具有减小的输入电容的多沟道高电子迁移率晶体管的制作方法

- 国知局

- 2024-09-14 14:29:28

本公开涉及半导体装置的领域,并且具体地涉及具有减小的输入电容的多沟道高电子迁移率晶体管。

背景技术:

1、hemt(高电子迁移率场效应晶体管)也被称为异质结构fet(hfet)以及调制掺杂fet(modfet)与许多传统半导体晶体管设计相比提供高导电和低损耗。这些有益的导电特性使hemt在应用中是期望的,所述应用包括但不限于例如在电源和功率转换器、电动汽车、空调器中并且在消费电子装置中用作开关。设计者不断地寻求用于改进hemt的性能(例如,功耗和电压阻断能力)的方式。设计者寻求改进的示例性装置参数包括漏电流、阈值电压(vth)、漏极源极接通状态电阻(rdson)和最大电压切换能力(举几个例子)。使用超过一个装置沟道的多沟道hemt当前正在研究中。通过在装置的源极和漏极之间包括多个并联的导电路径,这个装置概念有益地降低装置的接通电阻。当前多沟道hemt设计涉及在漏极源极接通状态电阻(rdson)和输入电容之间进行不想要的折衷。

技术实现思路

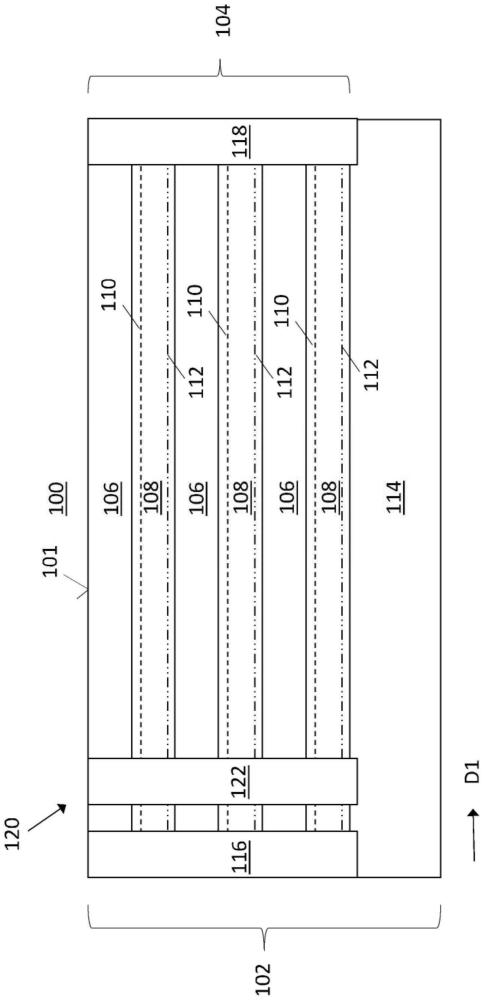

1、公开了一种高电子迁移率晶体管。根据实施例,所述高电子迁移率晶体管包括:半导体主体,包括堆叠在彼此的顶部上的多个iii型氮化物半导体层,由此形成多个二维第一电荷类型气体沟道和至少一个二维第二电荷类型气体沟道,所述二维第二电荷类型气体沟道沿垂直方向位于两个二维第一电荷类型气体沟道之间;源电极和漏电极,沿侧向彼此分隔开,并且与所述多个二维第一电荷类型气体沟道处于欧姆接触;栅极结构,被配置为通过控制所述多个二维第一电荷类型气体沟道的导电状态来控制所述源电极和漏电极之间的导电连接;和电荷耗散结构,被配置为在所述高电子迁移率晶体管的断开状态期间从所述二维第二电荷类型气体沟道去除第二电荷类型载流子。

2、公开了一种形成高电子迁移率晶体管的方法。根据实施例,所述方法包括:提供半导体主体,所述半导体主体包括堆叠在彼此的顶部上的多个iii型氮化物半导体层,由此形成多个二维第一电荷类型气体沟道和至少一个二维第二电荷类型气体沟道,所述二维第二电荷类型气体沟道沿垂直方向位于两个二维第一电荷类型气体沟道之间;形成源电极和漏电极,所述源电极和漏电极沿侧向彼此分隔开,并且与所述多个二维第一电荷类型气体沟道处于欧姆接触;形成栅极结构,所述栅极结构被配置为通过控制所述多个二维第一电荷类型气体沟道的导电状态来控制所述源电极和漏电极之间的导电连接;并且形成电荷耗散结构,所述电荷耗散结构被配置为在所述高电子迁移率晶体管的断开状态期间从所述二维第二电荷类型气体沟道去除第二电荷类型载流子。

技术特征:1.一种高电子迁移率晶体管,包括:

2.如权利要求1所述的高电子迁移率晶体管,其中所述电荷耗散结构包括第二导电型半导体材料的一个或多个区,所述一个或多个区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

3.如权利要求2所述的高电子迁移率晶体管,其中所述电荷耗散结构和所述源电极被连接到相同电势。

4.如权利要求2所述的高电子迁移率晶体管,其中所述栅极结构包括多个栅极柱,并且其中每个栅极柱是第二导电型半导体材料区,该区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

5.如权利要求4所述的高电子迁移率晶体管,还包括:势垒结构,沿侧向位于所述栅极结构和所述高电子迁移率晶体管的访问区之间,其中所述势垒结构形成能量势垒,所述能量势垒防止第二电荷类型载流子在所述高电子迁移率晶体管的所述访问区和所述栅极结构之间流动。

6.如权利要求5所述的高电子迁移率晶体管,其中所述势垒结构是第一导电型半导体材料区,该区延伸通过所述多个iii型氮化物半导体层并且将所述高电子迁移率晶体管的所述访问区与所述栅极结构分离。

7.如权利要求5所述的高电子迁移率晶体管,其中所述电荷耗散结构被安放在所述访问区内。

8.如权利要求5所述的高电子迁移率晶体管,其中所述电荷耗散结构包括多个电荷耗散柱,其中每个电荷耗散柱是第二导电型半导体材料区,该区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

9.如权利要求8所述的高电子迁移率晶体管,其中针对至少一个下面的参数,所述电荷耗散柱和所述栅极柱彼此不同:

10.如权利要求9所述的高电子迁移率晶体管,其中所述电荷耗散柱和所述栅极柱的所述参数使得所述栅极柱之间的所述多个二维第一电荷类型气体沟道在零栅极-源极电压被完全耗尽并且所述电荷耗散柱之间的所述多个二维第一电荷类型气体沟道在零栅极-源极电压被填充。

11.如权利要求2所述的高电子迁移率晶体管,其中所述栅极结构包括栅电极和位于所述至少一个二维第二电荷类型气体沟道和所述栅电极之间的电绝缘材料或schottky势垒。

12.如权利要求11所述的高电子迁移率晶体管,其中所述电荷耗散结构至少部分地与所述源电极重叠。

13.如权利要求12所述的高电子迁移率晶体管,其中来自所述电荷耗散结构的第二导电型半导体材料的所述一个或多个区延伸经过所述栅极结构并且朝着所述漏电极延伸。

14.一种形成高电子迁移率晶体管的方法,所述方法包括:

15.如权利要求14所述的方法,其中形成所述电荷耗散结构包括形成第二导电型半导体材料的一个或多个区,所述一个或多个区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

16.如权利要求15所述的方法,其中所述栅极结构包括多个栅极柱,并且其中每个栅极柱是第二导电型半导体材料区,该区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

17.如权利要求16所述的方法,其中所述方法还包括:形成势垒结构,所述势垒结构沿侧向位于所述栅极结构和所述高电子迁移率晶体管的访问区之间,其中所述势垒结构形成能量势垒,所述能量势垒防止第二电荷类型载流子在所述高电子迁移率晶体管的所述访问区和所述栅极结构之间流动。

18.如权利要求17所述的方法,其中所述电荷耗散结构被安放在所述访问区内,其中所述电荷耗散结构包括多个电荷耗散柱,并且其中每个电荷耗散柱是第二导电型半导体材料区,该区延伸通过所述多个iii型氮化物半导体层并且直接与所述至少一个二维第二电荷类型气体沟道交界。

19.如权利要求18所述的方法,其中形成所述电荷耗散结构包括将所述电荷耗散结构配置为仅在所述高电子迁移率晶体管通过所述栅极结构而被断开之后完全耗尽所述多个电荷耗散柱之间的所述多个二维第一电荷类型气体沟道。

20.如权利要求17所述的方法,其中形成所述势垒结构包括形成具有最小沟槽宽度的沟槽并且利用掺杂的第一导电型半导体材料填充所述沟槽以形成耗尽区,所述耗尽区阻止所述第二电荷类型载流子在所述高电子迁移率晶体管的所述访问区和所述栅极结构之间流动。

技术总结本公开涉及具有减小的输入电容的多沟道高电子迁移率晶体管。高电子迁移率晶体管包括:半导体主体,包括堆叠在彼此的顶部上的多个III型氮化物半导体层,由此形成多个二维第一电荷类型气体沟道和至少一个二维第二电荷类型气体沟道,所述二维第二电荷类型气体沟道沿垂直方向位于两个二维第一电荷类型气体沟道之间;源电极和漏电极,沿侧向彼此分隔开,并且与所述多个二维第一电荷类型气体沟道处于欧姆接触;栅极结构,被配置为通过控制所述多个二维第一电荷类型气体沟道的导电状态来控制所述源电极和漏电极之间的导电连接;和电荷耗散结构,被配置为在所述高电子迁移率晶体管的断开状态期间从所述二维第二电荷类型气体沟道去除第二电荷类型载流子。技术研发人员:C·奥斯特迈尔受保护的技术使用者:英飞凌科技奥地利有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/294345.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。