多芯片集成布局设计方法与流程

- 国知局

- 2024-10-09 16:08:48

本技术涉及芯片设计,具体而言,涉及一种多芯片集成布局设计方法。

背景技术:

1、在集成电路的发展过程中,电子设计自动化(electronic design automation,eda)技术也逐渐成熟,其应用范围也逐渐增大。在集成电路物理设计阶段,布局布线等是一个重要且耗时的步骤。首先,布局过程中涉及大量的迭代和优化,所需时间会显著地影响集成电路设计周期。其次 ,在集成电路的物理设计中,各个步骤间存在着密切联系,布局的结果会影响可布线性以及布线过程的运行时间、拥挤度和布通率等参数。

2、近年来,除了以线长和时延为驱动外,以可布线性为驱动的布局算法也受到关注。尽管在过去的几十年中布局算法有了显著的进步,但是快速且高效的布局仍然是一个具有挑战性的问题。特别是对于多芯片集成布局的应用场景,布局设计的方案具有更高的复杂性,在形成初始的方案之后,一般会通过人工进行不断的优化调整,以克服存在的各种问题。如此,就容易出现多芯片集成布局设计的效率低、成本高的问题。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种多芯片集成布局设计方法,以改善现有技术中存在的多芯片集成布局设计的效率低、成本高的问题。

2、为实现上述目的,本技术采用如下技术方案:

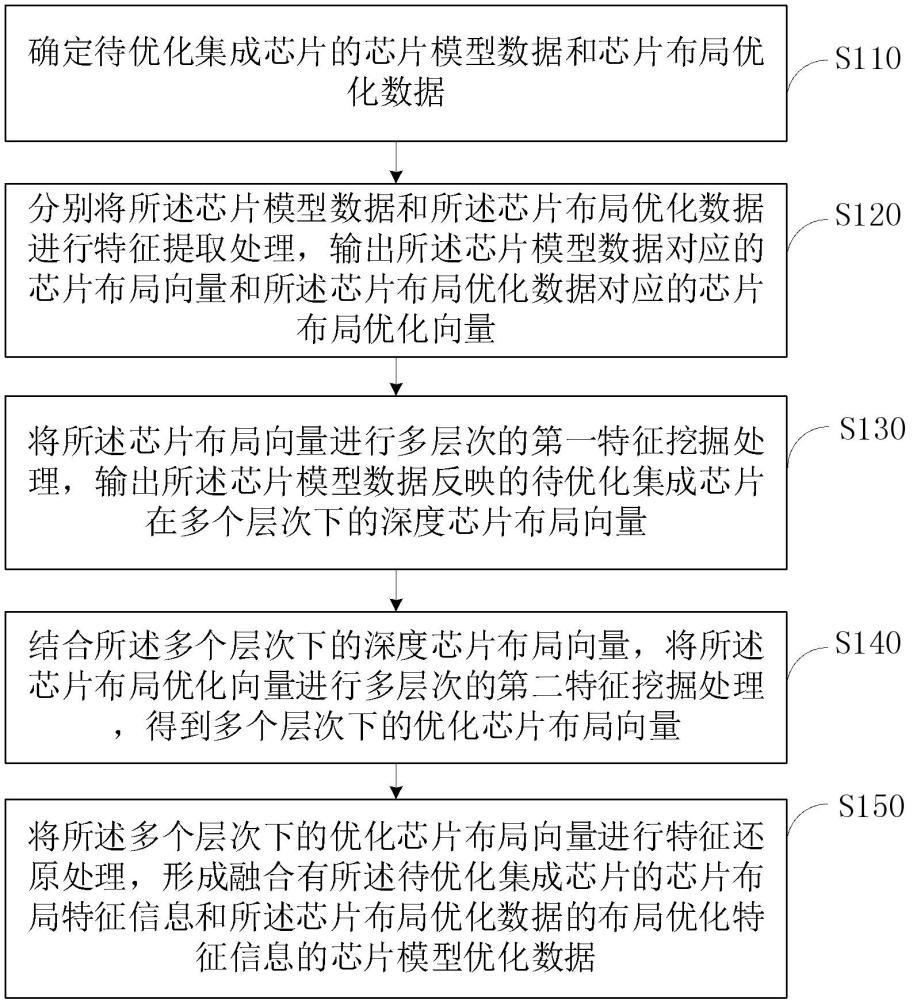

3、一种多芯片集成布局设计方法,包括:

4、确定出待优化集成芯片的芯片模型数据和芯片布局优化数据,其中,所述待优化集成芯片属于将多个子芯片和/或多个器件堆叠在基板的正面和背面的多个腔体的集成芯片,所述芯片模型数据基于对所述待优化集成芯片进行三维建模以形成,所述芯片布局优化数据基于对所述芯片模型数据进行模拟仿真以形成,所述芯片布局优化数据用于反映所述待优化集成芯片存在的性能问题,该性能问题包括与气密性相关的问题、与芯片体积相关的问题、与结构稳定性相关的问题、与散热相关的问题中的至少一个;

5、分别将所述芯片模型数据和所述芯片布局优化数据进行特征提取处理,输出所述芯片模型数据对应的芯片布局向量和所述芯片布局优化数据对应的芯片布局优化向量;

6、将所述芯片布局向量进行多层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在多个层次下的深度芯片布局向量;

7、结合所述多个层次下的深度芯片布局向量,将所述芯片布局优化向量进行多层次的第二特征挖掘处理,得到多个层次下的优化芯片布局向量,其中,所述优化芯片布局向量用于反映所述待优化集成芯片在所述芯片模型数据和所述芯片布局优化数据两个维度的特征信息;

8、将所述多个层次下的优化芯片布局向量进行特征还原处理,形成融合有所述待优化集成芯片的芯片布局特征信息和所述芯片布局优化数据的布局优化特征信息的芯片模型优化数据,其中,所述芯片模型优化数据用于反映优化后的集成芯片的布局情况。

9、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述将所述芯片布局向量进行多层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在多个层次下的深度芯片布局向量的步骤,包括:

10、利用经过优化操作形成的深度特征挖掘模型中的多个中间特征输出单元,将所述芯片布局向量进行多层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在多个层次下的深度芯片布局向量;

11、其中,针对将所述芯片布局向量进行的第一个层次的第一特征挖掘处理,利用所述多个中间特征输出单元中的第一个中间特征输出单元,将所述芯片布局向量进行第一个层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在第一个层次的深度芯片布局向量;

12、并且,针对将所述芯片布局向量进行的第a个层次的第一特征挖掘处理,利用所述多个中间特征输出单元中的第a个中间特征输出单元,将第b个层次的深度芯片布局向量进行第a个层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在第a个层次的深度芯片布局向量,a-b=1,且a大于1、b为大于或等于1。

13、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述中间特征输出单元为第一梯度优化单元,所述第一梯度优化单元中包括梯度优化关系;

14、所述利用经过优化操作形成的深度特征挖掘模型中的多个中间特征输出单元,将所述芯片布局向量进行多层次的第一特征挖掘处理,输出所述芯片模型数据反映的待优化集成芯片在多个层次下的深度芯片布局向量的步骤,包括:

15、利用所述多个中间特征输出单元中的每一个第一梯度优化单元中的梯度优化关系,将所述芯片布局向量进行关系映射处理,以实现多层次的第一特征挖掘处理,从而输出所述芯片模型数据反映的待优化集成芯片在多个层次下的深度芯片布局向量;

16、其中,每一个所述第一梯度优化单元包括多个卷积子单元,对于任意一个所述第一梯度优化单元,该第一梯度优化单元的输入向量在经过包括的多个卷积子单元的卷积处理之后,会将得到的卷积向量与该输入向量进行向量聚合处理,并将向量聚合处理的结果作为该第一梯度优化单元的输出向量。

17、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述结合所述多个层次下的深度芯片布局向量,将所述芯片布局优化向量进行多层次的第二特征挖掘处理,得到多个层次下的优化芯片布局向量的步骤,包括:

18、利用经过优化操作形成的优化特征挖掘模型,结合所述多个层次下的深度芯片布局向量,将所述芯片布局优化向量进行多层次的第二特征挖掘处理,得到多个层次下的优化芯片布局向量;

19、其中,所述优化特征挖掘模型包括级联连接的多个第二梯度优化单元,对于邻接的每两个第二梯度优化单元,该两个第二梯度优化单元之间配置有一个聚焦特征挖掘单元,使得前一个第二梯度优化单元的输出向量在经过该聚焦特征挖掘单元的处理之后,再输出到后一个第二梯度优化单元中进行相应的处理,所述第二梯度优化单元的数目与所述深度特征挖掘模型中的第一梯度优化单元的数目一样。

20、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述利用经过优化操作形成的优化特征挖掘模型,结合所述多个层次下的深度芯片布局向量,将所述芯片布局优化向量进行多层次的第二特征挖掘处理,得到多个层次下的优化芯片布局向量的步骤,包括:

21、针对将所述芯片布局优化向量进行的第一个层次的第二特征挖掘处理,利用所述多个第二梯度优化单元中的第一个第二梯度优化单元,将所述芯片布局优化向量进行第一个层次的第二特征挖掘处理,输出所述芯片布局优化数据在第一个层次的第二特征挖掘处理后的第一个层次的中间芯片布局优化向量;

22、在将所述芯片布局优化向量进行第c个层次的第二特征挖掘处理后,利用所述优化特征挖掘模型中的第c个聚焦特征挖掘单元,将所述第c个层次的第二特征挖掘处理后的第c个层次的中间芯片布局优化向量和所述深度特征挖掘模型中的第c个第一梯度优化单元输出的深度芯片布局向量进行向量聚合处理,输出对应的第c个芯片布局聚合向量,其中,c大于或等于1;

23、在将所述芯片布局优化向量进行第d个层次的第二特征挖掘处理的过程中,利用所述多个第二梯度优化单元中的第d个第二梯度优化单元,将所述芯片布局优化向量和第e个聚焦特征挖掘单元输出的第e个芯片布局聚合向量进行第d个层次的第二特征挖掘处理,输出所述芯片布局优化数据在第d个层次的第二特征挖掘处理后的第d个层次的中间芯片布局优化向量,其中,d大于1,d-e=1;

24、在进行最后一个层次的第二特征挖掘处理之后,将输出的多个层次的中间芯片布局优化向量作为所述多个层次下的优化芯片布局向量。

25、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,在所述针对将所述芯片布局优化向量进行的第一个层次的第二特征挖掘处理,利用所述多个第二梯度优化单元中的第一个第二梯度优化单元,将所述芯片布局优化向量进行第一个层次的第二特征挖掘处理,输出所述芯片布局优化数据在第一个层次的第二特征挖掘处理后的第一个层次的中间芯片布局优化向量的步骤以前,所述多芯片集成布局设计方法还包括:

26、利用预先确定的随机向量确定规则,输出所述优化特征挖掘模型对应的随机语义向量;

27、对所述随机语义向量和所述芯片布局优化向量进行标记,以标记为待处理向量,并加载到所述优化特征挖掘模型中;

28、所述针对将所述芯片布局优化向量进行的第一个层次的第二特征挖掘处理,利用所述多个第二梯度优化单元中的第一个第二梯度优化单元,将所述芯片布局优化向量进行第一个层次的第二特征挖掘处理,输出所述芯片布局优化数据在第一个层次的第二特征挖掘处理后的第一个层次的中间芯片布局优化向量的步骤,包括:

29、针对将所述芯片布局优化向量进行的第一个层次的第二特征挖掘处理,利用所述多个第二梯度优化单元中的第一个第二梯度优化单元,将所述芯片布局优化向量和所述随机语义向量进行第一个层次的第二特征挖掘处理,输出所述芯片布局优化数据在第一个层次的第二特征挖掘处理后的第一个层次的中间芯片布局优化向量。

30、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述多芯片集成布局设计方法基于经过网络优化操作形成的芯片布局优化网络实现,所述芯片布局优化网络包括第一网络部分和第二网络部分,所述第一网络部分包括第一特征提取模型和优化特征挖掘模型,所述第二网络部分包括第二特征提取模型和深度特征挖掘模型;

31、经过网络优化操作形成所述芯片布局优化网络的步骤,包括:

32、对训练芯片布局数据组合中的训练芯片模型数据进行加载,以加载到所述第二网络部分中,利用所述第二网络部分中的第二特征提取模型,将所述训练芯片模型数据进行特征提取处理,输出训练芯片布局向量;

33、利用所述第二网络部分中的深度特征挖掘模型,将所述训练芯片布局向量进行多层次的第一特征挖掘处理,输出所述训练芯片模型数据反映的训练待优化集成芯片在多个层次下的训练深度芯片布局向量;

34、对所述训练芯片布局数据组合中的训练芯片布局优化数据进行加载,以加载到所述第一网络部分中,利用所述第一网络部分中的第一特征提取模型,将所述训练芯片布局优化数据进行特征提取处理,输出训练芯片布局优化向量;

35、利用所述第一网络部分中的优化特征挖掘模型,结合所述多个层次下的训练深度芯片布局向量,将所述训练芯片布局优化向量进行多层次的第二特征挖掘处理,输出对应的多个层次下的训练优化芯片布局向量;

36、依据所述多个层次下的训练深度芯片布局向量和所述多个层次下的训练优化芯片布局向量,确定出所述芯片布局优化网络的网络优化误差;

37、依据所述网络优化误差,将所述芯片布局优化网络中的网络参数进行优化调整,输出网络优化操作后的芯片布局优化网络。

38、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述依据所述多个层次下的训练深度芯片布局向量和所述多个层次下的训练优化芯片布局向量,确定出所述芯片布局优化网络的网络优化误差的步骤,包括:

39、依据所述多个层次下的训练优化芯片布局向量和所述训练芯片模型数据,确定出所述芯片布局优化网络的第一网络优化误差;

40、依据所述多个层次下的训练深度芯片布局向量和所述多个层次下的训练优化芯片布局向量,确定所述芯片布局优化网络的第二网络优化误差;

41、融合所述第一网络优化误差和所述第二网络优化误差,输出所述芯片布局优化网络的网络优化误差。

42、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述依据所述多个层次下的训练优化芯片布局向量和所述训练芯片模型数据,确定出所述芯片布局优化网络的第一网络优化误差的步骤,包括:

43、将所述多个层次下的训练优化芯片布局向量进行特征还原处理,形成融合有所述训练待优化集成芯片的芯片布局特征信息和所述训练芯片布局优化数据的布局优化特征信息的训练芯片模型优化数据;

44、对所述训练芯片模型优化数据和所述训练芯片模型数据对应的参考芯片模型优化数据进行差异确定处理,输出所述芯片布局优化网络的第一网络优化误差,其中,所述参考芯片模型优化数据用于描述针对所述训练芯片模型数据反映的训练待优化集成芯片存在的性能问题进行优化后的集成芯片。

45、在本技术较佳的选择中,在上述多芯片集成布局设计方法中,所述依据所述多个层次下的训练深度芯片布局向量和所述多个层次下的训练优化芯片布局向量,确定所述芯片布局优化网络的第二网络优化误差的步骤,包括:

46、将所述多个层次下的训练深度芯片布局向量进行特征还原处理,形成对应的训练芯片模型还原数据;

47、将所述多个层次下的训练优化芯片布局向量进行特征还原处理,形成融合有所述训练待优化集成芯片的芯片布局特征信息和所述训练芯片布局优化数据的布局优化特征信息的训练芯片模型优化数据;

48、将所述训练芯片模型还原数据和所述训练芯片模型优化数据分别进行特征提取处理之后,对输出的向量进行差异确定处理,输出所述芯片布局优化网络的第二网络优化误差。

49、本技术提供的多芯片集成布局设计方法,首先,确定出芯片模型数据和芯片布局优化数据;其次,分别将芯片模型数据和芯片布局优化数据进行特征提取处理,输出芯片布局向量和芯片布局优化向量;然后,将芯片布局向量进行多层次的第一特征挖掘处理,输出多个层次下的深度芯片布局向量;进一步,结合多个层次下的深度芯片布局向量,将芯片布局优化向量进行多层次的第二特征挖掘处理,得到多个层次下的优化芯片布局向量;最后,将多个层次下的优化芯片布局向量进行特征还原处理,形成芯片模型优化数据。基于上述内容,由于会结合多个层次下的深度芯片布局向量将芯片布局优化向量进行多层次的第二特征挖掘处理,使得得到的多个层次下的优化芯片布局向量可以反映待优化集成芯片在芯片模型数据和芯片布局优化数据两个维度的特征信息,也就是说,既可以表征原始的芯片布局特征,也能反映需要优化的性能问题的特征,使得在进行优化芯片布局向量的特征还原处理时依据可以更可靠、充分,因此,还原出的芯片模型优化数据在保障与原始的芯片布局特征匹配的情况,也能实现性能问题的优化,而且在优化的过程中不需要进行人工的迭代等操作,使得可以改善现有技术中存在的多芯片集成布局设计的效率低、成本高的问题,即具有方案优化的可靠性、效率和成本兼顾的优势。

本文地址:https://www.jishuxx.com/zhuanli/20240929/311842.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表