一种多芯粒3D芯片的实现方法与流程

- 国知局

- 2024-08-22 14:48:48

本发明属于三维芯片设计,具体涉及一种多芯粒3d芯片的实现方法。

背景技术:

1、在过去的几十年里,随着集成电路技术的快速发展,摩尔定律已经逐渐接近其物理极限。为了继续推动半导体技术的发展,研究人员开始探索新的设计理念和制造技术。其中,三维集成电路和小芯片技术成为了热门的研究方向。

2、三维集成电路技术是通过将多个芯粒堆叠在一起,利用垂直空间来实现更高密度的集成,这种技术可以有效地提高芯片的性能,同时减少功耗和成本;小芯片技术是通过将一个大芯片分割成多个负责特定的功能小芯片,然后将这些小芯片组合在一起形成一个完整的大芯片,这种技术可以提高设计的灵活性和可扩展性,同时降低成本和提高生产效率。

3、遗憾的是,现有半导体领域缺乏将三维集成和小芯片进行结合的集成电路技术。

技术实现思路

1、为了解决上述背景技术中提到的至少一个问题,本发明提出了提出了一种多芯粒3d芯片的实现方法。

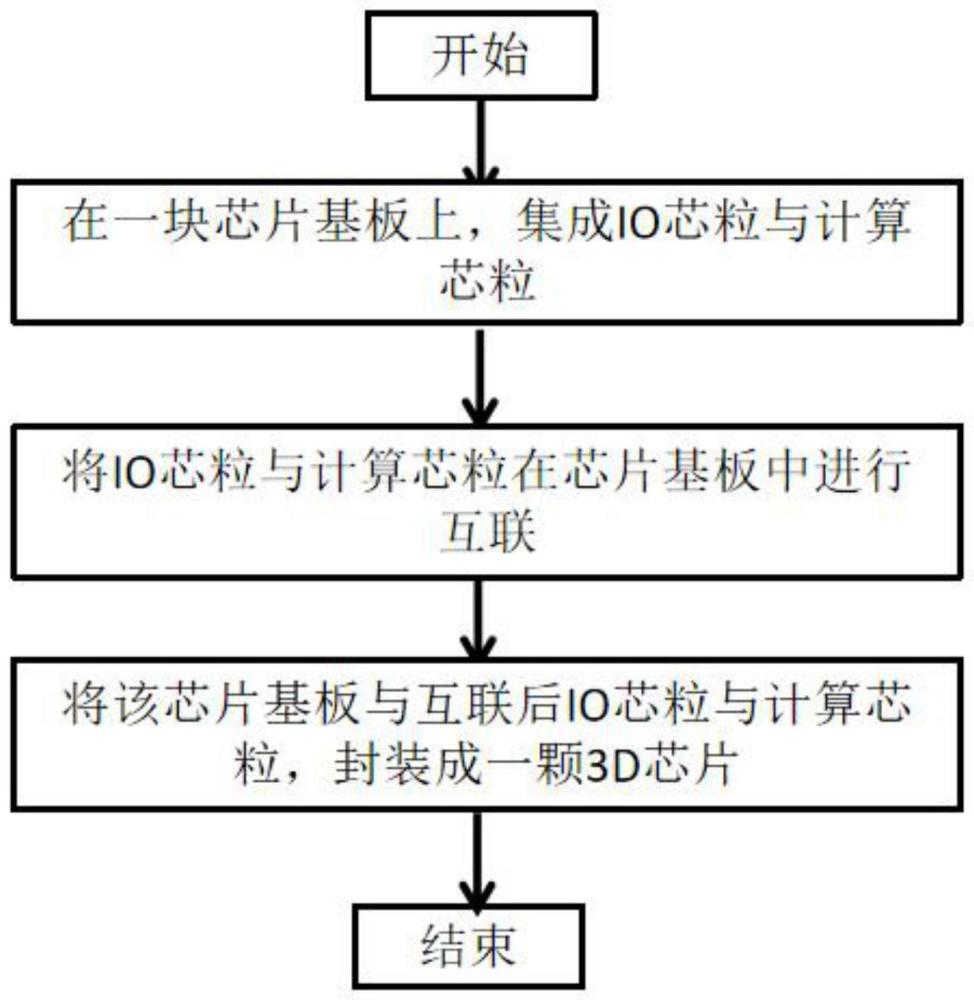

2、一种多芯粒3d芯片的实现方法,包括步骤:

3、步骤s1,在一块芯片基板上,集成io芯粒与计算芯粒;

4、其中,io芯粒包括用于芯粒与芯粒互联的d2d接口、用于连接其他高速或低速设备的pcie接口、ddr接口和serdes接口、用于音频视频编解码功能的计算模块、用于人工智能计算加速的计算模块和用于一般通用计算的计算模块;

5、计算芯粒是通过对计算单元和存储单元进行三维堆叠而得到,其中,计算单元包括可重构计算处理器、人工神经网络处理器和通用图形处理器;

6、存储单元包括dram存储器和sram存储器;

7、计算单元与存储单元满足关系:

8、kernel=1*a+α*b

9、α≥2

10、其中,kernel为计算芯粒,a为计算单元,b为存储单元,α为正整数系数;

11、当设定顶层金属所对应的一面的正面,硅衬底所对应的一面为背面时,则三维堆叠的堆叠方式包括:计算单元正面与存储单元背面键合实现互联、计算单元背面与存储单元正面键合实现互联;

12、当设定芯片基板垂直方向上,贴近芯片基板一侧为下,远离芯片基板一侧为上,则三维堆叠的堆叠结构包括:存储芯粒在上,计算芯粒在下、计算芯粒在上,存储芯粒在下;

13、步骤s2,将io芯粒与计算芯粒在芯片基板中进行互联;

14、具体地,io芯粒与计算芯粒满足关系:

15、chip=1*c+β*d

16、其中,chip为集成后的3d芯片,c为io芯粒,d为计算芯粒,β为io芯粒中d2d接口的数量;

17、三维集成电路技术是通过将多个芯粒堆叠在一起,利用垂直空间来实现更高密度的集成;小芯片技术是通过将一个大芯片分割成多个负责特定的功能小芯片,然后将这些小芯片组合在一起形成一个完整的大芯片;两种技术各有其优势,然而现有半导体领域缺乏将三维集成和小芯片进行结合的集成电路技术。

18、本发明提出了一种结合三维集成和小芯片的集成电路技术实现方法,按照本发明实现的集成电路,不仅可以有效地提高芯片的性能,减少芯片实际运行过程中的功耗,同时还能够提高芯片设计的灵活性和扩展性,降低芯片设计成本。

19、步骤s3,将该芯片基板与互联后io芯粒与计算芯粒,封装成一颗3d芯片。

20、本发明提出了,与现有的技术相比,具有以下有益效果:

21、本发明提出了一种结合三维集成和小芯片的集成电路技术实现方法,按照本发明实现的集成电路,不仅可以有效地提高芯片的性能,减少芯片实际运行过程中的功耗,同时还能够提高芯片设计的灵活性和扩展性,降低芯片设计成本。

技术特征:1.一种多芯粒3d芯片的实现方法,其特征在于,包括步骤:

2.根据权利要求1所述的一种多芯粒3d芯片的实现方法,其特征在于,步骤s1中所述的io芯粒,具体包括用于芯粒与芯粒互联的d2d接口、用于连接其他高速或低速设备的pcie接口、ddr接口和serdes接口、用于音频视频编解码功能的计算模块、用于人工智能计算加速的计算模块和用于一般通用计算的计算模块。

3.根据权利要求1所述的一种多芯粒3d芯片的实现方法,其特征在于,步骤s1中所述的计算芯粒,具体是通过对计算单元和存储单元进行三维堆叠而得到,其中,计算单元包括可重构计算处理器、人工神经网络处理器和通用图形处理器;存储单元包括dram存储器和sram存储器。

4.根据权利要求3所述的一种多芯粒3d芯片的实现方法,其特征在于,所述计算单元与存储单元满足关系:

5.根据权利要求3所述的一种多芯粒3d芯片的实现方法,其特征在于,所述对计算单元和存储单元进行三维堆叠,具体地,当设定顶层金属所对应的一面的正面,硅衬底所对应的一面为背面时,则三维堆叠的堆叠方式包括:计算单元正面与存储单元背面键合实现互联、计算单元背面与存储单元正面键合实现互联;

6.根据权利要求1所述的一种多芯粒3d芯片的实现方法,其特征在于,步骤s2中所述的io芯粒与计算芯粒,满足关系:

技术总结本发明属于三维芯片设计技术领域,具体公开了一种多芯粒3D芯片的实现方法。该方法提出了一种结合三维集成和小芯片的集成电路技术,按照该方法实现的集成电路,不仅可以有效地提高芯片的性能,减少芯片实际运行过程中的功耗,同时还能够提高芯片设计的灵活性和扩展性,降低芯片设计成本。技术研发人员:于义,阳祥秋,欧阳鹏受保护的技术使用者:北京清微智能科技有限公司技术研发日:技术公布日:2024/8/20本文地址:https://www.jishuxx.com/zhuanli/20240822/279981.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。