一种低功耗触发器

- 国知局

- 2024-10-21 14:38:21

本发明涉及触发器领域,特别是指一种低功耗触发器。

背景技术:

1、随着社会的不断发展,人们对于柔性产品的需求逐渐增加,薄膜晶体管(thinfilm transistor,tft)在柔性电路和柔性显示方面也发挥着越来越重要的作用。作为场效应晶体管的一种,薄膜晶体管的工作原理与传统的硅基mosfet器件类似,它不仅可以应用于面板显示器以及各种传感器领域,而且在生物医疗,可穿戴设备,柔性显示等方面都有广泛应用。相比于其它的氧化物半导体,铟镓锌氧化物(indium-gallium-zinc-oxide,igzo)具有更好的场效应迁移率、光学透明度和较好的均匀性,所以以igzo为代表的金属氧化物薄膜晶体管逐渐应用于更加复杂的电路系统。

2、但是,对于igzo tft来说,由于p型tft与n型tft之间载流子迁移率不匹配等因素的存在,在实际电路的应用中只能采用n型的单极型tft。实用p型tft的缺失使之在设计电路的过程中无法实现同一电路下的互补器件,这不仅加大了电路设计难度,也会导致电路静态功耗大大增加。

3、d触发器是时序逻辑电路中不可或缺的基本组成部分,虽然目前存在的基于tft的dff电路结构能实现相应的功能,但是仍然面临着功耗高,速度不足,成本较高等问题。

技术实现思路

1、本发明的主要目的在于克服现有技术中的上述缺陷,提出一种低功耗触发器,仅采用n型晶体管实现完全互补的锁存器结构,除信号必须的反相器之外,该电路在正常工作时不具有静态的电流通路,大大降低电路的功耗。

2、本发明采用如下技术方案:

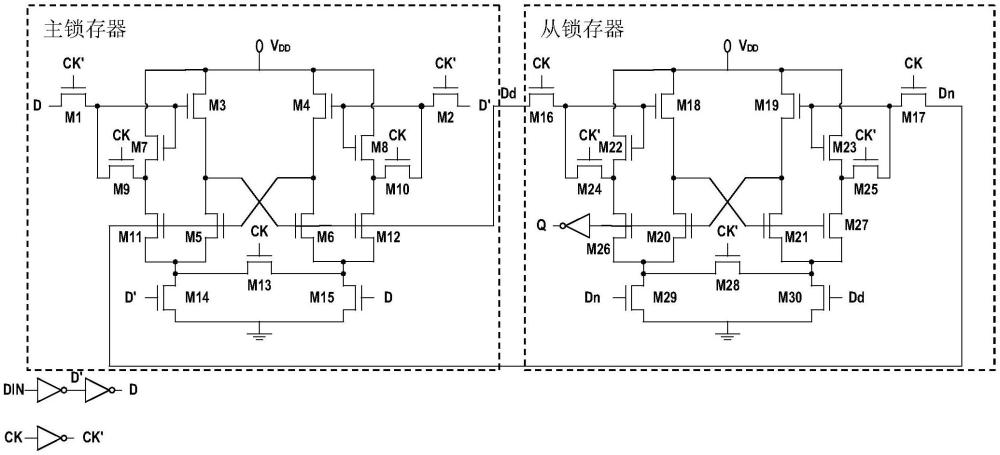

3、一种低功耗触发器,包括两锁存器和若干反相器,一所述锁存器作为主锁存器,另一锁存器作为从锁存器,所述反相器实现控制信号和输入数据的反相;所述主锁存器的两控制信号端之间连接有反相器,所述主锁存器的两数据输入端之间连接有反相器;所述从锁存器的数据输入端与所述主锁存器的数据输出端相连,所述从锁存器的两控制信号端之间连接有反相器;当输入的控制信号ck=0时,ck’=1,主锁存器进入数据输入阶段,从锁存器进入数据保持阶段;当输入的控制信号ck=1时,ck’=0,主锁存器进入数据保持阶段,从锁存器进入数据输入阶段。

4、所述锁存器包括数据输入单元和反馈单元;所述输入单元设置有第一控制信号端、第一数据输入端和第二数据输入端,用于根据控制信号将输入数据存储于第一节点,所述第一数据输入端和第二数据输入端之间连接有反相器;所述反馈单元与所述输入单元相连以将输入数据反馈至第二节点,所述反馈单元设置有第二控制信号端,所述第二控制信号端与所述第一控制信号端之间连接有反相器。

5、所述输入单元包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和第六晶体管;所述第一晶体管的栅极连接第一控制信号端,第一极连接第一数据输入端,第二极连接所述第三晶体管的栅极并作为一所述第二节点;所述第三晶体管的第一极连接vdd,所述第三晶体管的第二极作为一所述第一节点;所述第二晶体管的栅极连接第一控制信号端,第一极连接第二数据输入端,第二极连接所述第四晶体管的栅极并作为另一所述第二节点;所述第四晶体管的第一极连接vdd,所述第四晶体管的第二极作为另一所述第一节点;所述第五晶体管的栅极连接至所述第四晶体管的第二极也即另一所述第一节点;所述第五晶体管的第一极连接至所述反馈单元,所述第五晶体管的第二极连接至所述第三晶体管的第二极;所述第六晶体管的栅极连接至一所述第一节点,第一极连接至所述反馈单元,所述第六晶体管的第二极连接至所述第四晶体管的第二极。

6、在所述锁存器中,当第一控制信号端输入ck=1,第二控制信号端输入ck’=0时,所述第一晶体管和所述第二晶体管打开,所述输入数据通过所述第一晶体管和所述第二晶体管分别传入对应的所述第三晶体管和所述第四晶体管的栅极,所述反馈单元断开;当第一控制信号端输入ck=0,第二控制信号端输入ck’=1时,所述第一晶体管和所述第二晶体管关断,所述反馈单元接通。

7、所述反馈单元包括第七晶体管、第八晶体管、第九晶体管、第十晶体管、第十一晶体管和第十二晶体管;所述第七晶体管的栅极连接所述输入单元,第一极连接vdd;所述第九晶体管的栅极连接第二控制信号端,第一极连接至所述输入单元的一所述第二节点,第二极连接所述第七晶体管的第二极;所述第十一晶体管的栅极连接至另一所述第一节点,第一极连接至所述第九晶体管的第二极,第二极连至输入单元;所述第八晶体管的栅极连接所述输入单元,第一极连接vdd;所述第十晶体管的栅极连接第二控制信号端,第一极连接至所述输入单元的另一所述第二节点,第二极连接所述第八晶体管的第二极;所述第十二晶体管的栅极连接至一所述第一节点,第一极连接至所述第十晶体管的第二极,第二极连至输入单元。

8、还包括第十三晶体管、第十四晶体管和第十五晶体管;所述第十三晶体管的栅极连接所述第二控制信号端,第一极和第二极分别连接至输入单元;所述第十四晶体管的栅极连接所述第二数据输入端,所述第十五晶体管的栅极连接所述第一数据输入端,所述第十四晶体管和所述第十五晶体管的第一极分别连接所述第十三晶体管的第一极和第二极,所述第十四晶体管和所述十五晶体管的第二极分别接地。

9、所述输入单元和所述反馈单元采用的晶体管为n型tft晶体管、cmos晶体管或碳纳米管。

10、由上述对本发明的描述可知,与现有技术相比,本发明具有如下有益效果:

11、本发明提出了一种主从边沿触发器,通过使用交叉耦合型的电路结构实现在仅使用n型晶体管的情况下实现全互补的锁存器结构,电路除输入输出端所必须的反相器之外,在正常工作时,该锁存器没有静态的电流通路,极大降低电路的功耗,同时电路正反馈的工作方式也可以使电路的速度得到很大提升。

12、本发明的触发器,晶体管除了采用n型tft器件外,还可以采用其它晶体管实现,例如cmos晶体管,碳纳米管等。

技术特征:1.一种低功耗触发器,包括两锁存器和若干反相器,一所述锁存器作为主锁存器,另一锁存器作为从锁存器,所述反相器实现控制信号和输入数据的反相;其特征在于:所述主锁存器的两控制信号端之间连接有反相器,所述主锁存器的两数据输入端之间连接有反相器;所述从锁存器的数据输入端与所述主锁存器的数据输出端相连,所述从锁存器的两控制信号端之间连接有反相器;当输入的控制信号ck=0时,ck’=1,主锁存器进入数据输入阶段,从锁存器进入数据保持阶段;当输入的控制信号ck=1时,ck’=0,主锁存器进入数据保持阶段,从锁存器进入数据输入阶段。

2.如权利要求1所述的一种低功耗触发器,其特征在于:所述锁存器包括数据输入单元和反馈单元;所述输入单元设置有第一控制信号端、第一数据输入端和第二数据输入端,用于根据控制信号将输入数据存储于第一节点,所述第一数据输入端和第二数据输入端之间连接有反相器;所述反馈单元与所述输入单元相连以将输入数据反馈至第二节点,所述反馈单元设置有第二控制信号端,所述第二控制信号端与所述第一控制信号端之间连接有反相器。

3.如权利要求2所述的一种低功耗触发器,其特征在于:所述输入单元包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和第六晶体管;所述第一晶体管的栅极连接第一控制信号端,第一极连接第一数据输入端,第二极连接所述第三晶体管的栅极并作为一所述第二节点;所述第三晶体管的第一极连接vdd,所述第三晶体管的第二极作为一所述第一节点;所述第二晶体管的栅极连接第一控制信号端,第一极连接第二数据输入端,第二极连接所述第四晶体管的栅极并作为另一所述第二节点;所述第四晶体管的第一极连接vdd,所述第四晶体管的第二极作为另一所述第一节点;所述第五晶体管的栅极连接至所述第四晶体管的第二极也即另一所述第一节点;所述第五晶体管的第一极连接至所述反馈单元,所述第五晶体管的第二极连接至所述第三晶体管的第二极;所述第六晶体管的栅极连接至一所述第一节点,第一极连接至所述反馈单元,所述第六晶体管的第二极连接至所述第四晶体管的第二极。

4.如权利要求3所述的一种低功耗触发器,其特征在于:在所述锁存器中,当第一控制信号端输入ck=1,第二控制信号端输入ck’=0时,所述第一晶体管和所述第二晶体管打开,所述输入数据通过所述第一晶体管和所述第二晶体管分别传入对应的所述第三晶体管和所述第四晶体管的栅极,所述反馈单元断开;当第一控制信号端输入ck=0,第二控制信号端输入ck’=1时,所述第一晶体管和所述第二晶体管关断,所述反馈单元接通。

5.如权利要求2所述的一种低功耗触发器,其特征在于:所述反馈单元包括第七晶体管、第八晶体管、第九晶体管、第十晶体管、第十一晶体管和第十二晶体管;所述第七晶体管的栅极连接所述输入单元,第一极连接vdd;所述第九晶体管的栅极连接第二控制信号端,第一极连接至所述输入单元的一所述第二节点,第二极连接所述第七晶体管的第二极;所述第十一晶体管的栅极连接至另一所述第一节点,第一极连接至所述第九晶体管的第二极,第二极连至输入单元;所述第八晶体管的栅极连接所述输入单元,第一极连接vdd;所述第十晶体管的栅极连接第二控制信号端,第一极连接至所述输入单元的另一所述第二节点,第二极连接所述第八晶体管的第二极;所述第十二晶体管的栅极连接至一所述第一节点,第一极连接至所述第十晶体管的第二极,第二极连至输入单元。

6.如权利要求2所述的一种低功耗触发器,其特征在于:还包括第十三晶体管、第十四晶体管和第十五晶体管;所述第十三晶体管的栅极连接所述第二控制信号端,第一极和第二极分别连接至输入单元;所述第十四晶体管的栅极连接所述第二数据输入端,所述第十五晶体管的栅极连接所述第一数据输入端,所述第十四晶体管和所述第十五晶体管的第一极分别连接所述第十三晶体管的第一极和第二极,所述第十四晶体管和所述十五晶体管的第二极分别接地。

7.如权利要求3或5所述的一种低功耗触发器,其特征在于:所述输入单元和所述反馈单元采用的晶体管为n型tft晶体管、cmos晶体管或碳纳米管。

技术总结一种低功耗触发器,包括两锁存器和若干反相器;主锁存器的两控制信号端之间连接有反相器,主锁存器的两数据输入端之间连接有反相器;从锁存器的数据输入端与主锁存器的数据输出端相连,从锁存器的两控制信号端之间连接有反相器;当输入的控制信号CK=0时,CK’=1,主锁存器进入数据输入阶段,从锁存器进入数据保持阶段;当输入的控制信号CK=1时,CK’=0,主锁存器进入数据保持阶段,从锁存器进入数据输入阶段。本发明通过使用交叉耦合型的电路结构实现在仅使用N型晶体管的情况下实现全互补的锁存器结构,极大降低电路的功耗;且采用正反馈的工作方式,同时添加额外晶体管实现无数据竞争的目的,使得电路的速度得到很大提升。技术研发人员:焦海龙,李晓菲受保护的技术使用者:北京大学深圳研究生院技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/318796.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表