一种主板时序控制电路的制作方法

- 国知局

- 2024-12-26 16:04:36

本发明涉及电路设计,特别涉及一种主板时序控制电路。

背景技术:

1、主板中各模块启动所需的电压或电流不尽相同,因此上电时序控制显得尤为重要,一个合理且稳定的上电时序控制方案能够确保计算机在开机时各组件协同工作,有效避免硬件冲突或损坏等问题。然而,现有的时序控制电路虽能在接收到开机信号后,基于时钟信号的反馈及预设的上电顺序逐步为各模块提供上电信号,但无法在第一个模块上电后自动建立响应期并基于此对该模块的响应速度进行检测,无法在任一模块因环境温度影响其响应速度时,防止整个时序电路控制的模块因此而遭遇上电信号反馈时间不准确的问题,因此提出一种主板时序控制电路,能够在第一个模块上电后自动建立响应期,并对该模块的响应速度进行检测,在响应期内,若未能收到被检测模块的上电完成信号反馈,电路会自动对下一个模块的上电信号进行限制,确保所有模块都能按照预设顺序稳定启动,能够在任一模块因环境温度影响其响应速度时,对下一个模块进行上电限制的同时为被检测模块建立延时期,从而避免错误的报警、复位操作,以及上电信号反馈时间不准确的情况发生。

技术实现思路

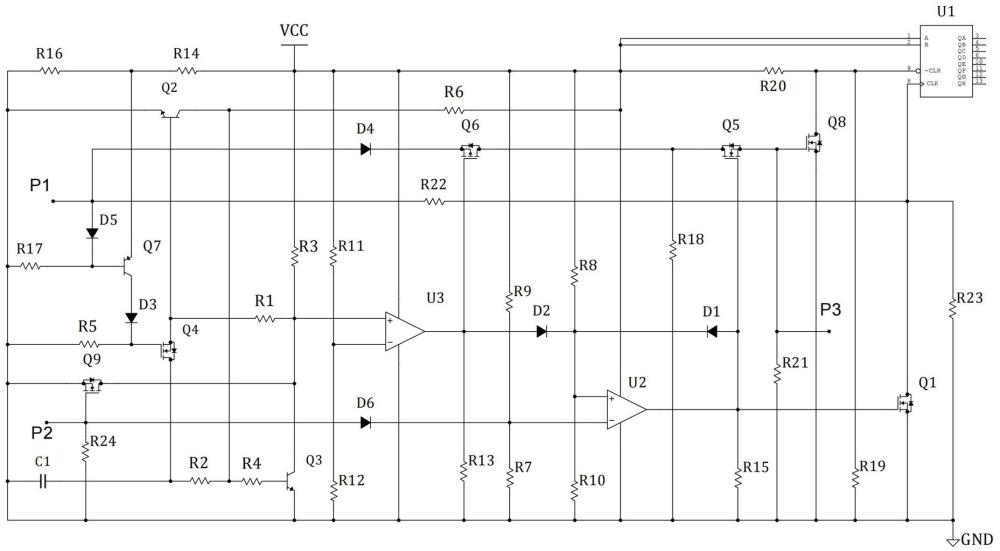

1、针对上述技术问题,本发明的目的是提供一种主板时序控制电路,所述控制电路包括反馈单元,反馈单元包括第一位移寄存器u1、第十九电阻r19、第二十电阻r20、第二十二电阻r22、第二十三电阻r23、第一连接器p1;

2、所述第一位移寄存器u1第一引脚、第一位移寄存器u1第二引脚、第二十电阻r20一端和电源连接,第一位移寄存器u1第九引脚和第十九电阻r19一端、第二十电阻r20另一端连接,第一位移寄存器u1第八引脚和第二十二电阻r22一端、第二十三电阻r23一端连接,第二十二电阻r22另一端和第一连接器p1端连接,第十九电阻r19另一端、第二十三电阻r23另一端和接地端连接。

3、进一步的,所述控制电路还包括转换单元,转换单元包括第二三极管q2、第三三极管q3、第四场效应管q4、第七三极管q7、第三二极管d3、第五二极管d5、第一电容c1、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第十四电阻r14、第十六电阻r16、第十七电阻r17;

4、所述第二三极管q2集电极和第二电阻r2一端、第四电阻r4一端、第六电阻r6一端连接,第二三极管q2基极和第一电阻r1一端、第四场效应管q4源极连接,第三三极管q3集电极和第一电阻r1另一端、第三电阻r3一端连接,第三三极管q3基极和第四电阻r4另一端连接,第四场效应管q4漏极和第一电容c1一端、第二电阻r2另一端连接,第四场效应管q4栅极和第三二极管d3阴极、第五电阻r5一端连接,第七三极管q7集电极和第三二极管d3阳极连接,第七三极管q7基极和第五二极管d5阴极、第十七电阻r17一端连接,第七三极管q7发射极和第十四电阻r14一端、第十六电阻r16一端连接,第五二极管d5阳极和第一连接器p1端连接,第三电阻r3另一端、第六电阻r6另一端、第十四电阻r14另一端和电源连接,第二三极管q2发射极、第三三极管q3发射极、第一电容c1另一端、第五电阻r5另一端、第十六电阻r16另一端、第十七电阻r17另一端和接地端连接。

5、进一步的,所述控制电路还包括限制单元,限制单元包括第二运算放大器u2、第三运算放大器u3、第一场效应管q1、第二二极管d2、第八电阻r8、第十电阻r10、第十一电阻r11、第十二电阻r12;

6、所述第二运算放大器u2同相端和第八电阻r8一端、第十电阻r10一端、第二二极管d2阴极连接,第二运算放大器u2输出端和第一场效应管q1栅极连接,第三运算放大器u3同相端和第三电阻r3一端连接,第三运算放大器u3反相端和第十一电阻r11一端、第十二电阻r12一端连接,第三运算放大器u3输出端和第二二极管d2阳极连接,第一场效应管q1漏极和第一位移寄存器u1第八引脚连接,第八电阻r8另一端、第十一电阻r11另一端和电源连接,第一场效应管q1源极、第十电阻r10另一端、第十二电阻r12另一端和接地端连接。

7、进一步的,所述控制电路还包括复位单元,复位单元包括第九场效应管q9、第六二极管d6、第七电阻r7、第九电阻r9、第二连接器p2;

8、所述第九场效应管q9栅极和第六二极管d6阳极、第二连接器p2端连接,第六二极管d6阴极和第七电阻r7一端、第九电阻r9一端、第二运算放大器u2反相端连接,第九电阻r9另一端和电源连接,第七电阻r7另一端、第九场效应管q9源极和接地端连接。

9、进一步的,所述控制电路还包括延时单元,延时单元包括第五场效应管q5、第六场效应管q6、第八场效应管q8、第一二极管d1、第四二极管d4、第十八电阻r18、第二十一电阻r21;

10、所述第五场效应管q5栅极和第一二极管d1阳极、第一场效应管q1栅极连接,第五场效应管q5源极和第八场效应管q8栅极、第二十一电阻r21一端、第三连接器p3端连接,第五场效应管q5漏极和第六场效应管q6漏极、第十八电阻r18一端连接,第六场效应管q6栅极和第三运算放大器u3输出端连接,第六场效应管q6源极和第四二极管d4阴极连接,第八场效应管q8漏极和第一位移寄存器u1第九引脚连接,第一二极管d1阴极和第二运算放大器u2同相端连接,第四二极管d4阳极和第一连接器p1端连接,第八场效应管q8源极、第十八电阻r18另一端、第二十一电阻r21另一端和接地端连接。

11、进一步的,所述控制电路还包括复位单元,复位单元还包括第二十四电阻r24;

12、所述第二十四电阻r24一端和第九场效应管q9栅极连接,第二十四电阻r24另一端和接地端连接。

13、进一步的,所述控制电路还包括延时单元,延时单元还包括第十三电阻r13、第十五电阻r15;

14、所述第十三电阻r13一端和第六场效应管q6栅极连接,第十五电阻r15一端和第五场效应管q5栅极连接,第十三电阻r13另一端、第十五电阻r15另一端和接地端连接。

15、本发明与现有技术相比的有益效果是:

16、本发明能够在第一个模块上电后自动建立响应期,对该模块的响应速度进行检测,在响应期内,如果未能收到被检测模块的上电完成信号反馈,电路会自动对下一个模块的上电信号进行限制,确保所有模块都能按照预设顺序稳定启动,能够在任一模块因环境温度因素影响其响应速度时,对下一个模块进行上电限制的同时为被检测模块建立延时期,从而避免错误的报警、复位操作,以及上电信号反馈时间不准确的情况发生。

技术特征:1.一种主板时序控制电路,其特征在于,所述控制电路包括反馈单元,反馈单元包括第一位移寄存器、第十九电阻、第二十电阻、第二十二电阻、第二十三电阻、第一连接器;

2.根据权利要求1所述的主板时序控制电路,其特征在于,所述控制电路还包括转换单元,转换单元包括第二三极管、第三三极管、第四场效应管、第七三极管、第三二极管、第五二极管、第一电容、第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第十四电阻、第十六电阻、第十七电阻;

3.根据权利要求2所述的主板时序控制电路,其特征在于,所述控制电路还包括限制单元,限制单元包括第二运算放大器、第三运算放大器、第一场效应管、第二二极管、第八电阻、第十电阻、第十一电阻、第十二电阻;

4.根据权利要求2所述的主板时序控制电路,其特征在于,所述控制电路还包括复位单元,复位单元包括第九场效应管、第六二极管、第七电阻、第九电阻、第二连接器;

5.根据权利要求3所述的主板时序控制电路,其特征在于,所述控制电路还包括延时单元,延时单元包括第五场效应管、第六场效应管、第八场效应管、第一二极管、第四二极管、第十八电阻、第二十一电阻;

6.根据权利要求4所述的主板时序控制电路,其特征在于,所述控制电路还包括复位单元,复位单元还包括第二十四电阻;

7.根据权利要求5所述的主板时序控制电路,其特征在于,所述控制电路还包括延时单元,延时单元还包括第十三电阻、第十五电阻;

技术总结本发明公开了一种主板时序控制电路,所述控制电路包括反馈单元,反馈单元包括第一位移寄存器、第十九电阻、第二十电阻、第二十二电阻、第二十三电阻、第一连接器;本发明能够在第一个模块上电后自动建立响应期,对该模块的响应速度进行检测,在响应期内,如果未能收到被检测模块的上电完成信号反馈,电路会自动对下一个模块的上电信号进行限制,确保所有模块都能按照预设顺序稳定启动,能够在任一模块因环境温度因素影响其响应速度时,对下一个模块进行上电限制的同时为被检测模块建立延时期,从而避免错误的报警、复位操作,以及上电信号反馈时间不准确的情况发生。技术研发人员:高嵩,段崇修受保护的技术使用者:四川酷赛科技有限公司技术研发日:技术公布日:2024/12/12本文地址:https://www.jishuxx.com/zhuanli/20241216/348032.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表