一种栅极驱动电路的制作方法

- 国知局

- 2024-06-21 13:43:34

本技术涉及显示面板的驱动,具体涉及一种栅极驱动电路。

背景技术:

1、阵列基板行驱动(gate driver on array,简称goa),也就是利用现有薄膜晶体管液晶显示器阵列制程将栅极(gate)行扫描驱动信号电路制作在阵列基板上,实现对栅极逐行扫描的驱动方式,从而可以省掉面板的栅极驱动电路部分,具有降低面板的生产成本和实现面板窄边框设计的优点,为多种显示器所使用。

2、因此,为了对像素进行外部补偿,goa电路需要提供稳定的写入控制信号wr[n]。目前goa电路为了尽量减少薄膜晶体管的数量以实现面板的窄边框设计,通常采用单q点控制方式,goa电路为了保证显示阶段第一节点q的高电位,与第n级级传信号cout[n]输出端连接的电容c1的电容值,是远大于与信号输出端连接的电容c2的电容值,这样,在随机侦测阶由于电容c1分压的作用,无法将q点耦合至更高,导致信号输出端输出的写入控制信号(wr[n])的峰值电压较低,无法完成正常侦测过程。

技术实现思路

1、为了解决或改善上述问题,本技术实施例提供一种栅极驱动电路。

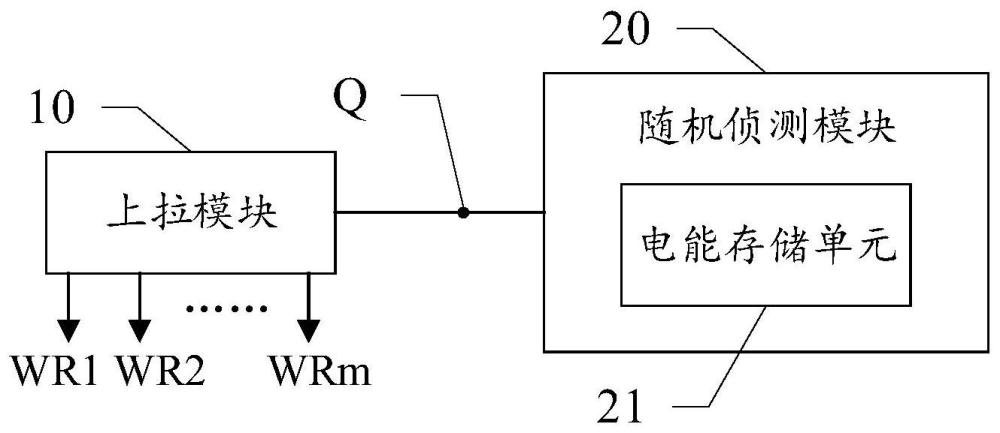

2、本技术实施例提供一种栅极驱动电路,包括多个级联的goa单元,其中,第n级goa单元包括上拉模块和随机侦测模块;

3、所述上拉模块与第一节点连接,用于输出多行写入控制信号;

4、所述随机侦测模块包括电能存储单元,所述随机侦测模块与所述第一节点连接,所述随机侦测模块用于在驱动周期接收到预设信号时,向所述电能存储单元进行充电,提升所述第一节点的电位以使得所选中的第m行写入控制信号保持稳定;其中,m和n为正整数。

5、在一些实施例中,所述电能存储单元包括第一电容,所述第一电容与所述第一节点连接,所述随机侦测模块的第一输入端与第一电源高电压连接,所述随机侦测模块的第一控制端与复位信号连接;

6、所述随机侦测模块用于在所述驱动周期的随机侦测阶段接收到所述复位信号时,向所述第一电容进行充电至所述第一电源高电压,提升所述第一节点的电位以使得所述第m行写入控制信号保持稳定。

7、在一些实施例中,所述电能存储单元还包括第二电容,所述随机侦测模块的输出端与第二节点连接,所述随机侦测模块的第二输入端与第二电源高电压连接,所述第二电源高电压小于所述第一电源高电压,所述随机侦测模块的第三输入端与上拉控制信号连接;

8、所述随机侦测模块还用于在所述驱动周期的选行阶段接收到所述上拉控制信号时,通过所述第二节点向所述第二电容进行充电至所述第二电源高电压,提升所述第一节点的电位以使得所述第m行写入控制信号保持稳定。

9、在一些实施例中,所述随机侦测模块还包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管和第六晶体管;

10、所述第一晶体管的栅极、所述第四晶体管的栅极和所述第六晶体管的栅极均为所述随机侦测模块的第一控制端;

11、所述第一晶体管的漏极与第三节点qb连接,所述第一晶体管的源极与所述第二晶体管的漏极连接,所述第二晶体管的源极与第三电源高电压连接;

12、所述第三晶体管的漏极与所述第二电容的一端连接,所述第二电容的另一端和所述第三晶体管的栅极与所述第二节点连接;

13、所述第三晶体管的源极和所述第四晶体管的漏极均与所述第五晶体管的栅极连接,所述第四晶体管的源极与所述第一节点连接;

14、所述第五晶体管的漏极为所述随机侦测模块的第一输入端,所述第五晶体管的源极与所述第六晶体管的漏极连接,所述第六晶体管的源极与所述第一电容的一端连接,所述第一电容的另一端与所述第一节点连接。

15、在一些实施例中,所述随机侦测模块还包括第七晶体管、第八晶体管和第九晶体管;

16、所述第七晶体管和所述第八晶体管共栅极,所述第七晶体管的漏极为所述随机侦测模块的第三输入端,所述第七晶体管的源极和所述第八晶体管的漏极均与所述第九晶体管的源极连接,所述第八晶体管的源极与所述第二节点连接;

17、所述第二电容的一端分别与所述第二节点和所述第三晶体管的栅极连接,所述第九晶体管的漏极为所述随机侦测模块的第二输入端,所述第二电容的另一端与所述第九晶体管的漏极连接。

18、在一些实施例中,所述随机侦测模块的第二控制端与随机侦测选行与复位信号连接,所述随机侦测模块用于在所述随机侦测阶段接收到的所述随机侦测选行与复位信号为高电平时,对所述第二节点进行放电的同时对所述第一电容进行放电。

19、在一些实施例中,所述随机侦测模块还包括第十晶体管,复用所述第七晶体管的栅极和所述第八晶体管的栅极为所述随机侦测模块的第二控制端,所述第十晶体管的源极与第一电源低电压连接,所述第十晶体管的栅极与全局复位信号连接,所述第十晶体管的漏极与所述第六晶体管的源极连接。

20、在一些实施例中,所述上拉模块包括第三电容、第十一晶体管、第十二晶体管、第十三晶体管、第十四晶体管和第十五晶体管;

21、所述第三电容的一端、所述第十一晶体管的栅极、所述第十二晶体管的栅极、所述第十三晶体管的栅极、所述第十四晶体管的栅极以及所述第十五晶体管的栅极均与所述第一节点连接;

22、所述第十一晶体管的漏极与第一时钟信号连接,所述第三电容的另一端与所述第十一晶体管的源极连接,所述第十一晶体管的源极用于输出第n级级传信号;

23、所述第十二晶体管的漏极与第二时钟信号连接,第十二晶体管的源极用于输出第m行写入控制信号;

24、所述第十三晶体管的漏极与第三时钟信号连接,所述第十三晶体管的源极用于输出第m+1行写入控制信号;

25、所述第十四晶体管的漏极与第四时钟信号连接,所述第十四晶体管用于输出第m+2行写入控制信号;

26、所述第十五晶体管的漏极与第五时钟信号连接,所述第十五晶体管的源极用于输出第m+3行写入控制信号。

27、在一些实施例中,所述第n级goa单元还包括上拉控制模块,所述上拉控制模块与所述随机侦测模块的输出端连接,用于拉高所述随机侦测模块的输出端的电位。

28、在一些实施例中,所述上拉控制模块包括第十六晶体管和第十七晶体管;

29、所述第十六晶体管的漏极与所述第二电源高电压连接,所述第十六晶体管的栅极和所述第十七晶体管的栅极均与所述上拉控制信号连接,所述第十六晶体管的源极与所述第十七晶体管的漏极连接,所述第十七晶体管的源极与所述第一节点连接。

30、本技术实施例提供的栅极驱动电路包括多个级联的goa单元,第n级goa单元包括上拉模块和随机侦测模块,随机侦测模块和上拉模块均与第一节点连接,上拉模块用于输出多行写入控制信号,随机侦测模块包括电能存储单元,所述随机侦测模块用于在驱动周期接收到预设信号时,向所述电能存储单元进行充电,通过电能存储单元耦合提升所述第一节点的电位以使得所选中的第m行写入控制信号保持稳定,使得第n级goa单元能正常输出第m行写入控制信号,由此保证显示面板正常显示。

本文地址:https://www.jishuxx.com/zhuanli/20240618/34206.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表