一种基于FPGA的低成本DSC信号产生装置及方法与流程

- 国知局

- 2024-06-21 14:09:42

本发明涉及液晶模组的显示和测试领域,具体为一种基于fpga的低成本dsc信号产生装置及方法。

背景技术:

1、lcd(liquid crystal display,液晶显示器)具有轻薄、耗电低、辐射小、屏幕无闪烁、色彩丰富等优点;液晶模组是lcd的关键组件,传统液晶模组内部的互联信号通常采用lvds(low-voltage differential signaling,低压差分信号传输)接口,但lvds接口只能支持较低的分辨率。为了满足对显示分辨率日益增长的需求,市场上出现了displayport接口。displayport接口不仅能够支持超高的分辨率和刷新率,而且能够直接驱动面板,具有更好的电磁兼容性与抗干扰性能,目前具有displayport接口的液晶模组已广泛应用于现代的平板电脑,笔记本电脑,桌面显示器等中大尺寸电子设备;随着现在生活水平的提高,人们对高分辨率和超高刷新率的追求也越来越高,特别是近年来随着电竞显示器的火爆,带动了超高分辨率和超高刷新率显示面板的发展,而目前即使是高达hbr3(high bit rate3,8.1gbps/lane)的速率也满足不了需求,在下一代基于displayport v2.1协议的uhbr10(ultra high bit rate 10,10gbps/lane),uhbr13.5(ultra high bit rate 13.5,13.5gbps/lane)和uhbr20(ultra high bit rate 20,20gbps/lane)模组产品没有商用之前,为了在不用物理升级至更高速率的传输带宽的基础上,dsc(display streamcompression)技术应运而生,dsc(display stream compression)技术的主要功能就是将视频图像数据经过压缩后再进行传输,达成低带宽就可输出超高分辨率和超高刷新率内容,并且经压缩后画面表现为视觉上无失真、低延迟的技术。dsc(display streamcompression)技术可运用在多个视频图像接口,包括displayport、hdmi、mipi等等,本文以displayport为主。

2、但是,现有的测试装置测试液晶模组时存下以下缺陷:

3、(1)目前市面上的基于fpga的displayport测试装置大多只符合displayportv1.2的协议标准,最高速率只支持到hbr2(high bit rate 2,5.4gbps/lane);而符合displayport v1.4a以及支持edp(embedded displayport)v1.4b协议标准的速率最高也仅为hbr3(high bit rate 3,8.1gbps/lane)的速率,在面对超高分辨率和超高刷新率的规格,比如4k 144hz及以上时就无法满足了;而dsc(display stream compression)技术通过将视频图像数据经过压缩后,将视频图像数据带宽压缩到原始视频图像数据的三分之一后再进行传输,这样就可以满足要求。

4、(2)在fpga上实现完整的实时性dsc(display stream compression)电路逻辑功能,需要fpga芯片内部的逻辑资源,dsp(数字信号处理)资源,存储器资源非常丰富,如此就需要购买昂贵的高性能fpga芯片,这样就大大提高了设备的成本。

技术实现思路

1、针对现有技术存在的不足,本发明提供了一种基于fpga的低成本dsc信号产生装置及方法,通过在现有装置的基础上能够输出经过vesa(video electronics standardsassociation)官方dsc(display stream compression)软件压缩后的视频图像数据,而不用在现有装置上实现完整的dsc实时压缩功能,从而让液晶模组生产商的产线上原有大批不带dsc(display stream compression)的测试装置能够利用起来对超大分辨率和超高刷新率的displayport液晶模组进行测试,大大降低了成本。

2、为实现上述目的,本发明提供如下技术方案:

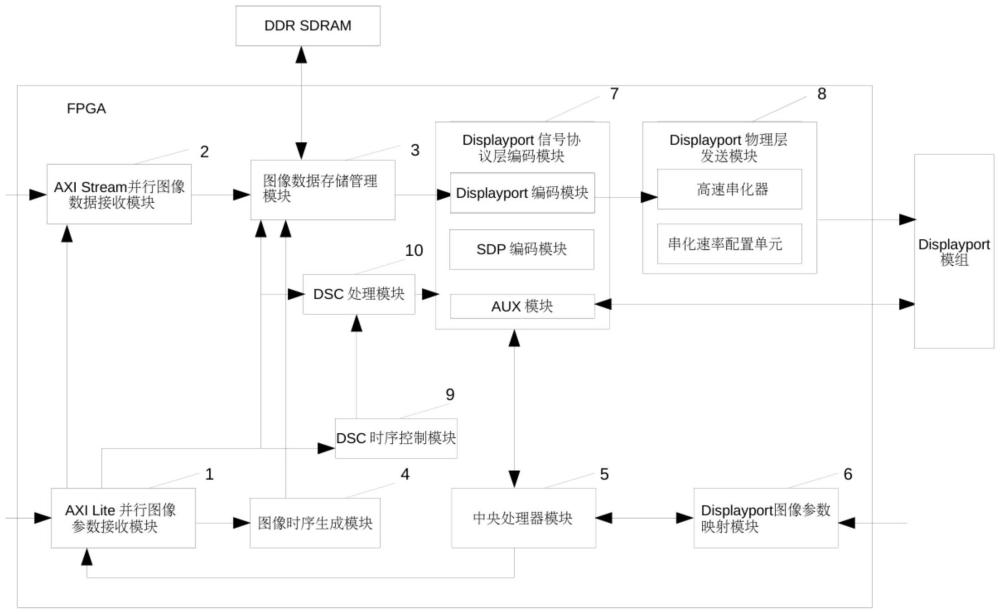

3、一种基于fpga的低成本dsc信号产生装置,包括axi stream并行数据接收模块,所述axi stream并行数据接收模块用于接收axi stream master总线上发送的正常图像数据或经过dsc压缩后图像数据,并转换成rgb格式的并行数据;图像数据存储管理模块,所述图像数据存储管理模块存储上述rgb格式的并行数据,并根据待测displayport模组所需的速率、通道,判断是否支持dsc信息将所述并行数据转化为与所述displayport模组信号速率匹配的displayport的串行信号。

4、作为本发明进一步的方案,还包括axi lite并行图像参数接收模块和图像时序生成模块,所述axi lite并行图像参数接收模块接收根据displayport模组的类型设置的寄存器配置参数,所述图像时序生成模块接收axi lite并行图像参数接收模块接收到的对应displayport模组压缩后的分辨率类型的寄存器生成压缩时序控制信号。

5、作为本发明进一步的方案,还包括dsc时序控制模块、dsc处理模块和displayport信号协议层编码模块,所述图像数据存储管理模块接收axi lite并行图像参数接收模块接收到的切图指令,根据图像时序生成模块输出的时序控制信号将图像对应编号的rgb数据从ddr sdram存储颗粒中取出来,并跟图像时序生成模块输出的时序控制信号一起送给dsc处理模块;所述dsc时序控制模块接收寄存器配置模块接收到的对应displayport模组真实分辨率类型的寄存器生成真实时序控制信号;所述dsc处理模块接收寄存器配置模块传送过来的压缩参数pps数据并缓存在ram,再送往displayport信号协议层编码模块。

6、作为本发明进一步的方案,还包括中央处理器模块,所述中央处理器模块控制displayport信号协议层编码模块中的aux通信接口跟模组通信得到待测模组的数据位宽、通道数、速率以及是否支持dsc压缩信。

7、作为本发明进一步的方案,还包括displayport物理层发送模块和displayport图像参数映射模块接,所述displayport物理层发送模块接收displayport信号协议层编码模块输出的数据,并根据displayport信号协议层编码模块中的aux通信接口得到的通道数及速率信息生成速率匹配的displayport串行信号,从而完成displayport模组显示图像画面测试;所述displayport图像参数映射模块接收axi lite并行图像参数接收模块接收到的图像参数寄存器并存储在映射区。

8、作为本发明进一步的方案,所述中央处理器模块接收displayport图像参数映射模块映射区的图像参数后控制displayport信号协议层编码模块中的aux模块进行displayport模组的vcom调节和edid烧录。

9、本发明还提供了一种基于fpga的低成本dsc信号产生方法,包括以下步骤:

10、通过aux接口跟displayport模组通信得到待测模组的通道数,速率信息以及是否支持dsc压缩模式,如果模组不支持dsc压缩模式则按照displayport协议对各通道正常图像数据进行像素数据排列、dummy数据填充,以及bs、be、fs、fe、sr标识符插入,最终得到正常图像像素数据流编码的并行数据流;如果模组支持dsc压缩模式则按照displayport协议对各通道压缩图像数据按照每个chunk逐字节进行排列,chunk dummy填充以及eoc标识符插入,然后再进行dummy数据填充,以及bs、be、fs、fe、sr标识符插入,以及dsc压缩模式插入ss、se标识符,并在它们之间插入pps类型的sdp数据流,最终得到dsc编码的并行数据流;

11、根据速率信息,通过displayport物理层发送模块的串化速率配置单元动态配置各通道的高速串化器内部锁相环的参考时钟、串化速率、使得高速串化器与待测模组所需的displayport信号速率匹配;

12、将各通道displayport编码的并行数据通过配置好的高速串化器编码模块,转换为对应速率的串行displayport信号。

13、本发明具有以下有益效果:

14、本发明可以实现在现有装置的基础上可以输出任意分辨率的压缩图像数据,并提供vcom调节、edid烧录等功能,所有功能都在一片fpga内实现,液晶模组测试装置集成度高,节约测试成本,提升测试效率和测试可靠度,提升企业的生产效率及产品合格率。

15、本发明可以实现通过aux接口跟模组通信得到待测模组的通道数,速率信息以及是否支持dsc压缩模式;如果模组不支持dsc压缩模式则按照displayport协议对各通道正常图像数据进行像素数据排列,dummy数据填充,以及bs(blanking start),be(blankingend),fs(fill start),fe(fill end),sr(scrambler reset)等标识符插入,最终得到正常图像像素数据流编码的并行数据流;如果模组支持dsc压缩模式则按照displayport协议对各通道压缩图像数据按照每个chunk逐字节进行排列,chunk dummy填充以及eoc(end ofchunk)标识符插入,然后再进行dummy数据填充,以及bs(blanking start),be(blankingend),fs(fill start),fe(fill end),sr(scrambler reset)等标识符插入,dsc压缩模式还需要插入ss(sdp start),se(sdp end)标识符,并在它们之间插入pps类型的sdp(secondary-data packet)数据流,最终得到dsc编码的并行数据流;以及根据速率信息,通过串化速率配置单元动态配置各通道的高速串化器内部锁相环的参考时钟、串化速率、使得高速串化器与待测模组所需的displayport信号速率匹配,串化速率最高可配置为hbr3(high bit rate 3,8.1gbps/lane)的速率;将各通道displayport编码的并行数据通过配置好的高速串化器编码模块,转换为对应速率的串行displayport信号。

16、为更清楚地阐述本发明的结构特征和功效,下面结合附图与具体实施例来对本发明进行详细说明。

本文地址:https://www.jishuxx.com/zhuanli/20240618/36355.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表