MEMS气体传感器的晶圆级三维封装方法及结构与流程

- 国知局

- 2024-07-27 12:43:52

mems气体传感器的晶圆级三维封装方法及结构技术领域1.本发明涉及mems技术领域,特别是涉及一种mems气体传感器的晶圆级三维封装方法及结构。背景技术:2.微机电系统(micro-electro-mechanical system,简称mems),也叫做微电子机械系统、微系统、微机械等,是集微传感器、微执行器、微机械结构、微电源、微能源、信号处理和控制电路、高性能电子集成器件、接口、通信等于一体的微型器件或系统。由于其微型化、智能化、多功能、高集成度和适于大批量生产等优点,使得其在电子、医学、工业、汽车和航空航天等国防和国民经济领域得到越来越广泛的应用。3.mems产品制造过程中,封装工艺既是重点,又是难点,封装成本占mems制造成本的50%以上。现有的mems封装工艺包括三维叠层封装和晶圆级封装工艺。三维叠层封装是把多个功能芯片依次层叠,并通过导电通孔或引线键合等实现互连而组装成三维封装结构,这种封装方式容易对功能芯片造成损伤,且封装出的器件体积偏大;晶圆级封装是在同一晶圆或不同的晶圆上制作外部功能芯片和mems器件,然后键合在一起形成硅封装,但现有技术中通常采用高温键合,容易导致器件受损,且封装后的器件存在散热不佳等问题,导致器件性能下降。技术实现要素:4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种mems气体传感器的晶圆级三维封装方法及结构,用于解决现有的mems封装技术导致封装出的器件体积偏大,封装过程中容易对芯片造成损伤,和/或封装完成的器件散热不佳,导致器件性能下降等问题。5.为实现上述目的及其他相关目的,本发明提供一种mems气体传感器的晶圆级三维封装方法,包括步骤:6.提供半导体基底,所述半导体基底内形成有asic芯片及多个间隔设置的硅通孔,所述硅通孔的一端显露于所述半导体基底的正面;7.对所述半导体基底进行背面减薄,以使所述硅通孔的另一端和所述半导体基底的背面相平齐,正面和背面为两个相对的表面;8.对所述半导体基底的背面进行刻蚀,以使所述硅通孔的表面突出于所述半导体基底的背面;9.于所述半导体基底的背面形成绝缘层;10.对半导体基底的背面进行化学机械抛光,露出所述硅通孔;11.进行光刻和干法刻蚀,以于所述半导体基底的背面形成空腔,所述空腔贯穿所述绝缘层,且延伸到所述半导体基底内,由此得到预键合结构;12.将形成有mems器件的mems微加热板和所述预键合结构进行共晶键合,所述半导体基底的背面和mems器件所在的面为键合面,所述mems器件正对所述空腔,所述硅通孔和mems微加热板的焊垫键合,所述绝缘层和mems微加热板的绝缘表面键合;13.于asic芯片正面硅通孔的表面形成硅通孔焊球;14.切割形成单颗mems气体传感器芯片。15.可选地,所述硅通孔包括铜柱和位于铜柱表面的铝层。16.可选地,对所述半导体基底进行背面减薄的工艺包括cmp。17.可选地,形成所述绝缘层的方法为:18.采用化学气相沉积工艺于所述半导体基底的背面和硅通孔的表面形成所述绝缘层;19.进行化学机械研磨以去除所述硅通孔表面的所述绝缘层,同时使得硅通孔表面和绝缘层的表面相平齐。20.可选地,所述半导体基底包括硅晶圆,所述绝缘层包括二氧化硅层。21.可选地,于所述半导体基底的背面形成空腔的方法包括:22.于所述绝缘层和硅通孔表面形成光刻胶层;23.对所述光刻胶层进行图形化处理以定义出空腔图形;24.依所述光刻胶层对所述绝缘层进行干法刻蚀,以于所述绝缘层中形成空腔的第一部分;25.对对应第一部分的半导体基底进行干法刻蚀,以形成所需深度的所述空腔。26.可选地,形成焊球后,还包括对得到的结构进行切割以分离为多个独立器件的步骤。27.可选地,所述mems微加热板自下而上包括硅基底、氧化硅层和氮化硅层,所述氮化硅层内形成有所述焊垫,所述mems器件形成于所述氧化硅层上,键合过程中,所述氮化硅层和半导体基底表面的绝缘层键合。28.可选地,所述焊垫包括粘结金属层和位于粘结金属层表面的焊料金属层,所述焊料金属层和硅通孔键合。29.更可选地,所述粘结金属层包括钛层和/或氮化钛层,所述焊料金属层包括铬层和/或金层。30.本发明还提供一种mems气体传感器的晶圆级三维封装结构,所述mems气体传感器的晶圆级三维封装结构包括相互键合的半导体基底和mems微加热板,所述半导体基底内形成有asic芯片、空腔及多个间隔设置的硅通孔,所述半导体基底表面形成有绝缘层,所述空腔贯穿所述绝缘层,且延伸到所述半导体基底内,所述硅通孔显露于所述绝缘层的表面,所述mems微加热板内形成有mems器件和焊垫,所述mems器件正对所述空腔,所述绝缘层和mems微加热板的绝缘表面键合,所述硅通孔和所述焊垫键合连接。31.如上所述,本发明提供的mems气体传感器的晶圆级三维封装方法及结构,具有以下有益效果:本发明采用硅通孔和背面露铜工艺的三维封装技术制备mems气体传感器,采用共晶键合的方法进行asic和mems微加热板的晶圆级键合封装,有助于提高键合性能和制造工艺效率。附图说明32.图1-10显示为本发明提供的mems气体传感器的晶圆级三维封装方法于制备mems气体传感器的晶圆级三维封装结构的各步骤中所呈现的例示性截面结构示意图。33.元件标号说明34.11半导体基底35.12铜柱36.13铝层37.14绝缘层38.15空腔39.161mems器件40.163硅基底41.164氧化硅层42.165氮化硅层43.166粘结金属层44.167焊料金属层具体实施方式45.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。如在详述本发明实施例时,为便于说明,表示器件结构的剖面图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本发明保护的范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。46.为了方便描述,此处可能使用诸如“之下”、“下方”、“低于”、“下面”、“上方”、“上”等的空间关系词语来描述附图中所示的一个元件或特征与其他元件或特征的关系。将理解到,这些空间关系词语意图包含使用中或操作中的器件的、除了附图中描绘的方向之外的其他方向。此外,当一层被称为在两层“之间”时,它可以是所述两层之间仅有的层,或者也可以存在一个或多个介于其间的层。47.在本技术的上下文中,所描述的第一特征在第二特征“之上”的结构可以包括第一和第二特征形成为直接接触的实施例,也可以包括另外的特征形成在第一和第二特征之间的实施例,这样第一和第二特征可能不是直接接触。48.需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。为使图示尽量简洁,各附图中并未对所有的结构全部标示。49.请参阅图1至图1050.如图1至图10所示,本发明提供一种mems气体传感器的晶圆级三维封装方法,包括步骤:51.提供半导体基底11,所述半导体基底11内形成有asic(applicationspecificintegrated circuit,应用型集成电路)芯片及多个间隔设置的硅通孔,所述硅通孔的一端显露于所述半导体基底11的正面,该步骤的结构如图1所示,该硅通孔可以通过深硅刻蚀工艺形成;所述半导体基底11例如为硅晶圆,但不限于此,还可以是锗晶圆,锗硅晶圆,soi晶圆等,在半导体基底11为200mm或300mm晶圆的情况下,asic芯片通常为多个,阵列分布于半导体基底11内,而硅通孔的数量与asic芯片的数量相匹配;52.采用包括但不限于化学机械研磨工艺,即cmp工艺(例如先粗磨再精磨)对所述半导体基底11进行背面减薄,以使所述硅通孔的另一端和所述半导体基底11的背面相平齐,正面和背面为两个相对的表面,也可以将硅通孔定义为包括相对的正面和背面,经研磨后,硅通孔的正面和半导体基底11的正面平齐,且背面和半导体基底11的背面平齐,该步骤后得到的结构如图2所示,背面指图2中的底面,而正面指图2中的顶面;53.对所述半导体基底11的背面进行刻蚀,例如对所述半导体基底11进行回刻,以使所述硅通孔的表面突出于所述半导体基底11的背面,即从图3可以看到,所述硅通孔的下表面低于半导体基底11的下表面;54.于所述半导体基底11的背面形成绝缘层14而使得硅通孔的背面仍然显露在外,该步骤后得到的结构如图5所示;该过程可以包括在形成绝缘层14后对半导体基底11的背面进行化学机械抛光,露出所述硅通孔的步骤;55.进行光刻和干法刻蚀,以于所述半导体基底11的背面形成空腔15,所述空腔15贯穿所述绝缘层14,且延伸到所述半导体基底11内,由此得到预键合结构,该过程可以参考图6至8所示;56.将形成有mems器件161的mems微加热板和所述预键合结构进行共晶键合(eutectic bonding),所述mems器件161正对所述空腔15,所述硅通孔和mems微加热板的电连接结构,即焊垫键合,所述绝缘层14和mems微加热板的绝缘表面键合,该步骤得到的结构如图9所示;57.采用包括但不限于植球工艺(ball mount)于显露的所述硅通孔的表面,即硅通孔的正面,即于asic芯片正面硅通孔的表面形成焊球17,得到的结构如图10所示;58.由于mems微加热板上通常形成有多个mems器件161,故而在形成焊球17后,还通常需要对得到的结构进行切割(die saw)以将晶圆上的多个器件各自分离而形成单颗mems气体传感器芯片。59.本发明提供的mems气体传感器的晶圆级三维封装方法先单独对形成有asic芯片的半导体基底进行预处理,之后再和形成有mems器件的mems微加热板共晶键合,可以最大程度减少封装过程中对芯片造成的损伤,且有助于提高封装效率;键合结构可以批量定制,有助于降低封装成本和器件小型化;利用共晶键合工艺具有的键合温度低、受表面粗糙度影响很小、适于批量的气密封装、物理特性良好、导热性好、强度高、无需助焊剂以及低黏滞性等优点,可以提高键合的一致性,避免沾污引起的界面空洞,有助于提高键合质量;mems器件置于空腔中,有助于改善器件散热,提高器件可靠性,且空腔可以用于气体导入,有助于提高封装器件的性能。同时,本发明采用硅通孔和背面露铜工艺的三维封装技术制备mems气体传感器,并结合共晶键合的方法进行asic和mems微加热板的晶圆级键合封装,有助于提高键合性能和制造工艺效率。60.在一示例中,所述mems微加热板自下而上(以图9和10为例)包括硅基底163、氧化硅层164和氮化硅层165,所述氮化硅层165内形成有所述焊垫,所述mems器件161形成于所述氧化硅层164上,且较佳的为与所述氮化硅层165具有间距,即mems器件161形成在一个由氮化硅层165包围成的空间内,键合过程中,所述氮化硅层165和半导体基底11表面的绝缘层14键合,且焊垫和硅通孔键合连接。当然,所述mems微加热板的结构并不仅限于此,重要的是与半导体基底11相匹配。在较佳的示例中,所述焊垫包括粘结金属层166和位于粘结金属层166表面的焊料金属层167,所述焊料金属层167和硅通孔键合,所述粘结金属层166包括但不限于钛层和/或氮化钛层,所述焊料金属层167包括但不限于铬层和/或金层,例如为铬金属层和金层的叠层,铬具有良好的硬度,而金具有良好的柔性和导电性,在共晶键合工艺中可以降低对表面平坦度的要求,提高键合品质。61.在一较佳的示例中,所述硅通孔包括铜柱12和位于铜柱12表面的铝层13,所述硅通孔可以通过硅通孔(tsv)工艺形成于所述半导体基底11内,例如先通过深硅刻蚀工艺于半导体基底11内形成通孔,然后于通孔内沉积金属形成所述硅通孔。铜柱12具有良好的导电性,而铝层13具有熔点低等优点,因而在后续的共晶键合工艺中容易软化而与所述mems微加热板的焊垫互熔结合,尤其是铜柱12和金的共晶键合速度较快。62.在一较佳的示例中,形成所述绝缘层14的方法为:63.采用化学气相沉积工艺于所述半导体基底11的背面和硅通孔的表面形成所述绝缘层14,在所述半导体基底11为硅晶圆时,所述绝缘层14较佳地为二氧化硅层,有助于减少层间应力,提高界面均匀性,该步骤得到的结构如图4所示;当然,所述绝缘层14也可以采用其他绝缘材料,例如氮氧化硅层等,但采用氧化硅层不仅有助于改善层间应力,同时还有助于简化后续的刻蚀工艺;64.进行化学机械研磨以去除所述硅通孔表面的所述绝缘层14,同时使得硅通孔表面和绝缘层14的表面相平齐,该步骤得到的结构如图5所示。通过该步骤,可以进一步提高界面平坦性,有助于提高后续键合质量。65.在一较佳的示例中,于所述半导体基底11的背面形成空腔15的方法包括:66.采用包括但不限于涂布工艺于所述绝缘层14和硅通孔表面形成光刻胶层18,所述光刻胶层18的厚度例如为3000μm-7000μm;67.对所述光刻胶层18进行图形化处理以定义出空腔15图形,该步骤得到的结构如图6所示;68.依所述光刻胶层18对所述绝缘层14进行干法刻蚀,以于所述绝缘层14中形成空腔15的第一部分,该步骤得到的结构如图7所示;69.对对应第一部分的半导体基底11进行干法刻蚀,以形成所需深度的所述空腔15,该步骤得到的结构如图8所示,所述空腔15在所述半导体基底11内的深度较佳地为所述半导体基底11厚度的1/4-3/4。70.在较佳的示例中,在进行共晶键合前,还可以先对所述预键合结构和mems微加热板进行清洁,例如采用氮气进行清洁,不仅能够有效去除无机与有机污染物,提高键合表面的清洁度,还能够显著改善键合面金属的表面性质,提高焊料的浸润性,减少界面空洞的形成,提高键合质量。71.本发明还提供一种mems气体传感器的晶圆级三维封装结构,所述mems气体传感器的晶圆级三维封装结构可以基于前述任一方案所述的封装方法制备而成,故前述内容可以全文引用至此。所述mems气体传感器的晶圆级三维封装结构如图10所示,包括相互键合的半导体基底11和mems微加热板,所述半导体基底11内形成有asic芯片、空腔15及多个间隔设置的硅通孔,所述半导体基底11表面形成有绝缘层14,所述空腔15贯穿所述绝缘层14,且延伸到所述半导体基底11内,所述硅通孔显露于所述绝缘层14的表面,所述mems微加热板内形成有mems器件161和焊垫,所述mems器件161正对所述空腔15,所述硅通孔和mems微加热板的电连接结构键合,如与由粘结金属层166和焊料金属层167构成的焊垫键合,所述绝缘层14和mems微加热板的绝缘表面键合。且进一步的示例中,所述焊垫包括粘结金属层和位于粘结金属层表面的焊料金属层,所述焊料金属层和硅通孔键合,所述粘结金属层包括钛层和/或氮化钛层,所述焊料金属层包括铬层和/或金层。72.对所述mems气体传感器的晶圆级三维封装结构的更多介绍还请参考前述内容,出于简洁的目的不赘述。由于采用前述方法封装而成,使得本发明提供的mems气体传感器的晶圆级三维封装结构具有键合质量高,散热性能好等优点。73.综上所述,本发明提供一种mems气体传感器的晶圆级三维封装方法及结构。该封装方法包括步骤:提供半导体基底,所述半导体基底内形成有asic芯片及多个间隔设置的硅通孔,所述硅通孔的一端显露于所述半导体基底的正面;对所述半导体基底进行背面减薄,以使所述硅通孔的另一端和所述半导体基底的背面相平齐,正面和背面为两个相对的表面;对所述半导体基底的背面进行刻蚀,以使所述硅通孔的表面突出于所述半导体基底的背面;于所述半导体基底的背面形成绝缘层;对半导体基底的背面进行化学机械抛光,露出所述硅通孔;进行光刻和干法刻蚀,以于所述半导体基底的背面形成空腔,所述空腔贯穿所述绝缘层,且延伸到所述半导体基底内,由此得到预键合结构;将形成有mems器件的mems微加热板和所述预键合结构进行共晶键合,所述半导体基底的背面和mems器件所在的面为键合面,所述mems器件正对所述空腔,所述硅通孔和mems微加热板的焊垫键合,所述绝缘层和mems微加热板的绝缘表面键合;于asic芯片正面硅通孔的表面形成硅通孔焊球;切割形成单颗mems气体传感器芯片。本发明采用硅通孔和背面露铜工艺的三维封装技术制备mems气体传感器,并结合共晶键合的方法进行asic和mems微加热板的晶圆级键合封装,有助于提高键合性能和制造工艺效率。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。74.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123276.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

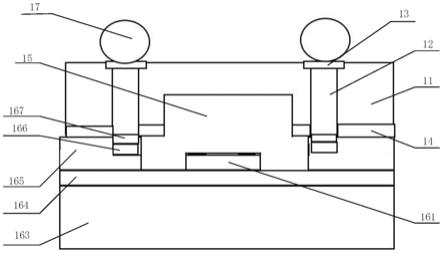

返回列表