一种MEMS器件及其制造方法与流程

- 国知局

- 2024-07-27 12:44:09

一种mems器件及其制造方法技术领域1.本发明涉及半导体技术领域,特别涉及一种mems器件及其制造方法。背景技术:2.mems(micro-electro-mechanical system,微机电系统)器件是在微电子技术基础上发展起来的采用微加工工艺制作的微电子机械器件,已经广泛地用作传感器和执行器。例如,mems器件可以是压力传感器、加速度计、陀螺仪、硅电容麦克风等。3.mems器件例如包括组装在一起的传感器芯片和电路芯片。其中,在传感器芯片中形成mems机械结构,在电路芯片中形成检测电路。把传感器芯片和电路芯片焊接在一起,从而形成mems器件。4.根据检测元件和方法的不同,压力传感器可以分为多种不同的类型,包括压阻式、电容式、谐振式等。压阻式压力传感器与其他类型的压力传感器相比,具有灵敏度高、响应速度快、可靠性高、功耗低、体积小等一系列优点。随着技术的进步,采用mems技术的压阻式压力传感器的技术日趋成熟,已经实现了生产的批量化和低成本化。5.在传统的压力传感器中,通过硅-玻璃或者硅-硅键合工艺形成空腔与支撑结构。该键合工艺导致压力传感器的尺寸和制造成本增加以及产品良率降低。6.专利cn109678103a公开了一种mems结构及其制造方法,不需要通过传统的键合封装工艺形成空腔,直接将空腔嵌入在半导体衬底内。该方法具体包括:在半导体衬底的第一表面,采用电化学腐蚀形成空腔,利用外延层封闭空腔。然后经由穿过外延层的开口在空腔的内壁上形成停止层。在半导体衬底的第二表面,采用深槽刻蚀工艺或湿法蚀刻工艺形成通道。经由通道去除停止层,使得空腔与外界环境连通。7.上述方法需要破坏对传感器来说至为重要的外延层(敏感膜层),以形成通道的刻蚀停止层,而且需要引进额外的停止层,增加了传感器器件的尺寸。技术实现要素:8.鉴于上述问题,本发明的目的在于提供一种mems器件及其制造方法,采用多孔层氧化形成的第一氧化层以及包裹第一氧化层的第二氧化层作为刻蚀停止层,用于形成与外部环境连通的通道,从而形成空腔。9.本发明的一方面提供一种mems器件的制造方法,所述方法包括:10.在半导体衬底的第一区域形成第一掺杂区;11.在所述半导体衬底的第一区域形成多孔层,所述多孔层位于所述第一掺杂区下方;12.对所述多孔层进行氧化形成第一氧化层以及包裹所述第一氧化层的第二氧化层;13.在所述第一掺杂区和所述半导体衬底的第一表面上形成外延层;14.在所述外延层上形成钝化层;15.在所述半导体衬底的第二表面形成到达所述第二氧化层的通道;以及16.经由所述通道去除所述第一氧化层以及所述第二氧化层,以在所述半导体衬底中形成空腔。17.优选地,形成所述半导体衬底的方法包括:18.提供第一半导体层;以及19.在第一半导体层上外延生长第二半导体层;20.其中,所述第一半导体层为重掺杂半导体层;所述第二半导体层为单晶半导体层或者轻掺杂半导体层。21.优选地,采用电化学腐蚀将所述第一区域中的第二半导体层转变成所述多孔层。22.优选地,通过调节所述第二半导体层的掺杂浓度调节所述多孔层的孔隙率。23.优选地,所述多孔层的孔隙率为40%~70%。24.优选地,在形成第一掺杂区的步骤之前,还包括:采用第一次离子注入和退火在所述第二半导体层中形成阱区,所述阱区围绕所述半导体衬底的所述第一区域。25.优选地,所述阱区的结深大于10微米。26.优选地,所述多孔层的厚度不超过所述阱区的结深。27.优选地,所述多孔层的厚度为3微米~7微米。28.优选地,采用第二次离子注入和退火形成网格形的第一掺杂区,所述第一掺杂区的结深小于所述阱区的结深。29.优选地,所述第一掺杂区的结深小于等于1微米。30.优选地,在所述半导体衬底的第一区域形成多孔层的步骤之前,还包括在所述半导体衬底的第一表面形成第一掺杂区的保护层,所述保护层至少覆盖所述第一掺杂区。31.优选地,所述保护层为氮化硅层。32.优选地,在形成所述外延层之前,采用干法刻蚀去除所述保护层。33.优选地,对所述多孔层进行氧化以形成第一氧化层以及包裹所述第一氧化层的第二氧化层的步骤包括:34.以相对较低的第一温度对所述多孔层进行一次氧化;35.以相对较高的第二温度对所述多孔层进行二次氧化。36.优选地,所述第一温度为400℃,所述第二温度为1100℃。37.优选地,所述第二氧化层的厚度设置为0.2微米~0.4微米。38.优选地,所述外延层的厚度为3微米~8微米。39.优选地,在所述半导体衬底的第二表面形成到达所述第二氧化层的通道的过程中,所述第一氧化层和所述第二氧化层作为刻蚀停止层。40.优选地,在所述半导体衬底的第二表面形成到达所述第二氧化层的通道的步骤之前,还包括:将所述半导体衬底减薄。41.优选地,在所述半导体衬底的第二表面形成到达所述第二氧化层的通道的步骤包括采用深槽刻蚀工艺或湿法蚀刻工艺去除所述半导体衬底的一部分。42.优选地,采用湿法刻蚀去除所述第一氧化层以及所述第二氧化层。43.优选地,在所述外延层上形成钝化层之前还包括:在所述外延层中形成多个敏感电阻。44.优选地,形成多个敏感电阻的步骤包括:采用第三次离子注入在所述外延层中形成所述多个敏感电阻。45.优选地,在形成多个敏感电阻的步骤之后,还包括:形成穿过所述外延层到达所述多个敏感电阻的互连结构。46.优选地,所述多个敏感电阻互连成惠斯通电桥。47.优选地,所述半导体衬底和所述敏感电阻为第一掺杂类型,所述阱区、所述第一掺杂区为第二掺杂类型,所述第一掺杂类型和所述第二掺杂类型相反。48.本发明的第二方面提供一种mems器件,包括:49.半导体衬底;50.位于所述半导体衬底中的空腔;51.位于所述半导体衬底的第一区域的第一掺杂区,所述第一掺杂区为网格形框架;52.位于所述第一掺杂区和所述半导体衬底第一表面上的外延层,位于所述外延层上的钝化层;以及53.从所述半导体衬底的第二表面到达所述空腔的通道,所述第一表面与所述第二表面相对,54.其中,所述外延层中没有到达所述空腔的开口。55.优选地,还包括位于所述外延层中的多个敏感电阻。56.优选地,还包括:穿过所述钝化层到达所述多个敏感电阻的互连结构。57.优选地,所述多个敏感电阻互连形成惠斯通电桥。58.优选地,所述多个敏感电阻为所述外延层中的掺杂区。59.优选地,所述衬底包括层叠的第一半导体层和第二半导体层;60.其中,所述第一半导体层为重掺杂半导体层;所述第二半导体层为单晶半导体层或者轻掺杂半导体层。61.优选地,还包括位于所述第二半导体层中的阱区,所述阱区围绕所述空腔,所述阱区限定出所述第一区域。62.优选地,所述阱区的结深大于10微米。63.优选地,所述第一掺杂区的结深小于所述阱区的结深。64.优选地,所述第一掺杂区的结深小于等于1微米。65.优选地,所述半导体衬底和所述敏感电阻为第一掺杂类型,所述阱区、所述第一掺杂区为第二掺杂类型,所述第一掺杂类型与所述第二掺杂类型相反。66.优选地,所述外延层的厚度为3微米~8微米。67.根据本发明实施例的mems器件及其制造方法,本发明通过采用多孔层氧化形成的第一氧化层以及形成于第一氧化层表面的第二氧化层作为刻蚀停止层,在半导体衬底的第二表面形成到达第二氧化层的通道,经由通道去除第一氧化层以及第二氧化层,以形成空腔,从而可以形成单芯片结构的压力传感器。采用该方法在形成通道时在刻蚀停止层停止,不会破坏外延层,克服了传统技术中从半导体衬底的第二表面(背面)腐蚀减薄导致外延层膜厚不均进而导致mems器件的灵敏度不一致、良率难以提升等问题。68.本发明实施例中,从半导体衬底的第二表面(背面)释放第一氧化层和第二氧化层,相对于现有技术从半导体衬底的第一表面(正面)释放氧化层的方法需要先在外延层中刻蚀开孔,释放氧化层后再填充开孔使外延层封闭,本发明实施例可以避免从半导体衬底的第一表面(正面)释放氧化层对外延层带来的损伤,使外延层保持完整性,减少了对外延层加工带来的不稳定性。69.该方法不需要通过传统的键合封装工艺形成空腔,巧妙的直接将空腔嵌入在半导体衬底内。使用该方法提供的mems器件结构新颖,工艺简单,避免了采用体硅加工技术带来的复杂的键合工艺,可实现小型化、低成本、大批量生产的要求。70.同时由于第一氧化层以及第二氧化层在形成空腔的过程中被去除,没有增加额外的结构,相较于需要额外设置刻蚀停止层的制备工艺,本发明实施例的mems器件及其制造方法进一步缩小了mems器件的尺寸。71.本发明优选地实施例中,采用保护层保护第一掺杂区的表面,以使得第一掺杂区的上表面在后续的多孔层氧化过程中不被氧化,进一步作为后续生长外延层的种子层;同时去除保护层时可以采用干法刻蚀,防止湿法腐蚀破坏多孔层表面的氧化层。72.本发明优选地实施例中,对多孔层进行氧化的过程中,采用低温氧化和高温氧化两步氧化方法,防止直接高温氧化导致的多孔层的表面能变小,造成多孔层结构的坍塌。73.本发明优选地实施例中,为了在后续的电化学腐蚀过程中得到多孔层的高孔隙率及较好的均匀性,本实施例的半导体衬底在重掺杂的第一半导体层上外延生长轻掺杂的第二半导体层,重掺杂的第一半导体层载流子浓度高,具有优异的导电性,使得多孔层的腐蚀更加均匀;轻掺杂的第二半导体层电化学腐蚀过程中具有优异的孔隙率。同时,可以通过调节第二半导体层的掺杂浓度来调节多孔层的孔隙率。附图说明74.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:75.图1示出了本发明第一实施例mems器件的俯视图;76.图2示出了本发明第一实施例的mems器件沿aa’方向的截面图;77.图3示出了图3a至3s示出根据本发明第二实施例的mems器件的制造方法中部分阶段的截面示意图。具体实施方式78.以下将参照附图更详细地描述本发明。在各个附图中,相同的元件采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。79.在下文中描述了本发明的许多特定的细节,例如器件的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本发明。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本发明。80.本发明可以各种形式呈现,以下将描述其中一些示例。81.图1示出根据本发明第一实施例的mems器件的俯视图,图2示出根据本发明第一实施例的mems器件沿aa’方向的截面图。如图1和图2所示,所述mems器件100包括在半导体衬底110中形成的空腔120、位于所述空腔120下方且与之连通的通道121、位于所述空腔120上的外延层150、以及位于所述外延层150中的多个敏感电阻160。82.在该实施例中,空腔120例如为正方形。阱区130围绕所述空腔120以限定出所述第一区域。第一掺杂区180为网格形框架,位于空腔120的顶部,外延层150覆盖第一掺杂区180、阱区130以及半导体衬底110,作为压力敏感薄膜。敏感电阻160位于外延层150中。第一掺杂区180的结深小于阱区130的结深。其中,所述外延层150中没有到达所述空腔的开口,保证了所述外延层150的完整性,进而保证了所述mems器件的稳定性。83.该mems器件100还包括位于外延层150上的钝化层140以及穿过钝化层140到达所述多个敏感电阻160的互连结构170。所述多个敏感电阻160均匀分布于外延层150中,经由互连结构170互连形成惠斯通电桥。84.在该mems器件中,半导体衬底110和敏感电阻160为第一掺杂类型,阱区130、第一掺杂区180例如为第二掺杂类型,第一掺杂类型和第二掺杂类型相反,第一掺杂类型例如为p型,第二掺杂类型例如为n型。85.本实施例中,所述半导体衬底110包括层叠的第一半导体层111以及第二半导体层112,所述空腔120以及所述阱区130均形成于所述第二半导体层112内。86.所述第一半导体层111为重掺杂p+型衬底,用于提供良好的导电性,所述第二半导体层112为轻掺杂p-型衬底,相对于所述第一半导体层111能获得较高的孔隙率,以在制备过程中得到较高的均匀性。87.图3a至3s示出根据本发明第二实施例的mems器件的制造方法中部分阶段的截面示意图。88.如图3a所示,根据本发明第二实施例的mems器件制造方法开始于半导体衬底110的第一半导体层111,在所述第一半导体层111上外延生长所述第二半导体层112。89.所述半导体衬底110的第二表面(背面)要求具有优异的导电性,又要求经过电化学腐蚀过程在所述半导体衬底110内形成均匀且高孔隙率的多孔层113。p+或n+型重掺杂半导体层内载流子浓度较高,有着良好的导电性,从而在后续电化学腐蚀反应能够平稳良好的进行,得到均匀性好的多孔层;但是其经过电化学腐蚀形成的多孔层的孔隙率低,例如电阻率为0.01~0.02ohm·cm的p+或n+型重掺杂硅衬底在电流密度很大时形成的多孔层的孔隙率也只有50%。90.轻掺杂半导体层会在电化学腐蚀过程中形成较高的孔隙率,例如电阻率为5~10ohm·cm的p-型单晶硅衬底在电流密度为40ma/cm2时,其孔隙率达到65%以上,当电流密度大于135ma/cm2时,其孔隙率约为80%。但是,轻掺杂衬底的背面导电性差,通常需要背面注入b(硼)来增加其导电性。b(硼)注入的不均匀性会导致后续电化学腐蚀过程中的电流不均匀,从而导致经过电化学腐蚀形成的多孔层的均匀性较差,例如约为13%。91.为了在后续的电化学腐蚀过程中得到轻掺杂多孔层的高孔隙率及重掺杂多孔层较好的均匀性,本实施例的所述半导体衬底110在重掺杂的第一半导体层111上外延生长轻掺杂的第二半导体层112,重掺杂的第一半导体层111具有优异的背面导电性,使得多孔层腐蚀更加均匀(例如可以达到3%);轻掺杂的第二半导体层112在后续的电化学腐蚀过程中具有优异的孔隙率,这样既可以通过调节外延的第二半导体层12的掺杂浓度获得可调节的孔隙率,也可以得到优异的背面导电性,使多孔层的腐蚀更加均匀。92.本实施例中,所述第一半导体层111例如是重掺杂p+单晶硅衬底,晶向例如为《100》,电阻率例如为0.01~0.02ohm·cm;所述第二半导体层112例如是p-单晶硅层,厚度例如为10um~50um,电阻率例如为5~10ohm·cm,电流密度例如为60~120ma/cm2,形成的多孔层113的孔隙率例如为40%~70%。93.如图3b至图3c所示,在半导体衬底110的第一表面形成具有开口的氧化层210,以所述氧化层210作为掩膜,经由具有开口的氧化层210进行第一次离子注入。94.具体地,在半导体衬底110的第一表面例如通过热氧生长氧化层210;在所述氧化层210的表面形成抗蚀剂层,采用光刻工艺图案化抗蚀剂层以形成抗蚀剂掩模,以及经由抗蚀剂掩模刻蚀所述氧化层210,以形成贯穿所述氧化层210的开口。在形成所述氧化层210的开口之后,采用溶剂溶解或灰化的方法去除抗蚀剂掩模。95.所述氧化层210的厚度为0.3微米~0.8微米,例如为0.4微米。96.在第一次离子注入中采用的n型掺杂剂例如是磷离子。通过控制离子注入的能量,使得n型掺杂剂从半导体衬底110的第一表面向下延伸至预定深度。97.如图3d所示,进行高温退火,在高温退火过程中,n型掺杂剂进一步扩散形成阱区130,阱区130的结深小于或者等于所述第二半导体层112的厚度,例如大于10微米,小于或者等于50微米。阱区130为矩形环状,阱区130围绕的半导体衬底110为第一区域,用于限定将要形成的空腔的形状。在高温退火之后例如采用hf酸进行漂洗以去除半导体衬底110表面的氧化层210。98.如图3e和图3f所示,采用光刻工艺图案化抗蚀剂层以在所述半导体衬底110的第一表面形成具有开口的抗蚀剂掩模pr1,开口位于阱区130限定的第一区域内。经由抗蚀剂掩模pr1的开口进行第二次离子注入,使得掺杂剂扩散形成n-型的第一掺杂区180。其中,所述第一掺杂区180位于所述阱区130限定的第一区域内。在第二次离子注入之后,例如通过灰化或溶解去除抗蚀剂掩模pr1。99.在第二次离子注入中采用的n型掺杂剂例如是磷离子。通过控制离子注入的能量,使得n型掺杂剂从半导体衬底110的第一表面向下延伸至预定深度。100.由于在无光照时,n型单晶硅难以发生电化学腐蚀,本实施例中注入磷离子以使得所述第一掺杂区180以及所述阱区130成为n型单晶硅:以在后续的电化学腐蚀过程中得以保留其原始形貌。其中,所述阱区130限定要形成空腔的形状,防止发生大面积的电化学腐蚀,限定腐蚀区域的范围。所述第一掺杂区180作为支撑结构,防止电化学腐蚀过程中出现塌陷。101.如图3g所示,进行高温退火。在高温退火过程中,n型掺杂剂进一步扩散,使得第一掺杂区180的结深小于阱区130的结深。第一掺杂区180在半导体衬底110的第一区域内形成网格形的框架,用于在后续步骤中形成外延层150。102.本实施例中,第一掺杂区180的结深小于等于1微米,用来保证后续外延层150下表面形貌的平整度。103.如图3h和图3i所示,在所述半导体衬底110的第一表面形成具有开口的保护层220,并在半导体衬底110的第一区域中形成多孔层113。104.具体地,在半导体衬底110的第一表面例如通过低压化学气相淀积(lpcvd)方式形成所述保护层220;在所述保护层220的表面形成抗蚀剂层,采用光刻工艺图案化抗蚀剂层以形成抗蚀剂掩模,以及经由抗蚀剂掩模刻蚀所述保护层220,以形成贯穿所述保护层220的开口。在形成所述保护层220的开口之后,采用溶剂溶解或灰化的方法去除抗蚀剂掩模。105.本实施例中,所述保护层220至少覆盖所述第一掺杂区180,对所述第一掺杂区180的表面形成保护,同时还要暴露出半导体衬底110的第一区域,以便对第一区域中的第二半导体层112进行电化学腐蚀。由于单晶硅的敏感膜层相较于多晶硅的敏感膜层性能更好,本实施例采用所述保护层220对所述第一掺杂区180的表面进行保护,保证了在后续氧化过程中,所述第一掺杂区180表面由于所述保护层220的保护而不被氧化,仍然为单晶硅,进而在后续外延过程中,能够在所述第一掺杂区180表面外延出单晶硅层。106.在一个具体的实施例中,所述保护层220例如为氮化硅层,厚度为0.1微米~0.5微米,例如为0.15微米。107.进一步地,采用电化学腐蚀第二半导体层112形成多孔层113。以所述保护层220作为硬掩模。将整个半导体结构浸入酸性溶液中,例如乙醇/氢氟酸/水的混合液,或丙酮/氢氟酸/水的混合液。例如,该酸性溶液的乙醇:氢氟酸的体积比为1:2。电流密度例如为90ma/cm2。108.在半导体衬底110的第一区域中发生电化学腐蚀,从而形成从半导体衬底110的第一表面向下延伸的多孔层113。n+型的阱区130和n-型的第一掺杂区180不发生电化学反应,仍然保持单晶结构。然后将整个半导体结构从腐蚀液中取出,进行清洗,从而完成电化学腐蚀步骤。109.所述多孔层113的厚度(即电化学腐蚀的深度)不超过所述阱区130的深度,防止腐蚀区域超出阱区130限定的第一区域,造成大面积电化学腐蚀。所述多孔层113的深度例如为3微米~7微米。110.如图3j所示,对所述多孔层113进行氧化形成第一氧化层115。111.该步骤中,所述多孔层113被氧化形成第一氧化层115。在所述第一氧化层的上表面(半导体衬底110的第一表面)、所述第一氧化层与所述第一掺杂区180接触的表面、所述第一氧化层与所述半导体衬底110接触的表面、所述第一氧化层与所述阱区130接触的表面以及所述半导体衬底110的第二表面形成第二氧化层114。第二表面与第一表面彼此相对。其中,所述第二氧化层114厚度为0.2~0.4微米。112.由于经由电化学腐蚀,所述第一区域内的第二半导体层112已经形成多孔层113,且孔隙率很高,疏松的或不完全氧化的多孔层113不能在后续的通道121的刻蚀过程发挥刻蚀阻挡的作用,本实施例需要将所述多孔层113完全氧化以形成致密的氧化层,以在后续的通道121的刻蚀的过程中作为刻蚀停止层,即所述第一氧化层115和第二氧化层114为致密的氧化层。113.所述多孔层113经过电化学腐蚀之后,多孔硅的孔壁厚约为0.05微米,将所述多孔硅完全氧化成氧化硅需要氧化生长大于0.05微米的氧化层;同时,由于所述第一掺杂区180的厚度小于1微米,为了防止所述第一掺杂区180被完全氧化成氧化硅,破坏所述第一掺杂区180的单晶硅层,本实施例中,所述第二氧化层114的厚度设置为0.2微米~0.4微米,既可以完全氧化所述多孔层113,又可以保证所述第一掺杂区180的单晶硅不被完全氧化。114.在进行氧化的过程中,首先采用相对较低的第一温度对所述多孔层113进行一次氧化,然后再采用相对较高的第二温度对所述多孔层113进行二次氧化。115.本实施例中,分两步对所述多孔层113进行氧化,防止突然的高温引起多孔硅表面缩聚,进而引起所述多孔硅表面能变小,容易发生坍塌。本实施例首先采用相对较低的第一温度对所述多孔层113进行氧化,相对较低的第一温度尚未能够使得所述多孔硅表面缩聚,但可以在所述多孔硅113的孔壁表层形成氧化层,再采用相对较高的第二温度进行氧化而形成氧化层时,不会对所述多孔硅的表面能造成影响,不容易发生坍塌,增加了稳固性。116.本实施例中,所述第一温度例如为400℃,所述第二温度例如为1100℃。117.如图3k所示,去除所述保护层220,暴露出所述第一掺杂区180的表面,并经由所述第一掺杂区180的表面形成外延层150。118.本实施例中,由于所述保护层220为氮化硅层,可以采用干法刻蚀方法去除所述保护层220,避免了湿法刻蚀过程中的hf溶液对所述第二氧化层114的破坏。干法蚀刻可选择等离子体刻蚀或反应离子刻蚀中的一种。119.进一步地,例如可以采用气相外延或者分子束外延等方法,以第一掺杂区180为种子层外延生长单晶硅,从而形成外延层150。在该实施例中,外延层150的厚度例如是3微米至8微米。120.本实施例中,在图3h和图3i所示的步骤中,由于所述保护层220对所述第一掺杂区180的表面进行保护,使得所述第一掺杂区180的表面在电化学腐蚀和氧化的过程中没有被腐蚀和氧化,仍然为单晶硅,进而能够在所述第一掺杂区180表面外延出单晶的外延层150。121.在一个具体的实施例中,在外延形成所述外延层150的过程中,注入n型掺杂剂,例如为磷离子,以使得所述外延层150为n型单晶硅,电阻率例如为1ω·cm。122.该外延层150覆盖半导体衬底110、阱区130、第二氧化层114以及第一掺杂区180的表面。123.形成所述外延层150之后,例如使用hf漂去所述半导体衬底110第二表面的第二氧化层114,以便后续进行深槽刻蚀。124.如图3l所示,采用光刻方法,在外延层150的表面形成具有开口的抗蚀剂掩模pr2。125.经由抗蚀剂掩模pr2的开口进行第三次离子注入,在外延层150中形成敏感电阻160。126.在第三次离子注入中采用的掺杂剂是p型掺杂剂,例如是硼离子。通过控制离子注入的能量,使得敏感电阻160从外延层150的表面向下延伸至预定深度。例如,在注入时可以采用7至10度的倾斜角,注入剂量一般为2e14~2e16cm-2。127.在该mems器件中例如形成四个敏感电阻160,对称分布于外延层150中。128.如图3m所示,去除抗蚀剂掩模pr2,进行高温退火以加深结深。退火温度例如是900℃~1100℃。129.如图3n和图3o所示,在经过第三次离子注入的外延层150上形成钝化层140,并图形化所述钝化层140以形成连接所述敏感电阻160与互连结构170的通孔141。130.具体地,所述钝化层140例如为二氧化硅层,在所述钝化层140的表面形成抗蚀剂层,采用光刻工艺图案化抗蚀剂层以形成具有开口的抗蚀剂掩模,经由抗蚀剂掩模刻蚀所述钝化层140,以形成贯穿所述钝化层140的通孔141。在形成所述钝化层140的通孔141之后,采用溶剂溶解或灰化的方法去除抗蚀剂掩模。所述通孔141暴露所述敏感电阻160的至少部分表面。131.如图3p所示,例如通过物理气相淀积(pvd)形成金属层,金属层的材料例如为铝。该金属层填充所述钝化层140的开口141,并且还覆盖所述钝化层140的表面。优选地,将金属层图案化形成互连结构170。132.例如通过干法刻蚀方式图案化所述金属层以形成互连结构170,采用的刻蚀气体例如为bcl3/cl2。133.上述互连结构170与敏感电阻160连接。在mems传感器为压阻式传感器的情形下,上述互连结构170与敏感电阻160连接形成惠斯通电桥。134.如图3q所示,在所述钝化层140以及互连结构170的表面形成抗蚀剂掩模pr3,以在形成空腔120的过程中对所述钝化层140以及互连结构170进行保护。135.抗蚀剂掩模pr3的厚度取决于所述空腔120的深度。在一个具体的实施例中将所述半导体衬底110减薄至200微米~400微米以便更加容易的形成空腔120。136.如图3r所示,采用光刻工艺,在半导体衬底110的第二表面形成具有开口的抗蚀剂掩模,第二表面与第一表面彼此相对。经由抗蚀剂掩模进行蚀刻,形成到达所述第二氧化层114的通道121,其中所述第一氧化层115和所述第二氧化层114作为刻蚀所述通道121的刻蚀停止层。137.在该步骤中,由于蚀刻剂的选择性,该蚀刻例如在第二氧化层114的表面停止。例如可以采用深槽刻蚀工艺或湿法蚀刻工艺形成通道121。深槽刻蚀工艺例如采用刻蚀气体sf6/c4f8,湿法蚀刻例如采用koh或者tmah溶液。在蚀刻之后,例如通过灰化或溶解去除抗蚀剂掩模。138.如图3s所示,经由通道121选择性去除所述第一氧化层115以及所述第二氧化层114,使得通道121与空腔120连通。139.在该步骤中,例如采用hf溶液去除所述第一氧化层115以及所述第二氧化层114,由于蚀刻剂的选择性,该蚀刻相对于半导体衬底110、阱区130、第一掺杂区180和外延层150去除所述第一氧化层115以及所述第二氧化层114。去除所述钝化层140上的抗蚀剂掩模pr3。140.本实施例中,所述mems器件例如为mems压力传感器,但不以此为限,可以理解的是,凡是需要从半导体衬底的第二表面刻蚀形成通道并释放形成空腔的mems器件都可以使用本技术中的方法。141.应当说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。142.依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123301.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

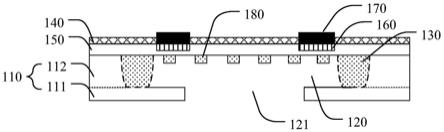

返回列表