一种微差压式MEMS压力传感器压敏芯片及其制备方法与流程

- 国知局

- 2024-07-27 12:49:14

一种微差压式mems压力传感器压敏芯片及其制备方法技术领域1.本发明属于传感器技术领域,涉及一种微差压式mems压力传感器压敏芯片及其制备方法。背景技术:2.mems压力传感器作为最为成熟的微机电系统(mems)元器件由于其小型化,制造成本低的优点得到广泛应用,但目前大部分已经实现产业化的mems压力传感器都主要用于测量100kpa(一个标准大气压)以上的压力,然而测量100kpa以下压力的mems传感器受到制备困难和成本较高等客观因素制约尚不常见。但是无论是在医疗生物领域还是军用方面,对1kpa以下微量程的压力传感测试的需求越来越大。对于mems微压传感器的设计制造,传感器的线性度和灵敏度性能上的平衡一直是制约mems压敏芯体的在该领域大规模应用的关键因素。为了感测微小的压力变化,压敏芯片感压膜(敏感结构)厚度必须做到足够小,才能满足传感器对灵敏度的要求。然而,过薄的膜厚会导致受到压力时,感压膜在感压方向挠度过大,从而导致传感器的线性度降低。技术实现要素:3.有鉴于此,本发明的目的在于提供一种微差压式mems压力传感器压敏芯片及其制备方法。4.为达到上述目的,本发明提供如下技术方案:5.一种微差压式mems压力传感器压敏芯片的制备方法,该方法包括以下步骤:6.s1:利用热氧化工艺,在作为器件层的单晶硅片两面各沉积一层氧化硅,利用腐蚀工艺在硅片上表面氧化硅层上刻蚀出压阻结构5,利用轻硼掺杂和浓硼掺杂工艺在硅片上表面制备出压阻条和欧姆接触区,注入完成后采用快速退火rtp工艺对注入造成的晶格损伤进行修复;7.s2:利用等离子体气相沉积工艺pecvd在硅片硼掺杂压阻结构5一面上沉积形成氧化绝缘层,厚度为500nm;并利用刻蚀工艺在绝缘层上开出欧姆接触的电接触孔;再利用金属薄膜沉积工艺在绝缘层上沉积形成金属薄膜,并通过金属腐蚀工艺刻蚀形成金属互联引线1,确保压阻结构5间形成电学互联;8.s3:利用腐蚀工艺在基板上表面氧化层上刻蚀出梁结构2的图形轮廓,然后利用该氧化层作为掩膜,通过反应离子刻蚀rie刻蚀硅形成梁结构2,深度为4um;9.s4:利用腐蚀工艺在硅片下表面氧化层刻蚀出“感压薄膜3+岛结构4”的区域图形;在刻蚀了“感压薄膜3+岛结构4”图形的氧化层表面再次喷涂光刻胶,显影形成岛结构4图形作为掩膜;利用反应离子深刻蚀drie工艺刻蚀硅,深度为岛结构4相应高度;最后去除剩余的光刻胶,露出“感压薄膜3+岛结构4”图形的氧化层;10.s5:以刻蚀了“感压薄膜3+岛结构4”图形的氧化层作为掩膜,再次使用反应离子深刻蚀drie体硅加工工艺在硅片底面上刻蚀“感压薄膜3+岛结构4”区域,形成目标尺寸的感压薄膜3和岛结构4;11.s6:去除硅片背面剩余氧化层,利用阳极键合工艺,在硅片背面键合作为玻璃基座7的玻璃片;12.背部基座根据要制备的压力传感器的应用类型来选择:13.若为差压类型,则在玻璃基座上加工通孔结构,保证感压薄膜背面与外界连通;14.若为绝压类型,则不加工通孔,通过高真空度阳极键合工艺完成感压薄膜背面与玻璃基座间真空压力参考腔的构建。15.可选的,所述s2中的金属薄膜为al。16.可选的,所述s3中,基板为n型高阻全硅片或soi;当使用soi作为基板时,drie工艺刻蚀到埋氧化层自停止,以提高感压薄膜厚度的尺寸精度与均匀度。17.基于权利要求所述制备方法的微差压式mems压力传感器压敏芯片,该压力传感器压敏芯片包括五层结构,即层一~层五;18.层一:为第一基底,是金属层,材料为铝、铜或铬金合金,通过mems刻蚀工艺制作成金属互联引线1;金属互联引线1将层一下方设置的层二中的压阻结构5的欧姆接触区电学导通构成惠斯通电桥形式压阻电路;压阻电路具有将被测压力信号转化为电学信号输出的功能;19.层二:为第二层基底,是单晶硅和氧化硅材料,包含刻蚀mems硅刻蚀工艺制作的梁结构2和硼元素掺杂工艺制作的压阻结构5;其中压阻结构5由高阻值的压敏电阻条和低阻值的欧姆接触区构成;梁结构2上表面设置两组压敏电阻条,两组压阻条分别相对压敏芯片结构中心对称排布在梁结构5上应力集中区域内;第一组压阻条长度方向垂直于芯片边框方向,第二组压阻条长度方向平行于芯片边框方向;20.层三:为第三层基底,设置在层二下方,材料为单晶硅,构成芯片的感压薄膜3;21.层四:为第四层基底,材料为单晶硅,上表面与层五的感压薄膜3相连;层四的中央设置有岛结构4;岛结构4下方及四周为空腔结构,保证感压薄膜3与岛结构4在受压时能够自由形变;层四的四周设有支撑边框6,支撑边框6的上、下面分别于感压薄膜3和玻璃基座7相连,支撑边框6厚度大于感压薄膜3的厚度,起到固定支撑的作用;22.层五:为第五层基底,是玻璃材质,中间设有通孔,通孔直径小于支撑边框6;上表面通过mems键合工艺与层四的边框结构6固定连接,作为压敏芯片底部的玻璃基座7;层五的下表面作为压敏芯片的贴片面,在压敏芯片进行外壳封装时,通过贴片胶与外壳固定。23.本发明的有益效果在于:24.本发明针对现有mems微差压传感器压敏芯片设计中灵敏度和线性度之间的结构设计矛盾提出一种“岛-膜-梁耦合”型压阻式微差压敏感芯片结构,相较于现有的“岛-膜耦合”型压敏芯片,在相同尺寸条件下大大提高了压敏芯片的线性度,并有效解决了“岛-膜耦合”型压敏芯片的应力集中区域小、应力分布均匀性差的问题,提高了压敏芯片的成品率和性能稳定性。25.本发明提出的“岛-膜-梁耦合”型微差压传感器压敏芯片的结构特点包含,抑制挠度变形的多孔岛结构、八边圆弧形感压薄膜结构、应力集中十字形梁结构及高对称性压阻电路。该压敏结构沿自身中心的x、y轴呈轴对称,以实现受z轴方向上的压力时,压敏结构上的应力被诱导集中在感压薄膜上方的十字梁结构与多孔质量块岛结构(及支撑边框结构)的交接区域。26.本发明的其他优点、目标和特征在某种程度上将在随后的说明书中进行阐述,并且在某种程度上,基于对下文的考察研究对本领域技术人员而言将是显而易见的,或者可以从本发明的实践中得到教导。本发明的目标和其他优点可以通过下面的说明书来实现和获得。附图说明27.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作优选的详细描述,其中:28.图1为单晶硅基片工艺流程图;29.图2为soi基片工艺流程图;30.图3为微差压式压敏芯片立体图;31.图4为微差压式压敏芯片俯视图;32.图5为微差压式压敏芯片侧视图。33.附图标记:1-金属互联引线;2-梁结构;3-感压薄膜;4-岛结构;5-压阻结构;6-支撑边框;7-玻璃基座。具体实施方式34.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。35.其中,附图仅用于示例性说明,表示的仅是示意图,而非实物图,不能理解为对本发明的限制;为了更好地说明本发明的实施例,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;对本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的。36.本发明实施例的附图中相同或相似的标号对应相同或相似的部件;在本发明的描述中,需要理解的是,若有术语“上”、“下”、“左”、“右”、“前”、“后”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此附图中描述位置关系的用语仅用于示例性说明,不能理解为对本发明的限制,对于本领域的普通技术人员而言,可以根据具体情况理解上述术语的具体含义。37.本发明设计一种压阻式微差压mems压力传感器压敏芯片,及其制造工艺。本发明所涉及mems压敏芯片基于硅的压阻效应,利用硅扩散工艺把掺杂元素(硼)离子注入扩散到硅片内,形成惠斯通电桥的敏感电阻,并利用惠斯通电桥将压力信号转换为电压信号,从而实现对压力的测量,其核心在于压敏芯片结构的设计以及满足结构制造要求的工艺方案。38.为实现上述“岛-膜-梁耦合”型微差压传感器压敏芯片的制造,本发明提出了以下两套mems制造工艺方案。分别为使用n型高阻全硅片作为基板材料的方案和使用soi(silicon on insulator)作为基板的方案。两者工艺步骤一致。不同点是使用soi可以在刻蚀感压薄膜3结构时通过soi的中间氧化层作为自停止层,有效控制刻蚀深度,保证感压薄膜3厚度的一致性。大大改善量产各批次间压敏芯片的性能指标稳定性,提高制作的成品率。但缺点是相较使用全硅基板材料费较高。本发明工艺方案包括以下步骤:39.a)利用热氧化工艺,在作为器件层的单晶硅片两面各沉积一层氧化硅,利用腐蚀工艺在硅片上表面氧化硅层上刻蚀出压阻结构5,利用轻硼掺杂和浓硼掺杂工艺在硅片上表面制备出压阻条和欧姆接触区,即压阻结构包含压阻条和欧姆接触区。注入完成后采用快速退火rtp工艺对注入造成的晶格损伤进行修复;40.b)利用等离子体气相沉积工艺pecvd在硅片硼掺杂压阻结构5一面上沉积形成氧化绝缘层(厚度约500nm)。并利用刻蚀工艺在绝缘层上开出欧姆接触的电接触孔。再利用金属薄膜沉积工艺在绝缘层上沉积形成al或其他金属薄膜,并通过金属腐蚀工艺刻蚀形成金属互联引线1,确保压阻结构5间形成电学互联;41.c)利用腐蚀工艺在基板上表面氧化层上刻蚀出梁结构2图形,然后利用该氧化层作为掩膜,通过反应离子刻蚀rie刻蚀硅形成梁结构2,深度约为4um;42.d)利用腐蚀工艺在硅片下表面氧化层刻蚀出“感压薄膜3+岛结构4”区域图形。然后在刻蚀了“感压薄膜3+岛结构4”图形的氧化层表面再次喷涂光刻胶,显影形成岛结构4图形作为掩膜。利用反应离子深刻蚀drie工艺刻蚀硅,深度为岛结构4相应高度。最后去除剩余的光刻胶,露出“感压薄膜3+岛结构4”图形的氧化层;43.e)以刻蚀了“感压薄膜3+岛结构4”图形的氧化层作为掩膜,再次使用反应离子深刻蚀drie体硅加工工艺在硅片底面上刻蚀“感压薄膜3+岛结构4”区域,形成目标尺寸的感压薄膜3与岛结构4;44.使用soi作为基片时,drie工艺刻蚀到埋氧化层自停止,有效提高感压薄膜厚度的尺寸精度与均匀度;45.f)去除硅片背面剩余氧化层,利用阳极键合工艺,在硅片背面键合作为玻璃基座7的玻璃片;46.背部基座可根据要制备的压力传感器的应用类型来选择,若为差压类型,则在玻璃基座上加工通孔结构,保证感压薄膜背面可与外界连通。若为绝压类型则不必加工通孔,通过高真空度阳极键合工艺完成感压薄膜背面与玻璃基座间真空压力参考腔的构建。47.图1为单晶硅基片工艺流程图;图2为soi基片工艺流程图。48.本发明提出的“岛-膜-梁耦合”型微差压传感器压敏芯片的结构特点包含,抑制挠度变形的多孔岛结构、八边圆弧形感压薄膜结构、应力集中十字形梁结构及高对称性压阻电路。该压敏结构沿自身中心的x、y轴呈轴对称,以实现受z轴方向上的压力时,压敏结构上的应力被诱导集中在感压薄膜上方的十字梁结构与多孔质量块岛结构(及支撑边框6)的交接区域。49.如图3~图5所示,本发明mems压阻式压力传感器,按空间构成包含5层结构基底,包括层一~层五,按功能分为7部分。50.层一:第一基底为金属层,材料为铝、铜或铬金合金等mems工艺常用金属原材料,通过mems刻蚀工艺制作成金属互联引线1。金属互联引线1将第一基底(层一)下方设置的第二基底(层二)中的压阻结构5的欧姆接触区电学导通构成惠斯通电桥形式压阻电路。压阻电路具有将被测压力信号转化为电学信号输出的功能。51.层二:第二层基底为单晶硅和氧化硅材料,包含刻蚀mems硅刻蚀工艺制作的梁结构2和硼元素掺杂工艺制作的压阻结构5。其中压阻结构5由高阻值的压敏电阻条和低阻值的欧姆接触区构成。梁结构2上表面设置两组压敏电阻条,两组压阻条分别相对压敏芯片结构中心对称排布在梁结构2上应力集中区域内。第一组压阻条长度方向垂直于芯片边框方向,第二组压阻条长度方向平行于芯片边框方向。52.层三:第三层基底设置在第二层基底(层二)下方,材料为单晶硅,构成芯片的感压薄膜3。53.层四:第四层基底材料为单晶硅,上表面与第三层基底(层五)的感压薄膜3相连。第四层基底(层四)的中央设置有岛结构4。岛结构4下方及四周为空腔结构,保证感压薄膜3与岛结构4在受压时可自由形变。第四层基底(层四)四周设有支撑边框6结构,支撑边框6的上、下面分别于感压薄膜3和玻璃基座7相连,支撑边框6厚度远大于感压薄膜3的厚度,在受到压敏芯片量程范围的1~3倍压力的情况下,不产生明显形变,起到固定支撑的作用。54.层五:第五层基底为玻璃材质,中间设有通孔,通孔直径略小于支撑边框6。上表面通过mems键合工艺与第四层基底(层四)的边框结构6固定连接,作为压敏芯片底部的玻璃基座7结构。第五层基底(层五)的下表面作为压敏芯片的贴片面,在压敏芯片进行外壳封装时,通过贴片胶与外壳固定。55.本发明的结构特征包含以下4点:56.a)八边圆弧形感压薄膜:57.微压式压敏芯片为实现在微小压力下产生更大的应力应变,以实现微小压力变化的测量,需要感压膜尽量薄,面积尽量大。但大面积的薄膜难于制作,且难以控制薄膜的整体均匀度。本发明提出了在正方形的支撑边框和岛结构的四角上添加大尺寸的圆弧倒角,使感压膜呈同心八边圆弧形状,该形状感压膜相较原正方框型感压膜大大缩减了感压膜的面积,但膜上的最大正应力基本保持不变降低了工艺难度,且降低了感压结构的挠度变形即减小了量程内的信号输出非线性度。58.b)多孔岛结构:59.为了抑制压敏芯片因感压结构的大挠度变形而造成的输出信号非线性度过高的问题,本发明提出在感压膜背面制作大体积的轴对称岛结构来抑制z轴方向的形变,从而提高压敏芯片的线性度。但是岛结构质量过大会导致感压膜上产生过大的预应力,预应力会造成压敏芯片的灵敏度降低,并且压敏结构质量过大会造成,输出信号受加速度的影响而产生漂移,降低压敏芯片在不稳定测试环境中的精度。所以本发明提出通过在岛结构上打均匀排布的小孔,有效改善了感压结构整体质量过大的问题。60.c)双梁式十字梁结构:61.由于微小量程的mems压敏芯片相较于传统的mems压敏芯片具有面积更大、厚度更薄的感压膜,这造成感压上的应力集中区域的占比大大降低,且应力集中区域内的应力分布均匀度也相对较低。本发明提出在感压薄膜上表面制作双梁式十字梁结构,利用梁结构与薄膜结构的刚度差进行感压结构上的应力分布再调整,使应力集中在梁结构、岛结构和薄膜结构的交接区域上,有效地降低了应变能在非应力集中区的耗散,且应力集中区域上应力分布的均匀性也得到提高,改善了因制造工艺误差造成的压敏电阻条与应力集中区域的位置偏移而产生的压敏芯片的性能下降。降低了制造工艺的精度要求,提高了芯片制造成品率。62.d)高对称性压阻电路:63.压阻式压敏芯片上压敏电阻条所在区域的应力集中效果及应力分布均匀度对芯片性能有极大的影响,传统的“岛-膜耦合”型压敏芯片由于决定应力分布的岛结构在芯片背面,所以在制作时需要使用双面对准,双面对准精度有限,增加了实际产品与理论模型间的性能误差。本发明设计一种高对称性的压阻电路(包含压敏电阻条、欧姆接触区及金属布线),压阻电路对称排布在上表面的双梁结构上,由于压阻条、双梁结构皆为对称结构,因此降低了制作工艺中的对准难度。并且压阻条与双梁结构同面,所以可采用单面对准工艺。单面对准工艺精度误差小于双面对准,提高了压阻条所在的位置精度。并且根据本发明所设计双梁结构的应力分布再调整作用,降低了制作背面岛结构时,岛结构与梁结构双面对准误差对芯片性能的影响。64.最后说明的是,以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本技术方案的宗旨和范围,其均应涵盖在本发明的权利要求范围当中。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123654.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

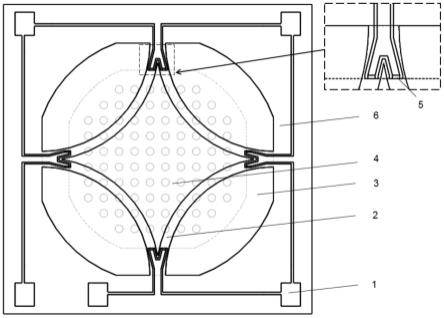

返回列表