CMOS工艺平台MEMS制造方法与流程

- 国知局

- 2024-07-27 12:50:47

cmos工艺平台mems制造方法技术领域1.本发明实施例涉及半导体工艺制造领域,特别涉及一种cmos工艺平台mems制造方法。背景技术:2.传统mems器件晶圆完成制造后,会进行切割,分割成单颗芯片,之后清洗切割过程中产生的硅屑,之后mems传感器结构释放,封装。由于mems有可动部件结构,所以切割清洗释放(有些产品还要适当减薄)后封装,这些工艺步骤会与产品本身产生矛盾,处置不当会造成mems器件损伤,导致大比例低良,甚至报废。3.另一方面,随着mems产品可穿戴需求的不断增加,以及晶圆流片水平的不断提高,且目前市场的强劲需求,目前传统mems集成工艺,普遍由晶圆厂完成晶圆制造由封测厂封装,从整个生产周期,以及产品在设备中的体积占比的小型化需求,传统制造封测工艺已经越来越不能满足需求。技术实现要素:4.本发明实施例提供了一种cmos工艺平台mems制造方法,以解决上述问题。所述技术方案如下:5.本发明实施例提供了一种cmos工艺平台mems制造方法,所述方法包括:6.第一步,制备mems器件晶圆;7.第二步,制作mems密封保护盖;8.第三步,键合所述mems器件晶圆与所述mems密封保护盖;9.第四步,对所述mems密封保护盖减薄,直至通孔露出;10.第五步,对所述通孔的侧壁进行绝缘处理并金属化填充,其中,所述mems器件晶圆引出有io电极与所述通孔导通;11.第六步,形成pad并对表面作钝化处理;12.第七步,在完成第六步的芯片表面进行涂覆光刻胶、曝光和显影后形成硬掩膜版,并流出芯片分割线槽;13.第八步,对所述芯片进行刻蚀,直至刻蚀深度大于芯片目标厚度;14.第九步,所述pad表面使用研磨保护胶带进行保护,并对所述mems器件晶圆的背面进行减薄,各芯片分散开;15.第十步,研磨胶带解uv,根据测试map扩膜挑拣后,获得mems芯片。16.可选的,所述第一步中,所述方法还包括:17.完成所述mems器件晶圆的制备后,再制造传感器部分。18.可选的,所述第二步,包括:19.刻蚀出所述mems密封保护盖的密封腔室以及所述通孔;20.对所述密封腔室进行保护,对所述通孔作进一步刻蚀;21.使用密封材料完成所述mems密封保护盖的制作。22.可选的,所述密封材料为硅基材料。23.可选的,对所述密封腔室进行保护的方法包括硬掩模版、氧化和钝化处理。24.可选的,所述第三步,包括:25.将所述通孔与引出的所述io电极对准,并在高真空条件下键合,形成真空腔。26.可选的,所述通孔与引出的所述io电极键合的方法采用低温键合法。27.可选的,所述第八步中,对所述芯片进行刻蚀之后,所述方法还包括:28.移除所述硬掩膜版。29.可选的,所述第八步,还包括:30.在刻蚀过程中进行cp测试。31.本发明实施例提供的一种cmos工艺平台mems制造方法,是一种mems高度集成化的方案,通过键合、挖通孔和金属化互联,以及减薄等工艺实现最终目的。并且使用该方法mems芯片在整个制造周期器件以及传感器可动部件表面实现了“零”接触,解决了mems器件因封装工艺导致的接触损伤,以及传统mems传感器难以像小型化发展、整体制造周期较长的问题。附图说明32.图1是本发明提供的cmos工艺平台mems制造方法的流程图;33.图2是第一步对应的结构示意图;34.图3是第二步对应的结构示意图;35.图4是第三步对应的结构示意图;36.图5是第四步对应的结构示意图;37.图6是第五步对应的结构示意图;38.图7是第六步对应的结构示意图;39.图8是第七步对应的结构示意图;40.图9是第八步对应的结构示意图;41.图10是第九步对应的结构示意图;42.图11是第十步对应的结构示意图。具体实施方式43.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明实施方式作进一步地详细描述。44.在本文中提及的“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。45.首先说明,图2至图11示意图不代表实际真实比例。46.请参考图1,其示出了本发明示例性实施例示出的cmos工艺平台mems制造方法的流程图。包含如下的工艺步骤:47.第一步,制备mems器件晶圆。48.如2所示,可选的,所述第一步中,所述方法还包括,完成所述mems器件晶圆的制备后,再制造传感器部分,原因是再制造传感器部分可有效避免设备沾污,并且可以避免衬底损伤。49.第二步,制作mems密封保护盖。50.如3所示,在一种可能的实施方式中,第二步包括如下内容一至三。51.内容一、刻蚀出所述mems密封保护盖的密封腔室以及所述通孔。52.内容二、对所述密封腔室进行保护,对所述通孔作进一步刻蚀。53.内容三、使用密封材料完成所述mems密封保护盖的制作。54.可选的,使用硅基材料或其他材料作为mems器件密封保护盖,对所述密封腔室进行保护的方法包括硬掩模版、氧化和钝化处理,但对此不作限定。55.第三步,键合mems器件晶圆与mems密封保护盖。56.在一种可能的实施方式中,如4所示,将所述通孔与引出的所述io电极对准,并在高真空条件下键合,形成真空腔。57.可选的,所述通孔与引出的所述io电极键合的方法优先采用低温键合法。58.第四步,对mems密封保护盖减薄,直至通孔露出。59.如5所示。60.第五步,对通孔的侧壁进行绝缘处理并金属化填充,其中,mems器件晶圆引出有io电极与通孔导通。61.如6所示。62.第六步,形成pad并对表面作钝化处理。63.如7所示。64.第七步,在完成第六步的芯片表面进行涂覆光刻胶、曝光和显影后形成硬掩膜版,并流出芯片分割线槽。65.如8所示。66.第八步,对芯片进行刻蚀,直至刻蚀深度大于芯片目标厚度。67.可选的,如9所示,所述第八步中,对所述芯片进行刻蚀之后,所述方法还包括:移除所述硬掩膜版。且此过程中,可灵活的穿插进行cp测试。68.此外,完成第八步,晶圆制造部分完成,可根据生成需求出货。第九步和第十步加工流程可在封测/装配厂完成,抑或在晶圆厂内完成。69.第九步,pad表面使用研磨保护胶带进行保护,并对mems器件晶圆的背面进行减薄,各芯片分散开。70.如10所示。71.第十步,研磨胶带解uv,根据测试map扩膜挑拣后,获得mems芯片。72.在一种可能的实施方式中,如11所示,研磨胶带解uv,根据测试map扩膜挑拣,最终得到高集成度,小型化的mems芯片。73.综上所述,采用本发明实施例提供的cmos工艺平台mems制造方法,是一种mems高度集成化的方案,通过键合、挖通孔和金属化互联,以及减薄等工艺实现最终目的。并且使用该方法mems芯片在整个制造周期器件以及传感器可动部件表面实现了“零”接触,解决了mems器件因封装工艺导致的接触损伤,以及传统mems传感器难以像小型化发展、整体制造周期较长的问题。74.以上所述仅为本发明的可选实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123774.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

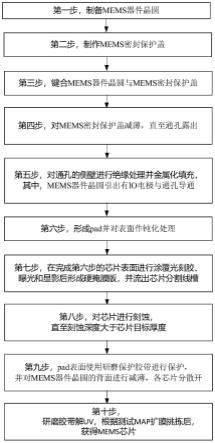

返回列表