基于CMOS工艺的CMOS-MEMS全集成热电堆芯片及制造方法与流程

- 国知局

- 2024-07-27 12:42:17

基于cmos工艺的cmos-mems全集成热电堆芯片及制造方法技术领域1.本发明涉及热电堆芯片结构设计技术领域,具体地,涉及一种基于cmos工艺的cmos-mems全集成热电堆芯片及制造方法。背景技术:2.热电堆传感器广泛应用于红外测温领域,如耳温枪,额温枪,红外测温枪,微波炉等产品。热电堆传感器的原理主要基于塞贝克效应,即当不同材料的一端结在一起,材料的两端有温度差时,会产生电动势,通过采集电压参数,可以得到材料冷端和热端的温差,进而实现远端测温。3.随着mems技术的发展,目前实现热电堆芯片主要有两大类技术,其一是梁膜结合的结构,这种方案的优势在于热端的聚热能力强,传感器的灵敏度较高。其二是封闭膜结构,该方案的灵敏度稍低,但是兼容cmos工艺。4.现有公开号为cn214121427u的中国专利,其公开了一种集成cmos电路的热电堆传感器系统,包括衬底,所述衬底包括第一区域和第二区域;cmos电路,位于所述第一区域内;热电堆传感器,位于所述第二区域内,包括多个热电堆结构以及第一类金属连线,所述第一类金属连线将所述多个热电堆结构与所述cmos电路串联连接。所述热电堆传感器还包括:位于所述衬底中的空腔,所述多个热电堆结构位于所述空腔的上方;以及位于所述多个热电堆结构之间的释放孔,其中,每个所述热电堆结构包括多个第一悬臂梁、每个所述第一悬臂梁上的至少一个热电偶和红外吸收薄膜。5.发明人认为现有技术中,热电堆芯片的背腔刻蚀在加工时有一定的工艺偏差,背腔刻蚀的角度会直接影响封闭膜的冷端和热端的距离,进而导致不同器件的热电压输出差异大,造成产品的一致性不好。技术实现要素:6.针对现有技术中的缺陷,本发明的目的是提供一种基于cmos工艺的cmos-mems全集成热电堆芯片结构及制造方法。7.根据本发明提供的一种基于cmos工艺的cmos-mems全集成热电堆芯片,包括衬底、微电机系统以及专用集成电路系统,所述微电机系统和专用集成电路系统二者在衬底上呈分隔设置,且所述衬底上设置有隔离层;所述专用集成电路系统包括mos管,所述mos管包括nmos管和pmos管,且所述nmos管和pmos管通过隔离层分隔;所述微电机系统包括热电堆和热沉区,所述微电机系统所在的衬底的背部开设有空腔,所述隔离层将热电偶和热沉区二者与空腔分隔;所述热电堆由多组热电偶串联形成,所述热电堆自衬底边缘位置延伸至衬底中部,所述热电堆与专用集成电路系统电连接,所述热沉区接地或悬空,且所述热沉区的内壁形成冷端边界。8.优选地,所述热电偶包括p型多晶和n型多晶,所述p型多晶和n型多晶串联。9.优选地,所述热沉区包括第一金属层、第二金属层、第三金属层、所述第一金属层、第二金属层以及第三金属层三者自下向上依次呈间隔设置或依次连通。10.优选地,所述第一金属层、第二金属层以及第三金属层三者之间的间隙填充有介质隔离层,所述介质隔离层的顶部设置有钝化层。11.优选地,所述热沉区为矩形框架结构,所述热沉区的内壁延伸至空腔的上方。12.根据本发明提供的一种基于cmos工艺的cmos-mems全集成热电堆芯片的制造方法,制造方法包括如下步骤:s1、准备所述衬底,备用;s2、在所述衬底上制作隔离层;s3、在所述衬底上制作nmos管和pmos管,且所述nmos管和pmos管通过隔离层进行隔离;s4、在所述nmos管和pmos管通过热氧化工艺原位生长制作栅氧层;s5、分别在所述栅氧层和衬底上淀积多晶层,且位于衬底另一侧的多晶层包括p型多晶和n型多晶;s6、制作所述第一通孔层,再淀积所述第一金属层,并通过所述第一通孔层和第一金属层将p型多晶和n型多晶串联;s7、依次制作所述第二通孔层、淀积第二金属层、制作第三通孔层以及淀积第三金属层并形成热沉区;s8、在所述介质隔离层上淀积钝化层;s9、在所述衬底的背面刻蚀形成空腔,所述空腔刻蚀停止在隔离层。13.优选地,针对步骤s2隔离层的制作,在所述衬底上刻蚀浅槽,再淀积介质层,之后通过cmp工艺平坦化实现隔离层的制作。14.优选地,针对步骤s3制作nmos管和pmos管;nmos管的形成过程:在衬底上注入硼形成pwell,再在pwell中通过磷注入形成nmos管的漏极和源极;pmos管的形成过程:在衬底上先形成nwell,再在nwell中通过磷、砷注入形成pmos管的漏极和源极。15.优选地,针对步骤5、步骤s6、步骤s7,所述多晶层完成后淀积介质,再淀积第一金属层,然后再淀积介质,之后再淀积第二金属层,以此类推。16.优选地,对于步骤s6和步骤s7,与所述nmos管和pmos管位于同一侧的第一金属层、第二金属层以及第三金属层用于走线、形成电容器件或形成电阻器件。17.与现有技术相比,本发明具有如下的有益效果:18.1、本发明通过第一金属层、第二金属层以及第三金属层配合形成的矩形热沉区,且热沉区的内壁延伸至空腔的上方,从而使热沉区的内壁为热电堆的冷端,有助于使热电堆的冷端和热端距离固定,进而有助于提高产品的一致性;19.2、本发明通过将微电机系统和专用集成电路系统设置在一起,有助于提高芯片的集成度,且有助于降低成本;20.3、本发明通过隔离层将热沉区和空腔隔离,一方面隔离层能够作为刻蚀空腔作业的停止层,有助于提高刻蚀作业的便捷性,另一方面隔离层对热沉区和热电堆起到支撑作用,有助于提高芯片结构的稳定性。附图说明21.通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:22.图1为本发明主要体现全集成热电堆芯片正面视角的剖面结构的示意图;23.图2为本发明主要体现全集成热电堆芯片俯视视角的剖面结构的示意图;24.图3为本发明主要体现全集成热电堆芯片上空腔与热沉区位置的示意图;25.图4为本发明主要体现深槽刻蚀工艺能力90±5°时热电堆薄膜的温升图谱。26.图中所示:27.具体实施方式28.下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。29.如图1和图2所示,根据本发明提供的一种基于cmos工艺的cmos-mems全集成热电堆芯片,包括衬底100、隔离层101、微电机系统11以及专用集成电路系统12,隔离层101位于衬底100上,微电机系统11和专用集成电路系统12二者在衬底100上呈分隔设置,且专用集成电路系统12分布设置在微电机系统11的周侧。衬底100为p型硅衬底100。30.专利集成电路系统包括mos管102,mos管102包括nmos管和pmos管,且nmos管和pmos管通过隔离层101分隔。nmos管是在衬底100上注入硼形成pwell,再在pwell中通过磷注入形成nmos管的漏极和源极;pmos管在衬底100上先形成nwell,再在nwell中通过磷、砷注入形成pmos管的漏极和源极。衬底100上的nmos管和pmos管的上方均生长有栅氧层103,从而分别形成nmos管和pmos管的栅极,任一栅氧层103上均淀积有多晶层104。31.如图1所示,微电机系统11包括热电堆和热沉区,热电堆由多个热电偶串联形成,热电偶淀积在衬底100的上方,且热电偶自衬底100边缘位置延伸至衬底100中部。微电机系统11区域内的多晶层104组成,多晶层104包括p型多晶114和n型多晶115,热电偶由p型多晶114和n型多晶115串联形成。p型多晶114和n型多晶115的上方均形成有第一通孔层105,任一第一通孔层105的下端均与对应的p型多晶114或n型多晶115连接,多晶层104的上方还淀积有第一金属层106,第一金属层106在衬底100上微电机系统11区域的中部和边缘位置均淀积有一个或多个,位于衬底100上微电机系统11区域中部的第一金属层106与第一通孔层105配合将相邻的p型多晶114和n型多晶115串联形成热电偶,最终形成ip(正端)和in(负端)两个接口,接入到专用集成电路系统12中进行电压的采集。32.专用集成电路系统12包括adc模块、带隙基准电压模块、振荡器数字电路接口以及otp校准等模块,ip(正端)和in(负端)两个接口与adc模块连接。33.如图1和图2所示,位于衬底100上微电机系统11区域的第一金属层106上自下向上一侧淀积有第二金属层108和第三金属层110,第一金属层106和第二金属层108之间连通有第二通孔层107,第二金属层108和第三金属层110之间连通有第三通孔层109。热沉区由第一金属层106、第二金属层108、第三金属层110、第二通孔层107以及第三通孔层109配合形成。在整体电路中,热沉区可以接到模拟地或者悬空处理。34.第一通孔层105、第一金属层106、第二通孔层107、第二金属层108、第三通孔层109以及第三金属层110六者均在衬底100上专用集成电路系统12的nmos管102和pmos管102的上方均成形有三组。位于集成电路系统区域的第一金属层106、第二金属层108以及第三金属层110用于走线、形成电容器件或形成电阻器件。35.微电机系统11和专用集成电路系统12位于衬底100上方的区域均填充有sio2,从而形成介质隔离层112,介质隔离层112的顶部设置有钝化层111,从而起到对微电机系统11和专用集成电路系统12的保护作用。36.如图1和图3所示,微电机系统11所在的衬底100的背部开设有空腔113,隔离层101将热电偶和热沉区二者与空腔113分隔,隔离层101对衬底100上方的器件起到支撑作用。热沉区为矩形框架结构,且热沉区的内壁延伸至空腔113的上方。热沉区的内侧为冷端边界,因为金属具有非常良好的热导率,热沉区的冷端边界与硅衬底100的温度梯度非常小,可以认为是芯片的冷端。37.在衬底100的背部开设有空腔113时,理想的情况是形成完全垂直的空腔113侧壁,但是实际工艺中,刻蚀角度首先无法形成90°完全垂直的形貌,其次,由于工艺的波动,其可能形成倒梯形和正梯形的形貌。假如没有热沉区域,那么热电堆芯片的热端(中心)到冷端的距离就会与设计值产生偏差,导致热电堆传感器的灵敏度存在差异,进而影响产品的一致性。38.存在热沉区时,只需要合理地设计热沉区的宽度值,即可保证热端和冷端的距离恒定不变,而不受背腔刻蚀工艺的影响。同时这种热沉区的设计,为背腔刻蚀工艺带来了较大的工艺容差,降低了工艺难度和成本。39.以下为本技术提供一个设计热沉区宽度w的计算过程:40.1)假设硅片的厚度为h,41.2)深槽刻蚀的工艺误差为90±α°,42.3)d=h*tanα;43.4)w≥h*tanα即可,为了保证热电堆的灵敏度以及更好的热沉效果,冗余的设计是热沉区的宽度可以尽可能往外边缘延伸。44.如图4所示,为深槽刻蚀工艺能力为90±5°时,热电堆薄膜的温升图谱,温升仿真基于热电堆薄膜900μm*900μm,硅衬底100的厚度400μm为基准。从图中可以看出,背腔刻蚀出倒梯形的形貌时,薄膜尺寸约达到935μm*935μm,此时温升最大,中心和边缘最大温差为261mk。当背腔刻蚀出正梯形的形貌时,薄膜尺寸约达到865μm*865μm,此时温升最小,中心和边缘最大温差为224mk。当设计热沉区时,冷端边界得以固定,热电堆有效薄膜面积总是在900μm*900μm。在工艺规格内,不论刻蚀出何种形貌,其中心和边缘最大温差基本都能保持在243mk。不设计热沉区时,导致的温升误差达到±7.8%,因此本发明可以显著的提高产品的一致性。45.根据本发明提供的一种基于cmos工艺的cmos-mems全集成热电堆芯片的制造方法包括上述的一种基于cmos工艺的cmos-mems全集成热电堆芯片结构,制造方法包括如下步骤:46.s1、准备p型硅衬底100,备用;47.s2、在衬底100上制作隔离层101,在衬底100上刻蚀浅槽,再淀积介质层,之后通过cmp工艺平坦化实现隔离层101的制作。48.s3、在衬底100的专用集成电路系统12区域制作nmos管和pmos管,且nmos管和pmos管通过隔离层101进行隔离。nmos管的形成过程:在衬底100上注入硼形成pwell,再在pwell中通过磷注入形成nmos管的漏极和源极。pmos管的形成过程:在衬底100上先形成nwell,再在nwell中通过磷、砷注入形成pmos管的漏极和源极。49.s4、在nmos管和pmos管通过热氧化工艺原位生长制作栅氧层103;50.s5、分别在栅氧层103和衬底100上淀积多晶层104,且位于衬底100另一侧的多晶层104包括p型多晶114和n型多晶115,多晶层104完成后淀积介质。51.s6、通过1p3m工艺制作第一通孔层105,再淀积所述第一金属层106,并通过第一通孔层105和第一金属层106将p型多晶114和n型多晶115串联,之后再淀积介质。52.s7、通过1p3m工艺依次制作所述第二通孔层107、淀积第二金属层108、淀积介质、制作第三通孔层109以及淀积第三金属层110并形成热沉区。53.s8、在介质隔离层112上淀积钝化层111;54.s9、在衬底100另一侧的背面刻蚀形成空腔113,空腔113刻蚀停止在隔离层101。55.工作原理56.制作时,先准备所述衬底100,备用;再在所述衬底100上制作隔离层101;然后在所述衬底100上制作nmos管和pmos管,且nmos管和pmos管通过隔离层101进行隔离;之后在nmos管和pmos管通过热氧化工艺原位生长制作栅氧层103;然后再分别在栅氧层103和衬底100上淀积多晶层104,且位于衬底100另一侧的多晶层104包括p型多晶114和n型多晶115;之后再制作所述第一通孔层105,再淀积所述第一金属层106,并通过所述第一通孔层105和第一金属层106将p型多晶114和n型多晶115串联;然后再依次制作第二通孔层107、淀积第二金属层108、制作第三通孔层109以及淀积第三金属层110并形成热沉区;之后再在介质隔离层112上淀积钝化层111;最后在在衬底100的背面刻蚀形成空腔113,所述空腔113刻蚀停止在隔离层101。57.在本技术的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。58.以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本技术的实施例和实施例中的特征可以任意相互组合。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123099.html

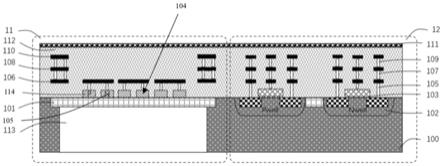

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。