基于热电的红外探测器的单片后互补金属氧化物-半导体集成的制作方法

- 国知局

- 2024-07-27 12:39:01

基于热电的红外探测器的单片后互补金属氧化物‑半导体集成相关申请的交叉引用1.本技术要求2019年4月1日提交的美国临时申请号62,827,205的权益。本技术交叉引用于2020年3月5日提交的美国专利申请序列号16/809,561,其是共同待决的于2019年7月21日的美国专利申请序列号16/517,653的部分继续申请,美国专利申请序列号16/517,653是美国专利申请序列号15/647,284的继续申请,美国专利申请序列号15/647,284标题为可扩展的基于热电的红外探测器,现为美国专利10,403,674,于2017年7月12日提交。本技术交叉引用2018年12月18日提交的美国专利申请序列号16/224,782,其是美国专利申请序列号15/653,558的分案申请,美国专利申请序列号15/653,558题为具有高cmos集成度的基于热电的红外探测器,现为美国专利号10,199,424,于2017年7月19日提交。本技术进一步交叉引用同一天提交的题为互补金属氧化物半导体和mems传感器的异质集成的pct国际申请,于2020年4月1日提交,其要求享有2019年4月1日提交的美国临时申请号62,827,207的权益。本技术进一步交叉引用2019年4月2日提交的美国临时申请号62,827,861。出于所有目的,将其全部公开内容通过引用整体并入本文。背景技术:2.由于众多应用的需求增加,对非制冷红外(ir)探测器的需求持续增长。这些应用仅举几例,包括空调系统,手机,自动驾驶汽车,物联网(iot),消防和交通安全。此外,预计在不久的将来,非制冷红外探测器将有更多应用。3.微机电系统(mems)ir探测器已经被提出。另外,由于所得系统的紧凑性和成本效益,期望mems ir探测器嵌入互补金属氧化物半导体(cmos)集成电路。但是,由于可用于后cmos工艺的热预算有限,因此mems ir探测器嵌入ic会带来巨大挑战。4.本公开内容针对嵌入有红外探测器的成本效益高且紧凑的系统。技术实现要素:5.本公开的实施例总体上涉及器件以及形成这种器件的方法。特别地,实施例涉及嵌入有mems组件或传感器的cmos器件。所述mems组件例如可以是ir传感器。6.在一个实施例中,一种用于形成器件的方法包括:提供衬底,所述衬底制备有具有cmos组件的互补金属氧化物半导体(cmos)区,以及具有用于互连所述cmos组件的互连件的be电介质。所述方法还包括在be电介质上形成mems层,所述mems层包括具有mems组件的mems区,所述mems组件包括重结晶的多晶硅结构。所述mems层占据be电介质的一部分。所述方法进一步包括在围绕mems层的be电介质上形成衬底密封环,并提供具有盖内表面和盖外表面的封盖。所述盖内表面包括盖密封环,所述盖密封环键合至be电介质上的衬底键合环以气密密封所述mems层。7.在一个实施例中,一种器件包括:衬底,所述衬底制备有具有cmos组件的互补金属氧化物半导体(cmos)区,和具有用于互连所述cmos组件的互连件的be电介质。所述器件还包括位于be电介质上的mems层,所述mems层包括具有mems组件的mems区,所述mems组件包括重结晶的多晶硅结构。所述mems层占据be电介质的一部分。所述器件还包括围绕mems层的be电介质上的衬底密封环,以及具有盖内表面和盖外表面的封盖。所述盖内表面包括盖密封环,所述盖密封环键合至be电介质上的衬底键合环以气密密封所述mems层。8.通过参考以下描述和附图,此处公开的实施例的这些和其他优点和特征将变得显而易见。此外,应当理解,此处所述的各种实施例的特征不是互相排斥的,并且可以以各种组合和排列存在。附图说明9.所述附图,结合在说明书中并形成说明书的一部分,示出了本公开的优选实施例,并且与说明书一起用于解释本公开的各种实施例的原理,其中相同的数字表示相同的部分。10.图1是半导体晶片的俯视图;11.图2a‑2f示出了器件的实施例的简化截面图;12.图3更详细地示出了器件的一部分的截面图;13.图4a‑4b示出了用于ir传感器的热电堆结构的示例性实施例的俯视图和截面图;14.图4c示出了2×3传感器阵列的示例性布局;15.图5a‑5i示出了用于形成器件的工艺的一个实施例;16.图6a绘出了激光热源的能量随时间的变化;17.图6b示出了使用图6a的激光热源通过激光退火模拟的结构;和18.图6c模拟了被激光热源加热的结构随时间变化在不同深度的温度。具体实施方式19.实施例总体上涉及器件,例如,具有嵌入式微机电系统(mems)模块的半导体器件或集成电路(ic)。所述ic例如是互补金属氧化物半导体(cmos)器件。对于mems模块,其可以包括一个或多个基于热电的红外(ir)探测器。所述mems探测器与cmos处理兼容。所述器件可以合并到产品中,例如热成像仪。例如,器件可以包括多个mems传感器,所述多个mems传感器可以设置为形成用于热成像仪的传感器阵列。所述传感器可用于其他类型的应用,例如单像素或线阵列温度或运动传感器。20.所述器件的制造可以涉及在衬底上形成特征构成电路组件,例如晶体管,电阻器,电容器,作为前道工序(feol)处理的一部分。作为后道工序(beol)处理的一部分,形成互连件以互连组件,使所述器件能够执行所需的功能。经过beol处理后,mems传感器被嵌入到器件上。此外,该过程还包括用封盖密封mems传感器,以气密密封mems传感器。21.为了形成所述特征,例如cmos电路组件,互连件和mems传感器,将层重复沉积在衬底上,并根据期望使用光刻技术进行图案化。例如,通过使用包含期望图案的掩模版通过用曝光源对光刻胶层进行曝光来对晶片进行图案化。曝光之后,光刻胶层被显影,从而将掩模版的图案转移到光刻胶层上。这形成光刻胶刻蚀掩膜。使用刻蚀掩膜执行刻蚀以复制下方晶片上的图案,可以包括一层或多层,具体取决于工艺阶段。在器件的形成过程中,许多掩模版可用于不同的图案化工艺。此外,可以在晶片上平行形成多个器件。所述器件用封盖气密密封。在一个实施例中,所述器件被晶片级密封。例如,所述器件晶片被盖晶片密封,平行地密封所述器件,所述器件晶片和盖晶片形成晶片堆叠。所述晶片堆叠被处理以单个化封装器件。22.图1示出了半导体晶片101的实施例的简化平面图。所述半导体晶片例如可以是硅晶片。晶片可以是轻掺杂的p型晶片。也可以使用其他类型的晶片,例如绝缘体上硅(soi)或硅锗晶片,以及掺杂有其他类型掺杂剂或掺杂剂浓度的晶片。23.所述晶片包括在其上形成器件115的有源表面111。可以在晶片上平行形成多个器件。所述器件例如沿着第一(x)方向排成行,并且沿着第二(y)方向排成列。提供具有经处理的封盖的盖晶片。例如,将盖晶片与所述晶片分开处理。盖晶片键合至具有所述器件的晶片,晶片级平行封装所述器件。所述晶片堆叠被切割,以将所述器件分成单个封装的芯片。在一个实施例中,将晶片堆叠部分地切割以暴露器件半导体晶片上的键合焊盘,然后进行完整切割以将封装器件单片化。24.图2a‑2f示出了器件200的实施例的简化截面图。所述器件例如是具有嵌入式mems结构或组件的cmos器件。在一个实施例中,所述器件是嵌入有基于热电的红外传感器的cmos器件。在一些实施例中,所述器件的mems结构包括多个基于热电的红外传感器。所述多个传感器可以设置为形成传感器阵列。例如,所述器件可以是红外成像仪,其中每个传感器可以是红外成像仪的像素。其他类型的mems结构或应用也可以。25.所述器件包括衬底201。例如,所述可以是晶片的一部分,如图1所示。共同元件可以不描述或不详细描述。所述衬底例如可以是半导体衬底,例如硅衬底。所述衬底例如可以是轻掺杂的p型硅衬底。其他类型的衬底或晶片也可用。26.在一个实施例中,所述衬底包括具有cmos组件的cmos区210。cmos区例如包括具有cmos器件或组件的cmos器件区。cmos组件可以包括金属氧化物半导体(mos)晶体管,诸如n型mos晶体管和p型mos晶体管。也可以在cmos器件区中提供其他类型的cmos组件,例如二极管,电容器和电阻器。p型mos晶体管和n型mos晶体管是互补型晶体管。晶体管包括用作晶体管主体的器件阱。另外,晶体管包括衬底上的栅极,所述栅极设置在位于器件阱中的第一和第二源极/漏极(s/d)区之间的器件阱上方。27.晶体管的栅极可以包括栅极电介质上方的栅电极。栅电极可以是多晶硅,栅极电介质可以是热氧化硅。其他类型的材料或栅极的设置也可用。对于p型mos晶体管,器件阱是n型阱,s/d区是重掺杂的p型区。另一方面,n型晶体管具有p型器件阱和重掺杂的n型s/d区。s/d区可以包括轻掺杂的延伸区。轻度掺杂的延伸区轻度掺杂有与所述重度掺杂的s/d区相同极性类型的掺杂剂。栅极的侧壁可以包括电介质间隔物。所述间隔物有助于对准所述s/d和轻掺杂的延伸区。器件阱可以包括器件阱接触件,所述器件阱接触件重掺杂有与器件阱相同极性类型的掺杂剂。28.所述cmos器件区可以包括用于具有不同操作特性或电压的不同类型晶体管的不同类型区域。例如,可以在低压(lv)区中提供低压晶体管,在中压(mv)区中提供中级或中压晶体管,在高压(hv)区中提供高压晶体管。也可以包括其他类型的器件区。例如,可以包括其中设置有存储器阵列的存储器区。29.如所讨论的,可以包括具有多个传感器的传感器阵列,所述多个传感器以行和列的传感器排列成矩阵。每个传感器对应于像素阵列中的一个像素。在这种情况下,cmos组件可以包括选择开关,行和列解码器以及读出电路。也可以包括其他cmos组件。cmos组件设置为读取阵列的每个像素。一旦读出传感器的全部阵列,就可以重建图像。所述图像例如是与阵列的传感器相对应的一帧。30.通常提供隔离区以隔离cmos组件。例如,提供隔离区给cmos器件区。另外,可以提供隔离区以将器件阱接触件与s/d接触件隔离。隔离区的其他设置也可以。隔离区可以是场氧化物(fox)隔离区。其他类型的隔离区,例如浅沟槽隔离(sti)区,也可用。31.层间电介质(ild)层220可以设置在衬底上。ild层用cmos组件覆盖cmos器件区。ild层例如是氧化硅层。其他类型的电介质层或电介质层的组合也可用。32.金属接触插塞,例如钨插塞,提供在ild层中,并且耦合到衬底和cmos组件上的接触区。例如,接触插塞耦合到cmos组件的s/d区和栅极,以及耦合到用于偏置阱和衬底的阱抽头。为其他类型的接触区提供接触插塞也可以。接触插塞例如可以通过镶嵌工艺形成。用于形成接触插塞的其他技术也可用。33.在ild层220上方的衬底上提供线后道工序(beol)电介质230。例如,beol电介质覆盖cmos区。beol电介质可以包括由beol电介质层形成的多个金属间电介质(imd)层。例如,beol电介质可以包括y个imd层,其中y为2–8。取决于设计和cmos工艺,也可以使用其他数量的imd层(包括1)。ild层和beol电介质可以被称为be电介质。34.imd层可以包括通孔电介质层和金属电介质层。取决于设计和工艺方法,可以由一个或多个电介质层形成imd层的通孔电介质层和金属电介质层。通孔电介质层可以设置在金属电介质层之上。提供位于通孔电介质层上方的金属电介质层也可以。例如,金属层(mx)可以设置在第一通孔层(vx)下方。例如,在3个imd层的情况下,x可以是1到3。金属电介质层包括金属线,而通孔电介质层包括通孔接触件。第一金属层电介质m1设置在ild层上方。beol电介质层的其他配置也可用。35.金属线和通孔接触件可以使用镶嵌技术形成,例如单或双镶嵌工艺。在单个镶嵌工艺的情况下,接触件和金属线在单独的工艺中形成。在双镶嵌工艺的情况下,金属线和接触件在同一工艺中形成。例如,在相同工艺中形成mx的金属线和vx‑1的通孔接触件。在一些实施例中,可以通过镶嵌和反应离子刻蚀(rie)工艺的组合来形成imd层。例如,金属线可以通过rie工艺形成,而接触件通过单镶嵌工艺形成。在rie工艺的情况下,形成金属层并使用刻蚀掩膜通过rie对其进行图案化以形成金属线。应该理解,可以使用不同的技术或技术或工艺的组合来形成beol电介质的不同imd层。例如,第一imd层可以使用镶嵌工艺形成接触件并使用rie工艺形成金属线,中间imd层可以使用双镶嵌工艺形成。可替代地,可以通过镶嵌和rie工艺的组合来形成imd层。形成imd层的其他设置也可用。36.至于beol电介质的顶部金属层,它可以用作具有焊盘金属线的焊盘层。焊盘线可以通过镶嵌或rie工艺形成。可以在焊盘线上方形成钝化层。钝化层例如可以包括一个或多个电介质层。在一个实施例中,钝化层包括位于氧化硅层上方的氮化硅层,从而形成sio2/sin钝化堆叠。其他类型的钝化层或堆叠也可用。可以在钝化层提供焊盘开口235以暴露焊盘线的接触焊盘。用于形成焊盘层的其他方法也可用。钝化层可以被认为是beol电介质的顶部电介质层。37.ild和imd层可以被平坦化以在cmos区上方形成平坦的顶表面。例如,在衬底上执行cmp。其他平坦化技术,例如用于填充间隙或平坦化衬底表面的旋涂玻璃(sog),也可用。结构上方ild和imd层的总厚度可能在100–400nm之间。为imd层提供任何其他厚度也可以。38.beol电介质上方为mems层240。在一个实施例中,mems层是单片集成mems层。例如,使用cmos工艺在beol电介质上方形成mems层。在一个实施例中,使用cmos工艺在beol电介质上方形成mems层,所述cmos工艺为后cmos兼容工艺。mems层的单片集成可减少器件占位面积并降低制造成本。另外,其他优点包括,例如,更大的填充因子和更短的互连长度,这导致传感器读出的寄生更快和更小。39.在一个实施例中,mems层240设置在器件的beol电介质之上和之内。例如,mems层占据了beol电介质的一部分。mems级限定了器件的mems区245。换句话说,mems区或mems层被下方的cmos区包围。mems区设置有mems组件。在一个实施例中,mems组件是具有传感器的传感器阵列。传感器可以设置在mems区的mems器件区内。例如,每个传感器可以位于其各自的mems器件区中。在一个实施例中,阵列的传感器是基于热电的ir mems传感器。为mems区提供其他类型的mems传感器也可以。传感器可以设置为具有m行和n列传感器的矩阵,从而形成m×n阵列。典型的阵列尺寸可以包括例如32×32阵列或80×64阵列。其他阵列大小也可以。阵列的尺寸可以取决于例如期望的图像分辨率。在某些情况下,阵列可以是一排传感器,例如m x 1或1x n阵列。为mems区提供单个mems传感器也可以。传感器可以对应于图像的像素阵列的像素。另外,传感器阵列还可包括与一个或多个盲像素相对应的一个或多个盲传感器。例如,盲像素用于校准目的。40.在一个实施例中,mems层包括基底电介质层。基底电介质层形成mems层的底部。例如,基底电介质层接触beol电介质的钝化层。基底电介质层可以是氧化硅层。其他类型的电介质层也可以。ir反射器设置在用于mems传感器的基底电介质层上。ir反射器可以是金属ir反射器。例如,金属ir反射器可以由钛(ti),钨(w)或铝形成。与cmos兼容的其他类型的ir反射器也可用。41.在一个实施例中,mems层包括设置在基底层和ir反射器上方的的牺牲层。牺牲层用于促进下部传感器腔的结构。在一个实施例中,牺牲层是非晶硅(αsi)层。其他类型的牺牲层也可用。42.mems电介质层设置在牺牲层上。mems电介质层例如可以是氧化硅层。其他类型的电介质层也可以。在某些情况下,电介质层可以是电介质层堆叠。mems电介质层用作膜,在其上布置传感器阵列的传感器的mems结构。在一个实施例中,mems结构是用作热电ir传感器或探测器的热电堆线结构。热电堆管线结构可以类似于例如在ussn 16/517,653,ussn 10,403,674,ussn 16/224,782和ussn 10,199,424中描述的那些,出于所有目的,它们都已通过引用并入本文。其他类型的mems结构或传感器,包括非ir传感器,也可以设置在mems区。43.在一个实施例中,热电堆线结构包括第一和第二极性掺杂的热电线段。在一个实施例中,热电线结构包括掺杂的多晶硅。在一个实施例中,使用激光退火将掺杂的多晶硅重结晶为非晶硅。其他类型的热电材料也可以用于热电堆线结构。金属接触件可以用于耦合热电堆线结构的第一和第二极性掺杂线段。金属接触件可以设置在第一极性掺杂段和第二极性掺杂段的交界处。金属接触件例如是ti或al合金接触件。其他类型的金属接触件也可用。第一传感器端子耦合到第一极性掺杂的热电线段,第二传感器端子耦合到第二极性掺杂的热电线段材料。所述端子可以是掺杂的热电材料的一部分。44.可以在线结构上方提供吸收器层。吸收器层例如设置为吸收入射的ir辐射。吸收器层可以是氮化钛(tin)层。其他类型的吸收器层也可用。例如,吸收器层可以是镍铬(nicr)层或掺杂的硅层。在一个实施例中,吸收器设置成吸收大部分入射的ir辐射。例如,吸收器可以设置为吸收大于85%的波长为8–14μm的入射ir辐射。提供任何其他设置也可用。在其他实施例中,吸收器设置为吸收波长为2–5μm的入射辐射。例如,使用干涉式吸收器的另一谐波。在一个实施例中,吸收器设置成吸收>50%的波长为2‑5μm的入射辐射。45.在一个实施例中,传感器保护层设置在吸收器层上方。传感器保护层用于保护传感器免受随后的刻蚀工艺的影响。例如,保护层用于保护线结构和吸收器层免受刻蚀剂(例如xef2)的腐蚀,所述刻蚀剂在释放工艺中用于形成下部传感器腔。在一个实施例中,保护层为氧化硅层。对ir辐射透明并且对在释放工艺中形成下部传感器腔中使用的刻蚀剂具有选择性的其他类型的层也可用。46.释放开口设置在mems电介质层和上方的其他层,如吸收器层和保护层,以在释放工艺中形成下部传感器腔时去除牺牲层。在一个实施例中,下部传感器腔具有一高度(在底部和顶部之间),所述高度的选择用于通过反射器最佳地反射ir辐射的期望波长。所述高度例如可以由牺牲层的厚度来定义。在一个实施例中,下部传感器腔的高度足以确保吸收器与反射器之间的1/4波长光学距离。例如,用于检测波长为8–12μm的ir辐射的光学距离大约为2–3μm。取决于要检测的波长,其他距离也可用。例如,通过减小或增加光学距离,可以分别检测具有较小或较大波长的ir辐射。光学距离被定义为ir辐射波具有穿过多层光路的距离处。47.可以在mems层提供mems到cmos(mc)接触件。mc接触件提供阵列的mems传感器到cmos区cmos组件的电连接。mc接触件可以是穿层通孔(tlv)接触件。mc接触件例如耦合到传感器的端子和顶部金属或焊盘层,其连接到cmos区的cmos组件。在一个实施例中,为阵列的每个传感器提供mc接触件。例如,为每个传感器的第一和第二端子提供第一和第二mc接触件。48.在一个实施例中,下部传感器腔是传感器阵列的公共下部传感器腔。例如,单个下部传感器腔用作传感器阵列的传感器的公共下部传感器腔。底部传感器腔由具有反射器的基底电介质层限定,而下部传感器腔的顶部由图案化的mems电介质层限定。所述腔没有侧壁。例如,在去除牺牲层之后,具有传感器结构的mems电介质层由mc接触件机械支撑。49.封盖250设置在衬底上,封装mems区。例如,将封盖键合到beol电介质的顶部,以在mems区上方形成真空。在一个实施例中,封盖由对红外辐射透明的材料形成。例如,封盖能够将红外辐射传输到传感器。封盖可以是硅(si)盖。其他类型的材料,例如锗(ge),硅锗(sige)或硫化锌(zns),也可以用于形成封盖。提供由透射红外线辐射的其他类型的材料形成的封盖也可以。50.在一个实施例中,封盖包括抗反射区260。抗反射区促进红外辐射透射穿过封盖。在一个实施例中,抗反射区包括在封盖的内(底部)表面上的底部光栅和在封盖的外(顶部)表面上的顶部光栅。光栅可以具有蛾眼光栅图案或结构,以促进红外辐射的透射。光栅可以具有促进红外辐射透射的其他类型的图案。可以通过刻蚀封盖表面来形成光栅。在一个实施例中,光栅设置为减少入射ir光的折射和反射。在一些实施例中,所述表面之一可以设置有表面光栅。例如,顶表面或底表面可以设置有表面光栅。也可以采用光栅的其他设置。51.在另一个实施例中,抗反射区包括设置在封盖的正面和背面上的抗反射涂层。例如,提供抗反射涂层代替表面光栅或图案。在表面之一上提供抗反射涂层也可以。例如,抗反射涂层可以设置在顶表面或底表面上。可以交替地将具有不同反射率的材料沉积在抗反射区的表面。例如,用于抗反射涂层的材料可以是硫化锌(zns)或锗(ge)。提供用于抗反射涂层的任何其他材料和沉积技术也可以。防反射涂层可以沉积在封盖表面并且被图案化以保留在抗反射区。在其中一个盖表面包括表面图案的情况下,另一个盖表面可以包括抗反射涂层。例如,抗反射区包括一个盖表面上的表面图案和另一盖表面上的抗反射涂层的组合。52.在一个实施例中,吸气剂270设置在封盖的内表面上。吸气剂吸收封装器件内部的水分和脱气。吸气剂例如可以是锆合金,钛(ti),镍(ni),铝(al),钡(ba)或镁(mg)。也可以使用其他类型的吸气剂材料,例如包括铈(ce)或镧(la)的稀土元素。吸气剂有助于维持真空,提高可靠性。在一个实施例中,吸气剂设置在mems层240的mems区245和封盖的抗反射区260的外部。53.采用密封环280以促进将封盖键合到衬底。密封环例如包括盖密封环280a和衬底密封环280b。衬底密封环设置在例如围绕mems层的beol电介质上。封盖和衬底密封环配合,将封盖键合到衬底。在一个实施例中,密封环可以是金属或金属合金。密封环可以是金基密封环,例如金,金锡或它们的组合。为密封环提供其他材料和结构也可以。例如,铝,铜,银钛,锗,锡,氮化钛,氧化硅,氮化硅或其组合,包括金和金锡。在一个实施例中,密封环通过热压缩配合。通过形成热压键或低共熔键将封盖键合到衬底上的其他技术也可用。54.当封盖键合到衬底时,封盖形成盖腔252,将mems区245封装在封盖键合区251内部。在一个实施例中,封盖气密密封mems区。腔容积例如可以由密封环的高度限定。此外,抗反射区和传感器之间的期望距离可以由密封环的高度确定。如所讨论的,在一个实施例中,下部传感器腔不具有腔侧壁。例如,下部传感器腔与盖腔连通。55.参照图2a,封盖包括平坦的或基本平坦的内表面和外表面。应当理解,抗反射区可以包括表面图案和/或抗反射涂层,使其基本上是平坦的。但是,平坦包括平坦和基本平坦。这样,抗反射区之间的容积和距离由密封环的高度确定。56.在另一实施例中,如图2b所示,封盖包括在其内表面上的盖凹部256。盖凹部例如设置在抗反射区外部的盖底面。盖凹部可具有正方形或矩形的覆盖区或形状。盖凹部的其他形状也可用。取决于盖晶片的厚度,盖凹部的深度可以在10,20,30,100至500μm的范围内。具有比500um深的盖凹部也可用。在一个实施例中,盖凹部改善了腔内的整体真空度。例如,盖凹部增加封盖和mems层之间的盖腔总容积。在将盖晶片键合到器件衬底之后,较大的体积改善整体真空度。这样,可以从器件捕获更好的成像质量。57.在一个实施例中,吸气剂270设置在盖凹部的内表面上。吸气剂吸收封装器件内的水分和脱气。吸气剂例如可以是锆合金,钛(ti),镍(ni),铝(al),钡(ba)或镁(mg)。也可以使用其他类型的吸气剂材料,例如包括铈(ce)或镧(la)的稀土元素。吸气剂有助于维持真空,提高可靠性。58.在另一个实施例中,如图2c所示,提供封盖,除了盖凹部256设置在mems区245上方之外。在盖凹部中提供抗反射区260使得抗反射区和传感器之间的距离可以由盖凹部的深度控制,该深度与密封环的高度无关。吸气剂270可以设置在盖凹部之外的封盖内表面上。吸气剂吸收封装器件内的水分和脱气。吸气剂有助于维持真空,提高可靠性。59.在另一个实施例中,如图2d所示,提供封盖250。封盖被处理成包括盖凹部256。盖凹部例如设置在具有盖密封环280a的封盖的盖键合区251的内部。例如,盖键合区位于围绕盖凹部的封盖内表面的边缘。对于给定的密封环高度,盖凹部增加整个盖腔容积。此外,可以通过增加盖凹部的深度而不增加密封环高度来增加深度。吸气剂270可以设置在位于mems区245上方的抗反射区260外部的盖凹部的内表面上。吸气剂吸收封装器件内的水分和脱气。吸气剂有助于维持真空,提高可靠性。60.如图2e所示,提供具有浅和深盖凹部256和257的封盖250。类似于图2d的盖凹部,浅盖凹部被具有盖密封环280a的封盖的盖键合区251围绕。另外,深盖凹部设置在封盖抗反射区260的外部。深凹部增加盖腔252的容积。吸气剂270可以设置在抗反射区260外部的深凹部内表面上。吸气剂吸收封装器件内的水分和脱气。吸气剂有助于维持真空,提高可靠性。61.在另一个实施例中,如图2f所示,提供封盖250。封盖类似于图2e的封盖,除了类似于图2c,深盖凹部257设置在mems区上方。例如,位于深盖凹部内的抗反射区260。吸气剂270可以设置在深盖凹部外部的浅盖凹部256的内表面上。吸气剂吸收封装器件内的水分和脱气。吸气剂有助于维持真空,提高可靠性。62.图3示出了器件300的实施例的一部分的简化截面图。如图所示,所述器件包括具有cmos区和mems区的mems器件区的器件的一部分。该器件可以类似于图2a‑2f的器件,但没有封盖。可以不描述或不详细描述共同元素。63.所述器件包括衬底301。该衬底例如可以是半导体衬底,例如硅衬底。衬底例如可以是轻掺杂的p型硅衬底。其他类型的衬底或晶圆也可用。64.在一个实施例中,衬底包括在cmos器件区中具有cmos组件的cmos区310。cmos组件可以包括金属氧化物半导体(mos)晶体管,诸如n型mos晶体管和p型mos晶体管。如图所示,该器件的一部分包括第一和第二晶体管,每个晶体管在s/d区314和316之间具有栅极312。mos晶体管可以是n型,p型或n型和p型mos晶体管的组合。cmos区还可以包括其他类型的cmos组件,例如二极管,电容器和电阻器。可以提供隔离区以隔离cmos组件。例如,提供隔离区以隔离具有第一和第二晶体管的第一和第二cmos器件区。65.层间电介质(ild)层320可以设置在衬底上。ild层用cmos组件覆盖衬底和cmos区。ild层例如是氧化硅层。其他类型的电介质层或电介质层的组合也可用。金属接触插塞328,例如钨插塞,提供在ild层中,并且被耦合到衬底和cmos组件上的接触区。例如,接触插塞耦合到cmos组件的s/d区和栅极,以及耦合到用于偏置阱和衬底的阱抽头。为其他类型的接触区提供接触插塞也可用。接触插塞例如可以通过镶嵌工艺形成。用于形成接触插塞的其他技术也可用。66.在ild层320上方的衬底上提供线后道工序(beol)电介质330。beol电介质可以包括由beol电介质层形成的多个金属间电介质(imd)层。例如,beol电介质可以包括y个imd层,其中y为2–8。取决于设计和cmos工艺,也可以使用其他数量的imd层(包括1)。ild层和beol电介质可以被称为be电介质。67.imd层可以包括通孔电介质层336和金属电介质层332。imd层的通孔电介质层和金属电介质层可以由一个或多个电介质层形成,取决于设计和工艺方法。通孔电介质层可以设置在金属电介质层之上。例如,金属层(mx)可以设置在第一通孔层(vx)下方。例如,如图所示,beol包含3个imd层(x=1到3)。金属电介质层包括金属线334,通孔电介质层包括通孔接触件338。第一金属层电介质m1设置在ild层上方。beol电介质层的其他设置也可用。68.金属线和通孔接触件可以使用镶嵌技术形成,例如单或双镶嵌工艺。在单个镶嵌工艺的情况下,接触件和金属线在单独的工艺中形成。在双镶嵌工艺的情况下,金属线和接触件在同一工艺中形成。例如,以相同的工艺形成mx的金属线和vx‑1的通孔接触件。在一些实施例中,可以通过镶嵌和反应离子刻蚀(rie)工艺的组合来形成imd层。例如,金属线可以通过rie工艺形成,而接触件通过单镶嵌工艺形成。在rie工艺的情况下,形成金属层并使用刻蚀掩膜通过rie进行图案化以形成金属线。应该理解,可以使用不同的技术或技术或工艺的组合来形成beol电介质的不同imd层。例如,第一imd层可以使用镶嵌工艺形成接触件,使用rie工艺形成金属线,中间imd层可以使用双镶嵌工艺形成。可替代地,可以通过镶嵌和rie工艺的组合来形成imd层。形成imd层的其他设置也可用。69.至于beol电介质的顶部金属层(例如m3),它可以用作具有焊盘金属线的焊盘层。焊盘线可以通过镶嵌或rie工艺形成。可以在焊盘线上方形成钝化层337。钝化层例如可以包括一个或多个电介质层。在一个实施例中,钝化层包括在氧化硅层上方的氮化硅层,形成sio2/sin钝化堆叠。其他类型的钝化层或堆叠也是可用。可以在钝化层提供焊盘开口以暴露焊盘线的接触焊盘。用于形成焊盘层的其他方法也可用。70.ild和imd层可以被平坦化以在cmos区上方形成平坦的顶表面。例如,在衬底上执行cmp。其他平坦化技术,例如用于填充间隙或平坦化衬底表面的旋涂玻璃(sog),也可用。71.mems层340设置在beol电介质上方。在一个实施例中,mems层是单片集成的mems层。在一个实施例中,mems层包括基底或缓冲层339。基底层是电介质基底层,例如氧化硅。基底层例如用作刻蚀停止层。如所讨论的,截面图是mems阵列的传感器(例如,ir传感器)的mems器件区。72.如图所示,mems器件区包括下部传感器腔342。例如,基底层用作下部传感器腔的底部。在一个实施例中,下部传感器腔是传感器阵列的公共下部传感器腔。例如,传感器阵列的传感器共用相同下部传感器腔。73.ir反射器350设置在下部传感器腔的底部。ir反射器例如可以是金属ir反射器。例如,金属ir反射器可以由钛(ti),钨(w)或铝(al)形成。与后cmos兼容的其他类型的ir反射器也可用。74.mems电介质层358形成下部传感器腔的顶部。mems电介质层例如可以是氧化硅层。其他类型的电介质层也可用。在某些情况下,电介质层可以是电介质层堆叠。mems电介质层用作膜,在其上布置传感器的mems结构362。在一个实施例中,mems结构362是用作热电ir传感器或探测器的热电堆线结构。其他类型的mems结构或传感器,包括非ir传感器,也可以设置在传感器区中。75.在一个实施例中,热电堆线结构包括第一和第二极性掺杂的热电堆线段366和368。在一个实施例中,热电堆线结构包括掺杂的多晶硅。在一个实施例中,使用激光退火将掺杂的多晶硅重结晶为非晶硅。激光退火可以使非晶硅重结晶以及激活掺杂剂。与后cmos兼容的其他类型的热电材料也可以用于热电堆线结构。78.金属接触件370可以用于耦合热电堆线结构的第一和第二极性掺杂线段。金属接触件可以设置在线结构的相邻末端的交界或段的界面处。其他类型的金属接触件也可用。第一传感器端子365耦合到第一极性掺杂的热电线段材料,并且第二传感器端子367耦合到第二极性掺杂的热电线段材料。所述端子可以是掺杂的热电材料的一部分。77.可以在线结构上方提供吸收器层372。吸收器层例如设置为吸收入射的ir辐射。吸收器层可以是氮化钛(tin)层。其他类型的吸收器层也可用。例如,吸收器层可以是镍铬(nicr)层或掺杂的硅层。在一个实施例中,吸收器设置成吸收大部分入射的ir辐射。例如,吸收器可以设置为吸收大于85%的波长为8–14μm的入射ir辐射。提供任何其他设置也可用。在其他实施例中,吸收器设置为吸收波长为2–5μm的入射辐射。例如,使用干涉式吸收器的另一谐波。在一个实施例中,吸收器设置成吸收>50%的波长为2‑5μm的入射辐射。78.在一个实施例中,传感器保护层380设置在吸收器层上方。传感器保护层用于保护传感器免受随后的刻蚀工艺的影响。例如,保护层用于保护线路结构和吸收器层免受诸如xef2之类的刻蚀剂的腐蚀,该刻蚀剂用于在释放工艺中形成下部器件腔。在一个实施例中,保护层为氧化硅层。对ir辐射透明并且对释放工艺中形成下部器件腔使用的刻蚀剂具有选择性的其他类型的层也可用。在一个实施例中,传感器保护层可包括多个电介质层。例如,第一电介质层设置在线结构上并被图案化以形成用于接触件的开口。形成金属接触件和吸收器层,然后提供顶部保护层,覆盖线结构和吸收器层。79.释放开口382设置在电介质基底层和上方的其他层中,例如保护层,以使得能够在形成下部传感器腔的释放工艺中去除下部传感器腔牺牲材料。80.mems至cmos(mc)接触件348可以设置在mems层。mc接触件提供mems传感器至cmos区cmos组件的电连接。mc接触件例如耦合到传感器的端子和beol电介质的顶部金属或焊盘层,其连接到cmos区中的cmos组件。在一个实施例中,为阵列的每个传感器提供mc接触件。例如,为每个传感器的第一和第二端子提供第一和第二mc接触件。在释放工艺之后,mc接触件为具有传感器的mems电介质层提供机械支撑。81.封盖封装mems层的mems区。封盖形成上部传感器腔。在一个实施例中,封盖形成用于mems区传感器的公共上部传感器腔。提供焊盘开口以暴露位于mems层边缘的cmos区中的焊盘。82.图4a示出了mems传感器或结构450的实施例的简化俯视图,图4b示出了沿a‑a’,b‑b’和c‑c’的mems结构的各种截面图。顶视图不包括保护层。mems结构是线结构。线结构是用作热电ir传感器或探测器的热电堆。线结构设置在限定下部器件腔顶部的膜或电介质层上。在一个实施例中,线结构包括具有弯曲形状并占据膜表面的单个线单元(n=1)。83.在一个实施例中,线单元包括重结晶的非晶硅。其他类型的线单元也可用。例如,可以采用与后cmos兼容的热电材料来形成线结构。84.线单元包括第一和第二线段420和440。第一端451是第一线段的一部分,而第二端452是第二线段的一部分。在一个实施例中,第一端和第二端可以用作热电堆的冷结。第一线结构端子454布置在第一端,第二线结构端子456布置在第二端。所述端子例如是线结构的线单元的一部分。所述端子用作mems结构或传感器的端子。85.在一个实施例中,第一线段掺杂有第一极性类型的掺杂剂,第二线段掺杂有第二极性类型的掺杂剂。例如,第一线段重掺杂有第一极性类型的掺杂剂,第二线段重掺杂有第二极性类型的掺杂剂。第一极性类型可以是p型,第二极性类型可以是n型。提供n型的第一极性类型和p型的第二极性类型也可以。可以使用分开的注入来掺杂线段。86.可以使用掩膜和刻蚀技术来图案化线结构。例如,将光刻胶设置在线结构层上。光刻胶可以由曝光源通过包含期望的线结构图案的掩模版曝光。显影后,将掩模版的图案转移到光刻胶上以形成刻蚀掩膜。采用刻蚀使用刻蚀掩膜来图案化线结构层以形成线结构。刻蚀掩膜例如可以是光刻胶掩膜。刻蚀例如是各向异性刻蚀,例如反应离子刻蚀(rie)。其他刻蚀工艺也可用。在一个实施例中,刻蚀形成具有第一和第二线段的线结构。替代地,线结构可以是具有例如第一和第二段的非连续线结构。所述第一段和第二段可以通过金属接触件电连接。87.如图所示,线段是彼此的镜像。这将产生大约相同长度的线段。通过为线段提供曲折设计,可以有效地使用传感器区,同时形成具有所需电阻的线结构。例如,线结构的电阻约为5–50kω。其他电阻也可用。88.为了掺杂第一和第二线段,可以使用分开的注入物。例如,使用第一注入物掩膜的第一注入物用于掺杂第一线段,使用第二注入物掩膜的第二注入物用于掺杂第二线段。在一个实施例中,线段是重结晶的αsi线段。采用激光退火来重结晶αsi线段以及激活掺杂剂。89.线电介质层458覆盖线结构,填充间隙。线电介质层为热电堆膜提供机械支撑。线电介质层可以是例如旋转玻璃(sog)。其他类型的线电介质层也可以。电介质层的顶表面可位于线结构的顶部上方100‑400nm。在线结构的顶部上方提供具有其他厚度的电介质层也可用。92.提供接触件466以电耦合第一和第二段。接触件例如是金属接触件,例如钛(ti)或铝(al)。其他类型的接触件也可用。为了形成接触件,在电介质层形成接触开口,以暴露第一段和第二段的接合处附近的线结构。在衬底上形成金属层并对其进行图案化,使接触件耦合第一段和第二段。金属层例如可以是通过溅射或电镀形成的钛(ti)或铝(al)。其他类型的金属层或形成技术也可用。91.吸收器层457形成在衬底上,覆盖电介质层。可以使用刻蚀和掩膜工艺图案化吸收器层。图案化的吸收器层用作线结构上方的吸收器。在一个实施例中,吸收器层被图案化,覆盖线结构的中心部分和接触件,使中心部分外部的支腿部分暴露。吸收器层例如吸收ir辐射。吸收器层可以是tin或nicr层。吸收器层例如可以通过溅射形成。其他类型的吸收器层也可用。在一个实施例中,吸收器设置成吸收大部分ir辐射。例如,吸收器可以设置为吸收大于85%的8至14μm波长的ir辐射。吸收其他波长也可以。如图所示,吸收器层设置在接触件上方。吸收器用作热电堆的热结。第一线结构的第一端451和第二线结构的第二端452用作热电堆的冷结。未被吸收器覆盖的线结构支腿部分在热结和冷结之间提供热隔离。92.可以提供保护层459。保护层例如覆盖mems结构。保护层保护mems结构免于随后工艺的影响。该保护层例如是通过cvd形成的氧化硅层。其他类型的保护层也可用。93.图4c示出了传感器阵列404。传感器阵列包括多个传感器单元410。传感器单元包括耦合至mems结构的开关,所述mems结构例如是图4a‑4b中所描述的一个或多个线结构。共同元素可以不描述或不详细描述。94.传感器单元设置为形成具有m行和n列的阵列。传感器单元对应于传感器阵列的像素。传感器单元通过行线(rlm)在行方向上耦合,通过列线(cln)在列方向上耦合。传感器单元可以对应于像素。此外,公共线(coms)也用于耦合每列中的传感器单元。例如,传感器的每一列耦合到各自的com(例如,com1,com2或com3)。如图所示,该阵列包括一个2x3的阵列(m=2和n=3)。例如,传感器单元以2行(rl1和rl2)和3列(cl1,cl2和cl3)布置。其他大小的阵列也可用。例如,传感器阵列可以是32x32或80x62阵列。95.传感器阵列的像素可以包括以矩阵形式布置在衬底上的多个传感器。例如,每个像素可以包括传感器区和cmos开关或连接区。传感器区设置在例如衬底的传感器阵列区中。例如,传感器阵列区包括对应于传感器像素的多个传感器区。96.在一个实施例中,传感器单元的mems结构的第一端子耦合到开关495,第二端子耦合到公共线(com)。如图所示,传感器单元的每一列耦合到各自的com(例如,com1,com2和com3)。开关可以是具有第一和第二s/d端子以及栅极或控制极端子的晶体管。例如,开关的第一s/d端子耦合至mems结构的第一端子,并且第二s/d端子耦合至cl。rl耦合到开关的栅极或控制极端子。在一个实施例中,传感器单元的n型端子耦合至com,传感器单元的p型端子耦合至cl。将传感器单元耦合到cl和com的其他设置也可用。可以选择一个rl以选择一行传感器单元。激活cl以选择一列传感器单元。所选单元是所选rl和cl的交集。cmos组件和传感器像素之间的互连件可以通过beol电介质的ild和imd层实现。97.在一个实施例中,传感器阵列设置为读出一行传感器单元或像素。例如,一次读出阵列像素的一行。在一个实施例中,选择阵列的rl。这选择一行像素。然后选择cl,从而使得所选择的rl的像素被读出。在一个实施例中,阵列设置为从第一行到最后一行一次读出一行像素。读出的信息存储在存储器中。读出所有像素或扫描完所有行后,将生成成像仪的图像或一帧。例如,可以重建存储在存储器中的从像素读出的信息以形成图像。198.在图4c中的2×3阵列的情况下,扫描像素以形成图像可以包括选择rl1(第一行)以选择耦合到rl1的像素。选择rl1之后,选择cl1,cl2和cl3,使得耦合到rl1的像素被读出。耦合到rl1的像素信息被存储在存储器中。选择下一行或第二行rl2以选择rl2的像素。选择rl2之后,选择cl1,cl2和cl3,使得耦合到rl2的像素被读出。耦合到rl2的像素信息被存储在存储器中。由于rl2是阵列的最后一行,因此像素信息被重建以形成成像仪的图像或帧。通过重复感测,读出和重建过程,可以收集许多帧。例如,图像或帧是时间相关的。可以采用选择逻辑和输出逻辑组件选择用于输出包含信息的单元。逻辑组件可以是位于器件cmos区的cmos晶体管或组件。可以包括其他逻辑组件,包括存储器和重构逻辑组件,以存储和重构信息以形成一个或多个图像。在一实施例中,存储器和重构逻辑组件可以是片外逻辑。提供这些逻辑组件作为片上逻辑组件或片上或片外组件的组合也可用。99.图5a‑5i示出了用于形成器件的工艺的简化截面图。所述器件可以类似于图2a‑2f的器件,但没有封盖。如图所示,该截面图是例如图3所描述的器件一部分的。例如,该器件的该部分包括cmos区和mems区的mems器件区。共同元素可以不描述或不详细描述。100.参照图5a,提供了器件500。例如,已经对该器件进行了处理以在衬底501上cmos区510形成cmos组件。该器件包括衬底501。该衬底例如可以是半导体衬底,例如硅衬底。衬底例如可以是轻掺杂的p型硅衬底。其他类型的衬底或晶圆也可用。103.cmos组件可以包括pmos和nmos晶体管。诸如电阻器,电容器和二极管的其他cmos组件也可以被包括在cmos区中。cmos组件设置为包括数字和模拟电路。如图所示,cmos区510的一部分包括第一和第二晶体管。晶体管包括在s/d区514和516之间的栅极512。可以提供诸如fox或sti的隔离区以隔离cmos组件。例如,提供隔离区以将具有第一和第二晶体管的第一和第二cmos器件区隔离。102.在衬底上形成ild层520。ild层覆盖衬底和具有cmos组的cmos区。ild层例如是氧化硅层。其他类型的电介质层或电介质层的组合也可用。金属接触插塞528,例如钨插塞,提供在ild层中,并且耦合到衬底和cmos组件上的接触区。例如,接触插塞耦合到cmos组件的s/d区和栅极,以及耦合到用于偏置阱和衬底的阱抽头。为其他类型的接触区提供接触插塞也可用。103.接触插塞例如可以通过镶嵌工艺形成。例如,ild层形成在衬底上。ild层的表面可以通过例如化学机械抛光(cmp)来平坦化。图案化ild以在ild层中形成接触孔。诸如钨的金属层沉积在衬底上,填充接触开口。ild层上方的多余金属可以通过例如cmp去除,将接触插塞留在接触开口中。用于形成接触插塞的其他技术也可用。104.在ild层520上方的衬底上提供线后道工序(beol)电介质530。例如,beol电介质覆盖cmos区。beol电介质可以包括由beol电介质层形成的多个金属间电介质(imd)层。例如,beol电介质可以包括y个imd层,其中y为2–8。取决于设计和cmos工艺,也可以使用其他数量的imd层(包括1)。ild层和beol电介质可以被称为be电介质。105.imd层可以包括通孔电介质层536和金属电介质层532。imd层的通孔电介质层和金属电介质层可以由一个或多个电介质层形成,取决于设计和工艺方法。通孔电介质层可以设置在金属电介质层之上。例如,金属层(mx)可以设置在第一通孔层(vx)下方。例如,如图所示,beol包含3个imd层(x=1到3)。金属电介质层包括金属线534,通孔电介质层包括通孔接触件538。第一金属层电介质m1设置在ild层上方。beol电介质层的其他设置也可用。106.如图所示,beol电介质包含3个imd层。例如,第一imd层包括m1和v1,第二imd层包括m2和v2,并且第三或顶部imd层包括m3。在一个实施例中,m1可以通过单镶嵌技术形成。例如,可以在imd层上方形成m1电介质并且对其进行图案化以形成与m1金属线相对应的沟槽。可以在衬底上形成诸如铜或铜合金的金属层,填充沟槽并覆盖m1电介质。也可以使用其他类型的金属或合金,例如铝。通过cmp去除多余的金属,在m1电介质中保留m1金属线。使用rie工艺形成m1也可以。在rie工艺中,在ild层上形成金属层并图案化以形成m1金属线。在衬底上形成电介质层,以填充金属线之间的间隙。可以执行cmp以去除多余的电介质层。在某些情况下,电介质可以是自平坦化层,例如旋涂玻璃。107.对于m2和v1,它们可以通过双镶嵌工艺形成。例如,可以在衬底上m1上方形成电介质层。对电介质层进行图案化以形成m2的沟槽和v1的通孔开口,形成双镶嵌结构。可以使用先通孔或最后通孔双镶嵌工艺来形成双镶嵌结构。另外,可以采用多个电介质层来形成双镶嵌结构。例如,可以在m1和v1之间采用刻蚀停止层。可以在衬底上形成诸如铜或铜合金的金属层,以填充双镶嵌结构。也可以使用其他类型的金属或合金,例如铝。通过cmp去除多余的金属,使m2金属线留在v1通孔接触件上方。使用其他工艺,例如用于v1的单镶嵌和用于m2的rie组合,形成m2和v1也可用。108.m3和v2的形成可以类似于m2和v1。在其他实施例中,可以使用镶嵌工艺形成v2,使用镶嵌工艺或rie工艺形成m3。m3例如可以由铝形成。也可以使用其他类型的金属,例如铜或铜合金。109.至于m3,它可以用作焊盘层。例如,m3金属线可以用作焊盘金属线。可以在焊盘线上方形成钝化层537。钝化层例如可以包括一个或多个电介质层。在一个实施例中,钝化层包括在氧化硅层上方的氮化硅层,形成sio2/sin钝化堆叠。其他类型的钝化层或堆叠也可用。可以在钝化层提供焊盘开口以暴露焊盘线的接触焊盘。用于形成焊盘层的其他方法也可用。110.在图5b中,该过程开始形成mems层。在一个实施例中,该过程开始于在钝化层上形成基底或缓冲层539。基底层是电介质基底层,例如氧化硅。其他类型的基底层也可用。可以通过化学气相沉积形成基底层。在一个实施例中,可以通过低温工艺形成基底层。例如,缓冲层可以通过pecvd形成。其他低温工艺,例如lpcvd或apcvd也可用。基底层应足够厚,以保护下面的钝化层免受刻蚀剂(例如xef2)的腐蚀,该刻蚀剂在随后的释放工艺中用于形成下部传感器腔。111.ir反射器550形成在基底层上。ir反射器可以是金属ir反射器。例如,金属ir反射器可以由钛(ti),钨(w)或铝形成。其他类型的红外反射器也可用。为了形成ir反射器,在衬底上形成ir反射器的金属层。例如,金属层形成在基底层上。金属层可以通过例如溅射形成。用于形成金属层的其他技术也可用。图案化金属层以形成ir反射器。图案化金属层可以包括掩膜和刻蚀工艺。例如,抗蚀剂掩膜形成在金属层上方并被显影以暴露金属层要通过刻蚀工艺,例如反应离子刻蚀(rie),去除的部分。用于图案化金属层的其他技术也可用。图案化工艺例如形成用于传感器阵列的传感器的单独的ir反射器。112.在一个实施例中,如图5c所示,在衬底上形成牺牲层559。牺牲层例如是低温牺牲层。在一个实施例中,牺牲层是非晶硅(αsi)非晶层。使用低温工艺形成αsi牺牲层。例如,牺牲层是使用低温工艺,例如在低于400℃的温度下的pecvd,形成的。其他类型的低温牺牲层和/或用于形成牺牲层的低温工艺也可用。113.在一个实施例中,牺牲层的厚度用于限定传感器阵列的下部传感器腔的高度。例如,牺牲层的厚度应等于下部传感器腔的高度。例如,在下部传感器腔高1.2um的情况下,牺牲层应高约1.2um。114.参照图5d,在衬底上形成mems电介质层558。例如,mems电介质层形成在牺牲层上。在一个实施例中,mems电介质层用作用于mems区的传感器的膜层。在一个实施例中,mems电介质层是低温氧化物。例如,可以通过pecvd形成较低温度的氧化物。其他低温工艺也可以用于形成mems电介质层。115.mems结构层562形成在衬底上。例如,mems结构层形成在mems电介质层上。在一个实施例中,mems结构层是αsi层。mems结构层通过低温工艺形成。例如,mems结构层可以通过pecvd形成。116.如图5e所示,该过程开始形成mems结构。在一个实施例中,该过程开始形成用于mems器件区的热电堆结构。例如,为传感器阵列的每个mems器件区形成热电堆结构。在一个实施例中,该过程包括图案化mems结构层562以形成热电堆线结构。例如,热电堆线结构包括第一和第二线段566和568。117.所述线段掺杂有第一和第二极性类型的掺杂剂。例如,第一线段掺杂有第一极性类型的掺杂剂,例如n型,第二线段掺杂有第二极性类型的掺杂剂,例如p型掺杂。第一和第二线段的掺杂可以通过离子注入来实现。例如,使用第一注入物掩膜来掺杂第一线段来进行第一离子注入,使用第二注入物掩膜来掺杂第二线段来进行第二离子注入。替代地,可以在形成mems结构层时通过原位掺杂实现对线段的掺杂。例如,mems结构层在沉积时被掺杂。118.掺杂线段被处理以使mems结构层结晶。例如,处理线段以使αsi线段结晶。在一个实施例中,使用脉冲激光退火实现线段的再结晶。可以使用准分子激光器进行脉冲激光退火。其他类型的脉冲激光退火也可用。激光退火还激活了掺杂线段的掺杂剂。或者,采用其他技术使线段重结晶也可以。119.在热电堆结构上方形成电介质层580。电介质层例如可以是中间电介质层,其设置在mems电介质层上方并覆盖热电堆结构。在一个实施例中,中间电介质层为低温氧化物层。例如,类似于mems电介质层,通过低温工艺形成氧化物层。120.参照图5f,在连接第一和第二线段的中间层上形成接触件570。例如,形成热电堆连接桥或接触件以连接第一和第二线段。在一个实施例中,形成接触件包括在中间电介质层中形成接触开口。例如,形成第一接触开口以暴露与第二线段相邻的第一线段的邻近端,并且形成第二接触开口以暴露与第一线段相邻的第二线段的邻近端。在中间电介质层上形成诸如ti的金属层。其他类型的金属层也可用。金属层例如衬在中间电介质层的顶部和接触开口。对金属层进行图案化以形成连接第一和第二线段的连接桥。121.在线结构上形成吸收器572。例如,吸收器形成在线结构上并覆盖接触件570。在一个实施例中,吸收器形成为覆盖线结构的中心部分,包括接触件。吸收器层例如设置为吸收入射的ir辐射。吸收器可以是氮化钛(tin)吸收器。其他类型的吸收器也可用。例如,吸收器层可以是镍铬(nicr)层或掺杂的非晶硅层。在一个实施例中,吸收器设置成吸收大部分入射的ir辐射。例如,吸收器可以设置为吸收大于85%的波长为8–14μm的入射ir辐射。提供任何其他设置也可用。在其他实施例中,吸收器设置为吸收波长为2–5μm的入射辐射。例如,使用干涉式吸收器的另一谐波。在一个实施例中,吸收器设置成吸收>50%的波长为2‑5μm的入射辐射。122.为了形成吸收器,吸收器层形成在衬底上,覆盖线结构,接触件和中间电介质层。取决于吸收器层的材料,吸收器层可以通过溅射或低温工艺形成。例如,可以通过溅射形成金属吸收器层,通过低温工艺形成非晶硅层。非晶硅层可以原位掺杂或通过离子注入掺杂在沉积吸收器层之后,将其图案化以形成吸收器。123.顶部电介质层581形成在衬底上,覆盖线结构和吸收器。顶部电介质层用作线结构上方的保护层。在一个实施例中,顶部电介质层是低温氧化物。例如,通过低温工艺形成氧化物。其他类型的电介质层也可用。124.在图5g中,形成mc接触件548。mc接触件提供mems传感器到cmos区中cmos组件的电连接。mc接触件例如耦合到传感器的端子和顶部金属或焊盘层,其连接到cmos区中的cmos组件。在一个实施例中,为阵列的每个传感器提供mc接触件。例如,为每个传感器的第一和第二端子565和567提供第一和第二mc接触件。在一个实施例中,mc接触件可以耦合到cmos区中的cmos晶体管。例如,一个端子耦合至cmos晶体管的栅极,而另一端子耦合至公共线。mc接触件的其他设置也可用。125.为了形成mc接触件,可以形成mc接触通孔。例如,mc接触通孔是通过掩膜和刻蚀工艺形成的,例如使用抗蚀剂掩膜的rie。接触通孔从保护电介质层延伸到beol电介质层530的顶部金属层m3。如图所示,接触通孔在保护电介质层和中间电介质层中包括较宽的开口,以暴露线路的线结构的第一和第二端子的顶表面。例如,采用两步刻蚀,一个刻蚀形成较宽的上部,而另一个刻蚀形成较窄的下部。在一个实施例中,第一刻蚀用于形成上部,第二刻蚀用于形成下部。金属层形成在衬底上,填充接触通孔开口并覆盖暴露的端子和保护电介质层的表面。金属层例如可以是铜或铜合金。其他类型的金属层也可用。金属层可以通过电镀或溅射形成。用于形成金属层的其他技术也可用。通过cmp去除多余的金属,使顶部金属与保护层共面。去除多余金属的其他技术,例如rie,也可用。128.参照图5h,在电介质堆叠中形成释放开口582,其包括mems电介质层558及其上方的层。例如,形成通过保护层581,中间电介质层580和mems电介质层558的释放开口。例如,释放开口暴露填充一个或多个腔的牺牲层559。可以采用掩膜和刻蚀工艺来形成释放开口。例如,可以使用刻蚀掩膜采用rie以形成释放开口。用于形成释放开口的其他技术也可用。127.在图5i中,去除牺牲层,形成下部传感器腔。在一个实施例中,通过例如释放刻蚀去除牺牲层。释放刻蚀例如可以是干法mems释放刻蚀。干法mems释放刻蚀可以采用释放刻蚀,例如xef2。其他类型的释放工艺也可用。在释放刻蚀之后,mc接触件为具有传感器的mems电介质层提供机械支撑。128.该过程继续在mems区上方形成封盖。例如,封盖形成封装mems传感器的盖腔。在一个实施例中,封盖形成用于mems区的传感器的公共盖腔。例如,可以使用盖上以及mems层外部的beol电介质上的键合环将封盖键合至器件。例如,可以使用热压键合来实现键合。其他键合技术也可用。在一个实施例中,执行晶圆级真空封装以将盖晶片结合到器件晶片上。在形成封盖以封装器件之前,可以形成焊盘开口以暴露焊盘层的焊盘。焊盘例如位于盖键合区的外部。129.图6a示出了激光功率随时间的曲线图600。图6b示出了使用图6a的激光源通过激光退火模拟的结构601。例如,该结构类似于用于形成与mems传感器单片集成的cmos器件的结构。各个层的厚度被示出。图6c示出了图6b的结构的不同部分处的温度的曲线图602。如图所示,激光退火可有效地重结晶用于形成传感器线结构的非晶硅层,并激活线结构的掺杂剂,同时保持顶部金属层(m3)及其下方的结构的峰值温度小于等于350℃,并低于后cmos兼容温度。采用其他技术使线段重结晶,同时将顶部金属层(m3)及其下方的结构保持在后cmos兼容温度以内,也可以。130.如前所述,该器件将mems组件与cmos组件单片集成。在一个实施例中,通过使用低温工艺沉积诸如αsi之类的mems结构层,对层进行掺杂,使层重结晶以及使用例如准分子激光器的脉冲激光退火来激活掺杂剂,来促进cmos组件制造之后的mems组件的单片集成。激光退火能够使mems结构层重结晶并激活掺杂剂,而无需将beol电介质和ild层加热到阈值温度以上。例如,ild和beol电介质中的金属层可以保持在约350℃,这完全在后cmos工艺的热预算之内。131.在不脱离其精神或基本特征的情况下,本公开可以以其他特定形式来体现。因此,前述实施例在所有方面都应被认为是说明性的,而不是限制此处所述的发明。因此,本发明的范围由所附权利要求书而不是前述说明书来指示,并且落入权利要求书的等同含义和范围内的所有改变均旨在包含在其中。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122937.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

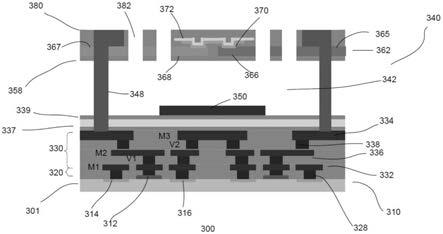

返回列表