具有在硅氮化物底切部上方的梁结构的微机电器件的制作方法

- 国知局

- 2024-07-27 12:52:05

1.本发明涉及微机电器件,其包括位于硅氮化物层中的底切部上方的释放机械结构。背景技术:2.微机电(mem)继电器可以作为一种用于添加功能并降低各种应用(例如用于物联网(iot)和可穿戴设备的传感器和消耗性器件)的功耗的器件发挥重要作用。一种类型的mems器件是机械继电器。这些器件具备具有非常突然的开关切换和在关断状态期间的零电流泄漏的准理想开关行为的能力。继电器的多端子操作也可以节约能源。例如,参见martin riverolo等人于2018年公开的“high performance seesaw torsional cmos-mems relay using tungsten via layer”。互补金属氧化物半导体(cmos)平台可用于与经典cmos器件相结合的此类mems继电器的单片制造。3.cmos mems是一种在via掩模中使用al(铝)金属化和钨(w)的化学气相沉积(cvd)来创建mems结构的技术。这种方法的一个特点是在金属层之间的二氧化硅(sio2)被用作可移除的隔离物。通常使用蒸气氟化氢(hf)或液体hf来移除sio2。一些cmos mems器件使用硅(si)(单晶或多晶)作为mems可移除层。可以使用等离子氟(f)工艺或二氟化氙(xef2)来蚀刻硅。技术实现要素:4.在所描述的示例中,一种微机电系统(mems)位于衬底上。在衬底的一部分上有硅氮化物(sin)层。机械结构具有第一端和第二端。第一端嵌入在sin层中,并且第二端从sin层悬挑出。附图说明5.图1是示例cmos集成电路芯片的一部分的横截面图,该cmos集成电路芯片包括具有形成在硅氮化物层中的梁的mems器件。6.图2是图1的mems器件的俯视截面图。7.图3a-图3f示出了图1和图2的mems器件的制造步骤。8.图4a是另一示例cmos集成电路芯片的俯视截面图,并且图4b是该cmos集成电路芯片的横截面图,该cmos集成电路芯片包括具有形成在硅氮化物层中的梁的mems器件。9.图5是另一示例cmos集成电路芯片的横截面图,该cmos集成电路芯片包括具有形成在硅氮化物层中的梁的mems器件。10.图6是示例封装mems器件。具体实施方式11.在附图中,为了一致性,相同的元件由相同的附图标记表示。12.cmos mems具有使其具有吸引力的几个特点。cmos已经相当成熟,并且模拟电路或其他电路可以与mems器件合并在同一晶圆上。cmos晶圆相对便宜并且可以用多种已知的工艺技术来制造。13.使用示例cmos工艺来制造mems的一个问题是二氧化硅(sio2)底切工艺。通常,形成sio2电介质层,然后在该sio2层上形成金属结构。通常用于底切sio2的一部分以释放金属结构的一部分以形成mems器件的湿氢氟酸(hf)蚀刻产生了限制mems结构的高应力。hf蚀刻也会腐蚀通常在cmos结构内使用的一些其他材料(如钛(ti))。蒸气hf甚至具有更强的反应性并腐蚀通常用作电介质材料的sin。这使得生成作为mems结构的一部分的电介质元件变得困难。14.示例cmos工艺也具有一个限制,因为它可能不包括mems器件(例如继电器)所需的材料。在cmos工艺中使用的导电材料(诸如w和氮化钛(tin))不会针对mems器件(诸如继电器)产生良好的接触。15.在所描述的示例中,cmos金属(例如:铝(al)、ti、tin、钛钨合金(tiw)、w、铜(cu)、钽(ta)、氮化钽(tan))可以与替代材料进行组合,这些替代材料诸如为:五氧化二钽(ta2o5)、二氧化钛(tio2)、氧化铝(a12o3)、氮化钛铝(tiain)、氮化铬(crn)、钛铝氧氮化物(tialon)、钼(mo)、氮化铝(aln)、氮化铝钪(alscn)、氧化铪锆(hfzrox)、铂(pt)、铱(ir)、氧化铱(irox)、锆钛酸铅(pb(zr,ti)o3)、铅(pd)、氧化铅(pdo)、金(au)、银(ag)、镍铁合金(nife)、铁(fe)、钴(co)、镍(ni)、钴镍铁合金(conife)、钌(ru)、氧化钌(ruo2)等,其可用于创建具有底切sin电介质的压电致动和/或继电器触点。16.这些替代材料可以通过使用sin电介质层被包含在cmos工艺中,在加工工艺期间使用化学机械抛光(cmp)步骤使sin电介质层平坦化。这使得有可能使用sin作为各层之间的电介质来创建cmos。使用碳、氟和氧气(cxfy+o2)的等离子体工艺被用于提供sin的选择性气体移除,但不会腐蚀这些金属和电介质中的大部分。例如,等离子体四氟化碳加氧气(cf4+o2)为sin提供了很强的蚀刻速率,而仅微弱地蚀刻sio2。这种选择性适用于大多数其他材料,但是存在w、mo和ru或ruo2的一些腐蚀。使用具有低衬底偏差的下游等离子体。该工艺类似于用于灰化抗蚀剂的工艺。这种等离子体工艺以几乎各向同性的方式蚀刻sin。对于mems结构的底切蚀刻,这是一个有用的特点。与需要定向蚀刻来产生通孔的via蚀刻相比,这是一种完全不同的蚀刻工艺。17.在所描述的示例中,sio2和许多其他电介质(诸如al2o3、ta2o5、tio2)可用于创建不受等离子体蚀刻底切工艺强烈腐蚀的电介质特征。18.图1是cmos集成电路芯片的一部分的横截面图,该cmos集成电路芯片包括具有形成在硅氮化物层104中的梁120的mems器件100。图2是图1的mems器件的俯视截面图。在该示例中,梁120是mems器件100的一部分。此图示出了具有两层的简单悬臂梁的图示。底层是w 120。该层是使用典型的w via镶嵌工艺流程形成的。via图案针对每个通孔具有最大空间,但网状结构可用于创建大型特征部。可能会或可能不会停止在另一图案化层上的sin蚀刻用于更好地定义厚度。然后蚀刻并清洁沟槽以移除留下的抗蚀剂和可能存在的任何残留物。下一步是沉积ti粘附和阻挡层105,其通常是cvd tin(实际上是ticon)。这些阻挡材料可以是其他材料,例如ta、tan、ru等。然后用cvd w填充沟槽,并且然后使用cmp移除沟槽外部的w。cmp或后续的清洁移除粘附/阻挡层(ti/tin)105。由于需要保护w免受sin底切蚀刻,它需要受到未蚀刻材料的保护。该图中所示的一种技术是使用层132,在该示例中该层为tin上的al。在实践中,层132可以是不会被sin底切蚀刻工艺快速腐蚀的其他金属或电介质材料。用于132的示例电介质材料是alox、aln、sio2、tao、tio2。可以利用蚀刻工艺使用另一个掩模来图案化该层。另一种选项是使其成为自对准保护层。该工艺通常以w凹陷蚀刻法(干法或湿法)开始,该蚀刻法相对于sin更快地移除w。然后沉积保护性绝缘或导电阻挡层,并且然后使用cmp或回蚀工艺移除sin上方的层。以这种方式,无需使用额外的掩模步骤即可保护w。一个关键点是,这些材料在底切蚀刻工艺中的蚀刻速度比sin慢得多。19.虽然该图显示了创建悬臂,但实际上,多个图案化和未图案化的层可以位于已使用底切工艺创建的mems层的下方或上方。这些附加层可用于创建可使用这种方法创建的各种mems器件。20.在该示例中,在衬底102上方形成sin层104,在该示例中衬底102为硅(si)。为简单起见,仅图示了衬底102的小的上部分。众所周知,cmos工艺通常在硅的薄外延层中加工有源器件,该外延层被形成在硅的体晶圆的顶部上。此外,为简单起见,该示例未按比例绘制。梁120明显比其厚度长。典型的via厚度121是在cmos器件中使用的厚度,通常在0.1μm到大约5μm之间。该示例中的总梁厚度是via厚度加上层132之上或层120之下的任何附加层(未在该图中示出)。释放的梁长度124通常比其宽度长得多,其典型的纵横比(长度比高度)为5比1或甚至更大。例如,如果梁的厚度121为1μm,则梁120的释放部分124通常比5μm长得多。在其他示例中,这种梁的释放部分可以长于20μm并且可能长于甚至100μm,这取决于材料和横截面设计。悬臂梁特征部120的总长度122总是长于释放的梁长度124,使得仍有合理的长度125嵌入剩余的sin 104中。21.在该示例中,梁120由具有tin的薄衬层的钨(w)加工成。使用已知的化学气相沉积(cvd)技术在镶嵌式工艺中沉积钨和tin,并且对w和tin的cmp被用于移除不需要的金属。在已通过底切蚀刻工艺移除sin之后,tin还充当扩散阻挡层以及用于w的蚀刻保护层。未示出ti薄层,它通常用作粘附层,也用于创建至该结构下方的金属的较低阻抗电连接。通常使用电离金属等离子体通过定向溅射沉积来沉积ti,以便在via类型特征部的底部上实现金属薄层。镶嵌是在铁、钢、青铜或黄铜表面上装饰金、银或铜线的技术。用凿子在金属的表面中做出狭窄的底切部,然后借助于锤子将金属丝压入底切部中。在该示例cmos工艺中,cmp工艺被用于在cvd工艺之后移除不需要的钨,如下文更详细描述的那样。这需要平坦的表面,因此要么表面没有被图案化,要么在w图案化步骤之前已使用cmp使其变平坦。虽然这类似于在cmos工艺中所做的操作,但在这种情况下,w在底部和侧面被sin层103而非sio2包围。22.在镶嵌工艺中,首先将电介质层沉积到衬底上。然后通过金属沉积对电介质层进行图案化和填充。双镶嵌工艺的特点是对通孔和沟槽进行图案化,使金属沉积物同时填充两者,同时在通孔和沟槽之间留下间隙区域。梁120的镶嵌工艺使用现有的层间电介质,其中蚀刻用于传导路径的通孔和沟槽。在这种情况下,电介质层103是sin并且用于梁120的金属是钨。在另一示例中,用于梁120的金属可以选自其他金属,诸如tiw。23.在该示例中,w或tiw被用于创建mems梁结构120并提供低蠕变率。在这种情况下,蠕变是梁在受到时间和温度以及可能的附加应力影响后变形的变化。典型的产品时间/温度是10年、85℃、105℃、125℃或150℃。有些产品需要更长的时间或甚至更高的温度。应力取决于应用。即使没有添加的外部应力,也总是有可能导致梁改变位置的内置内部应力。许多器件要求梁位置(横向和垂直)在不受外部应力时不改变。当然,梁总是具有弹簧常数,并且在应力下确实会弯曲。w的厚度被选择为为梁120提供大于大约75%的刚度,因此其他材料的缓慢蠕变不会衰减整个mems结构的特性。在所示示例中,tin的薄层105围绕梁120,并且铝导体132在梁120的顶部上被图案化。众所周知,铝具有高蠕变率,但如果w具有小的相对蠕变并且是梁刚度的主导部分,则整个梁或mems结构将不会移动太多。在该示例中,al层不仅可用于保护梁中的w的顶部免受sin底切蚀刻,而且还可用作与梁的电接触。a1层也可以位于梁的底部上并作为梁的蚀刻停止层。在各种示例中,该al层通常还包括其他材料,例如ti、tial、tin。在各种示例中,可以根据特定功能的需要存在其他材料。24.在sin层104和诸如al导体132的各种其他元件上形成牺牲sin层134。sio2电介质层136形成在sin层134的顶部上。开口138在电介质层136中被图案化以引导底切工艺。层136可以是多个层或者甚至是不同于sio2的其他材料,诸如alox、sion。25.使用四氟化碳加氧气(cf4+o2)形成底切区域140以提供对sin的强蚀刻速率,同时仅弱蚀刻sio2蚀刻停止层103和sio2顶部电介质层136。在实践中,该工艺需要等离子体活化的氟加氧气。针对氟(f)存在多种选项,如sf6或其他碳氟化合物,加上f2、nf3、hf等。对于o2来源,还存在多个选项,诸如h2o、o3、no2、co2等。cf4+o2的列表是一种已证明良好结果的常见工艺,但确实存在使用这些替代化学物质的其他工艺。如图1和图2所示,底切区域140的一部分141延伸穿过梁120的释放部分124的底部并向上延伸到梁120的部分124的侧面。sin层134的一部分142也被蚀刻掉。区域140、141、142一起是sin层104、134中的腔体区域,梁120的一部分悬臂式伸入腔体区域中。以这种方式,梁120的悬臂式释放部分124与sin层104、134分离并且因此可以响应于诸如静电力的力而移动。梁120的另一部分125仍然牢固地嵌入和锚定在sin层104中。以这种方式,梁120可以用作mems器件100的一部分。26.图3a-图3f示出了图1和图2的mems器件100的制造步骤。包含数十或数百个器件的整个晶圆300被制造为一个单元。为简单起见,仅图示了晶圆300的衬底302的小片上部分。27.在图3a处,在该示例中,sio2层303形成在衬底302上方,在该示例中衬底302是硅(si)。在该示例中,cmos工艺通常在形成在大块硅晶圆的顶部上的薄外延硅层中制造有源器件。在底切工艺期间,sio2层303将充当蚀刻停止层。然后在sio2层303上方形成sin层304。sin层304足够厚以允许在其中形成梁120(图2)。28.可能需要一个或多个沉积步骤来实现sin层304的足够厚度。本文使用硅氮化物的通用术语“sin”来指代任何不同形式的硅氮化物,诸如si3n4、si(x)n(y)h(z)等。在该示例中,sin层具有sioxnycz的成分,其中o小于0.1,并且c小于0.3,而n构成除si之外的材料的剩余部分。氢(h)符号通常从化学式(例如,sin)中省略,但通常存在于包括金属在内的许多此类材料中。29.在该示例中,使用化学气相沉积(cvd)工艺或等离子体增强化学气相沉积(pecvd)来沉积sin层104。化学气相沉积是一种在加热的衬底表面处使用热诱导的化学反应的涂覆工艺,其中试剂以气态形式供应。最常见的cvd或pecvd硅氮化物通常包含高达8%的氢。沉积sin的其他方法是溅射沉积或电子蒸发,但这不太常见。30.在sin层304的沉积完成之后,通常使用化学机械抛光(cmp)工艺使晶圆表面变平坦。如果下面存在已引入形貌的层,则这是必要的。cmp工艺使用与抛光垫和固持环相结合(其通常具有大于晶圆的直径)的研磨和腐蚀性化学浆料(通常是胶体)。抛光垫和晶圆由动态抛光头压在一起,并由固持环保持就位。动态抛光头以不同的旋转轴线旋转(即不同心)。这移除了材料并趋于使任何不规则的形貌变平,从而使晶圆的顶表面3041变平坦,也被称为是“平面的”。31.在图3b处,使用已知或后来开发的蚀刻技术对表面3041进行图案化和蚀刻以在sin层304内形成沟槽306。然后在晶圆上方沉积tin薄层305。该tin层涂覆沟槽306的底板和壁。32.在图3c处,钨层307被沉积在晶圆的表面上方并进入腔体306。钨层307粘附到tin层305。33.在图3d处,已执行另一cmp步骤以移除除了沟槽306内之外的各处的钨层307。以此方式,在sin层304内形成梁320。如上所述,这是一种镶嵌式工艺。使用cmp移除这些层的替代方法是回蚀工艺。34.tin层330被沉积在晶圆300的表面上方。然后在晶圆300的表面上方沉积铝层。然后沉积、图案化并蚀刻牺牲层(未示出)以形成铝导体332,该铝导体332形成mems继电器器件100(图1)的触点。35.然后在晶圆300的表面上方沉积另一sin层334,随后进行cmp工艺以平坦化晶圆300的表面3042。36.在图3e处,sio2电介质层336沉积在晶圆300的平坦化表面上方。然后牺牲层(未示出)被沉积、图案化和蚀刻以形成开口338和339。开口338将引导围绕梁320的底切工艺。开口339将引导蚀刻工艺形成通孔以接触铝导体332。尽管为简单起见仅图示了两个开口,但为与晶圆300上的其他特征部(未示出)的各种接触点制作了其他开口。37.在图3f处,晶圆300通过开口338、339暴露于四氟化碳加氧气(cf4+o2)等离子体350、351,从而为sin层304、334提供强蚀刻速率,同时仅弱蚀刻sio2蚀刻停止层303和sio2顶部电介质层336。以此方式,形成底切区340和接触区域343。底切区域340的一部分341延伸跨过梁320的释放部分324的底部并向上延伸到梁320的一部分324的侧面。sin层334的一部分342也被蚀刻掉。区域340、341、342一起是sin层304、334中的腔体区域,梁320的一部分悬臂式伸入该腔体中。梁320的释放部分324与sin层304、334分离以形成释放的机械结构并且因此可以响应于诸如静电力的力而移动。梁320的另一部分325仍然牢固地锚定在sin层304中。以这种方式,例如,梁320可以用作mems继电器中的谐振器或支撑梁的一部分。38.尽管本文中没有描述,但也可以使用已知的或以后开发的集成电路加工技术在晶圆300上加工各种cmos晶体管。完成后,晶圆300被锯切或以其他方式分离成独立芯片(也被称为管芯)。然后将独立的管芯附接到引线框架并使用已知或后来开发的ic封装技术(诸如用模塑料模制)进行包封,以提供与cmos电路系统集成的封装mems器件。39.图4a是另一示例cmos集成电路芯片的一部分的俯视截面图,并且图4b是它的横截面图,该cmos集成电路芯片包括具有形成在硅氮化物层404、434中的梁420的mems器件400。在该示例中,梁420被加工成具有被蚀刻穿过梁420的一部分424的通孔和槽的矩阵,如总体由427所指示。通孔和槽的矩阵427导致具有分布在整个梁部分424中的间隙空间426的互连金属构件的矩阵427。最初,间隙空间426将被从sin层404剩余的sin的sin来填充。换言之,梁部分424的互连金属构件427类似于华夫饼(waffle)图案。40.mems器件400以与图3a-图3f所示类似的方式来加工,但添加了加工通孔426和槽427的步骤。参考图4b,在图3f中描述的等离子体蚀刻工艺期间,在其上加工mems器件400的晶圆通过开口438、439暴露于四氟化碳加氧气(cf4+o2)等离子体450、451,从而为sin层404、434提供强蚀刻速率,同时在衬底402和sio2顶部电介质层436上仅弱蚀刻sio2蚀刻停止层403。在另一示例中,有可能替换或添加其他电介质(如al2o3),以进一步减少电介质的蚀刻。此外,可以在mems梁上方和下方使用不被sin底切蚀刻工艺强烈腐蚀的金属,只要sin在这些新结构层上方和下方即可。以此方式,形成底切区域440和接触区域443。底切区域440的一部分441延伸跨过梁420的一部分424的底部并向上延伸到梁420的该部分424的侧面。sin层434的一部分442也被蚀刻掉,使得梁420的该部分424与sin层404、434分离以形成释放的机械结构并且因此可以响应于诸如静电力的力而移动。梁420的另一部分425仍然牢固地锚定在sin层404中。以这种方式,梁420可以用作mems继电器。41.在这种情况下,等离子体蚀刻450从间隙空间426中移除sin,然后通过间隙空间426扩散以形成底切区域441的部分。以这种方式,可以在梁下方形成大面积的底切区域441,该区域比可能在诸如梁120(图1)的实心梁下方形成的底切区域更大。42.图5是另一示例cmos集成电路芯片的一部分的横截面图,该cmos集成电路芯片包括具有形成在硅衬底502上的(一个或多个)硅氮化物层504、534中的释放机械结构520的mems器件500。在该示例中,w via特征部520在除顶部外的所有侧面上都被cvd tin 505包围,并且最初嵌入在图案化金属特征部上的sin焊盘中。在该示例中,底部图案化特征部包含铱(ir)层560,该ir层在制造工艺中位于梁520的底部上。底部图案化特征部可以由不被sin底切蚀刻强烈腐蚀的任何电介质材料或金属材料制成。在该示例中,底层由ir 560的顶部上的tiain层561组成。在该示例中,ir 560位于移动的mems梁520的底部上。这可能用作此图中未示出的底层的顶部触点以创建继电器,其中当梁向下弯曲以与该示例中未移动的底部电极建立电连接时,继电器闭合。如前所述,w顶部的sio2 536保护w免受sin底切蚀刻工艺的影响。如果需要,cvd tin可以保护侧面和底部上的w。在这种情况下,该保护性顶层在sin底切工艺之前被图案化和蚀刻。43.在该示例中,使用碳、氟和氧气的等离子体(cxfy+o2)加工底切区域540,以通过电介质sio2层536中的开口提供对sin层503、534的选择性气体移除并且不腐蚀ir层560或蚀刻停止sio2层503。44.图6是示例封装mems器件600。在该示例中,集成电路芯片671是使用已知的或后来开发的cmos制造技术制造的。cmos电路672形成在ic 671中并且包括cmos晶体管、无源器件和互连导体。一个或多个mems器件673被形成在ic 671中。mems器件673可以类似于器件100(图1)、400(图4a、4b)、500(图5)或使用等离子体蚀刻工艺在sin层内制造的其他mems器件中的任何一种,如上文更详细描述的那样。45.ic 671附接到包括触点674的引线框架670。键合线675使用已知或后来开发的线键合技术将ic 671上的键合焊盘连接到触点674。46.模塑料676使用已知或后来开发的包封技术来包封ic 671。在该示例中,完成的mems器件600被封装为表面贴装器件。47.其他示例48.在所描述的示例中,在3个侧面上由cvd tin保护的cvd钨被用于在sin内形成梁结构。顶侧面可以通过另一图案化和蚀刻层或通过自对准工艺(如凹陷w,然后形成阻挡金属(如tin)并利用更多cmp)来保护。在其他示例中,例如,钛、ta、tiw、tin、tan的物理气相沉积(pvd)可用于在sin内形成梁结构。在每种情况下,使用碳、氟和氧等离子体来底切sin对其他材料的影响较小。sin比sio2更强并且具有更高的热导率。49.sin底切蚀刻导致清洁的表面,其中残留的碳或氟可以使用利用h2、h2o、o2、n2、nh3、no等的等离子体或蒸汽清洁工艺来移除。50.在所描述的示例中,w被用于低蠕变材料。然而,还有其他低蠕变材料,其示例被包括在表1中。表1中的所有材料都具有1500℃以上的极高熔化温度,其中大多数具有2000℃以上的熔化温度。半导体工艺中通常使用的符合低蠕变材料的材料有c、ta、mo、ir、ru、ti和pd。此外,tin或tan等化合物也可作为高熔点和低蠕变材料。包括常用的w合金(如tiw和niw)在内的合金也具有高熔点和低蠕变。除了少数例外,表1中列出的大多数材料通常不用于cmos工艺,因此没有用于沉积、蚀刻和清洁的完善的材料处理设施。这些材料中的大多数可以通过溅射沉积来沉积,并且因此需要通过图案化和蚀刻工艺而不是所描述的示例中讨论的镶嵌工艺来图案化。这些材料中的一些将通过sin底切蚀刻工艺进行蚀刻,因此需要加以保护。这可以使用堆叠的顶部和底部处的保护层(诸如,ta或甚至是一层薄的sio2、tin、al或alox)来完成。如有必要,还可以通过沉积保护材料(cvd tin、alox)来保护侧面,然后进行回蚀工艺以移除平坦暴露表面上的材料。使用蚀刻工艺而不是镶嵌工艺来创建梁的一个优点是可以创建实心梁。51.表1-示例低蠕变材料[0052][0053]在所描述的示例中,描述了可以用作继电器的简单梁结构。在所描述的示例中,描述了具有大致矩形形状的梁。在其他示例中,可以使用本文所述的等离子体蚀刻工艺在sin内形成更复杂的结构。这些结构可用于极其广泛的不同mems结构。与等离子蚀刻底切工艺兼容的多种材料可用于创建可能的多种类型器件。这些可以是使用静电、磁、压电、热来创建致动器的简单结构。诸如pt、ir、w、ru、mo、ti之类的高温金属可用于创建具有多种应用(诸如气体流量传感器、ir源)的高温加热器。具有这些的mems结构可用于创建谐振器、ir探测器、热探测器。具有可靠接触材料的电气结构(诸如继电器或rf开关)是可能的。可以使用如本文所述的柔性梁来制作可变电容器器件。[0054]在所描述的示例中,梁的一部分从sin层释放,而另一部分仍然嵌入在sin层中。在其他示例中,可以制造在sin层中没有剩余部分的释放的机械结构。在一些示例中,释放的机械结构可以由附接到sin层的扭力杆或类似的支撑机构支撑。如本文所用,术语“机械结构”指代各种形状和尺寸的完全和部分释放的结构。[0055]在所描述的示例中,悬臂梁定位在sin层中的腔体内。在其他示例中,sin层可以被配置为使得它不完全包围悬臂式机械结构。例如,机械结构上方可能没有顶层。在另一示例中,可以移除sin层的大部分,在这种情况下,悬臂式机械结构可以从sin层的边缘突出到基本上开放的空间中。[0056]在所描述的示例中,完成的封装器件是在封装件的底侧上具有多个触点的表面贴装器件。然而,在其他示例中,ic封装件可以具有任何数量的已知或以后开发的配置,并且可以具有各种形式、材料、形状、尺寸、触点数量、触点形状等。此外,mems谐振器和/或任何其他部件可以以各种配置被封装、安装等在ic封装件中。ic封装件的其他示例包括晶圆级封装件和管芯级封装件。[0057]许多器件利用环氧树脂塑料来封装,该环氧树脂塑料充分保护半导体器件并具有支撑引线和封装处理的机械强度。一些集成电路具有无引线封装,诸如四方扁平无引线(qfn)和双扁平无引线(dfn)器件,它们将集成电路物理耦合和电耦合到印刷电路板。扁平无引线器件(也被称为微引线框架(mlf)和小外形无引线(son)器件)是基于表面贴装技术,该表面贴装技术无需印刷电路板中的贯通孔而将集成电路连接到印刷电路板的表面。在封装件上的周边焊盘提供与印刷电路板的电耦合。另一示例可以包括完全包封在模塑料中的封装件,诸如双列直插式封装件(dip)。[0058]在本说明书中,术语“耦合”及其派生词意指间接、直接、光学和/或无线电连接。因此,如果第一器件耦合到第二器件,该连接可以是通过直接电连接、通过经由其他器件和连接件的间接电连接、通过光电连接和/或通过无线电连接。[0059]在权利要求的范围内,对所描述的实施例进行修改是可能的,并且其他实施例也是可能的。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123838.html

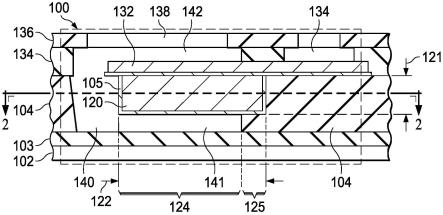

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表