电子器件及制备方法、测试电路及制备方法、测试方法

- 国知局

- 2024-07-27 13:00:30

本公开涉及电子器件,尤其涉及电子器件及制备方法、测试电路及制备方法、测试方法。

背景技术:

1、电极尺寸的缩减,是构筑先进节点半导体器件及其它小尺寸电子器件的关键基础。不同于数十至数百纳米器件中本征的电子发射特性,当电极间距缩减至单分子或者原子尺寸时,电极之间的量子、原子特性等将逐渐主导载流子输运过程,从而为低功耗、高密度的先进节点电子器件的制造及集成提供新的可能。但是,这些输运过程往往共存并相互干扰,影响了器件性能的提升。因此目前亟需发展在亚10纳米电极内可控调节载流子输运过程的技术。

技术实现思路

1、为了解决上述技术问题中的至少一个,本公开提供了电子器件及制备方法、测试电路及制备方法、测试方法。

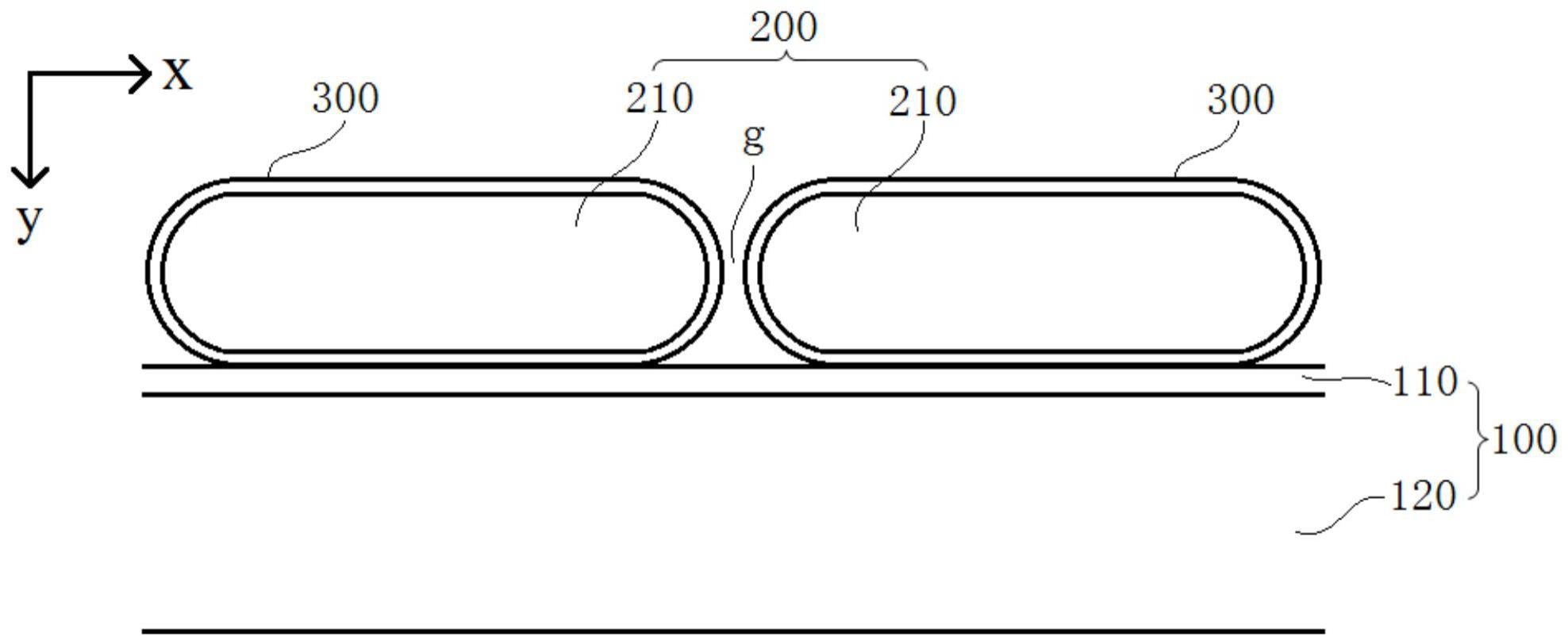

2、本公开第一方面提出了一种电子器件,包括:基底;形成于所述基底表面的纳米电极对,其中,所述纳米电极对包括至少两个纳米电极,所述两个纳米电极之间具有纳米间隙,所述两个纳米电极相向地布置;以及包覆于所述两个纳米电极表面的包覆层,所述包覆层被构造为阻碍所述两个纳米电极之间的原子迁移。

3、本公开第二方面提出了一种电子器件的制备方法,所述制备方法适于制备如上述第一方面中任一实施方式所述的电子器件,所述制备方法包括:先通过液相合成方法在溶液中合成具有包覆层的纳米电极,然后利用纳米电极的自组装特性使得溶液相的纳米颗粒在基底表面形成自组装阵列,或者,先利用纳米电极的自组装特性使得溶液相的纳米颗粒在基底表面形成自组装阵列,然后通过原子层沉积技术或真空蒸镀工艺使包覆层沉积在纳米电极上;以及在非共价键的相互作用下,在同一所述电子器件的两个纳米电极之间形成纳米间隙。

4、本公开第三方面提出了一种电子器件的测试电路,包括:多个如上述第一方面中任一实施方式所述的电子器件,所述多个电子器件包含的所有纳米电极中包括有至少一种形貌并且包括有至少一种包覆层;以及形成于所述电子器件的基底表面的引线,所述引线的一端与所述纳米电极的外侧一端连接,所述引线的另一端与测试台连接,以便于通过所述测试台对所述电子器件进行电学测试,得到对应于至少一种形貌和包覆层的电子器件的原子迁移电学数据。

5、本公开第四方面提出了一种测试电路的制备方法,所述制备方法适于制备如上述第三方面中任一实施方式所述的电子器件的测试电路,所述制备方法包括:通过如上述第二方面中任一实施方式所述的电子器件的制备方法制备得到电子器件;以及通过微纳加工的方式在所述电子器件的基底表面形成多条引线,其中,所述电子器件中的每个纳米电极外侧一端与所述引线的一端连接,所述引线的另一端与测试台连接。

6、本公开第五方面提出了一种测试电路的测试方法,所述测试方法适于对如上述第三方面中任一实施方式所述的电子器件的测试电路进行电学测试,所述测试方法包括:通过测试台对所述测试电路中的电子器件进行电流传输特性的测试,得到对应于至少一种形貌和包覆层的电子器件的电流传输特性;以及依据测试得到的电子器件的电流传输特性确定符合要求的纳米电极形貌和包覆层的类型。

7、本公开第六方面提出了另一种电子器件,包括:基底;以及,形成于所述基底表面的纳米电极对,其中,所述纳米电极对包括至少两个纳米电极,所述两个纳米电极之间具有纳米间隙,所述两个纳米电极相向地布置;其中,所述基底表面形成有凹槽,所述凹槽位于所述纳米间隙下方,且所述凹槽的宽度不小于所述纳米间隙的宽度。

8、本公开第七方面提出了另一种电子器件的制备方法,所述制备方法适于制备上述第六方面中任一实施方式所述的电子器件,所述制备方法包括:先通过液相合成方法在溶液中合成纳米电极,然后利用纳米电极的自组装特性使得溶液相的纳米颗粒在基底表面形成自组装阵列;在非共价键的相互作用下,在同一所述电子器件的两个纳米电极之间形成纳米间隙;以及在所述基底上进行刻蚀形成位于所述纳米间隙下方的凹槽。

9、本公开第八方面提出了另一种电子器件的测试电路,包括:多个如上述第六方面中任一实施方式所述的电子器件,其中,所述多个电子器件包含的所有纳米电极中包括有至少一种形貌,并且所述多个电子器件包含所有基底的凹槽中包括有至少一种凹槽形态和凹槽尺寸;以及形成于所述电子器件的基底表面的引线,所述引线的一端与所述纳米电极的外侧一端连接,所述引线的另一端与测试台连接,以便于通过所述测试台对所述电子器件进行电学测试,得到对应于至少一种形貌、凹槽形态和凹槽尺寸的电子器件的原子迁移电学数据。

10、本公开第九方面提出了另一种测试电路的制备方法,所述制备方法适于制备如上述第八方面中任一实施方式所述的电子器件的测试电路,所述制备方法包括:通过如上述第七方面中任一实施方式所述的电子器件的制备方法制备得到电子器件;以及通过微纳加工的方式在所述电子器件的基底表面形成多条引线,其中,所述电子器件中的每个纳米电极外侧一端与所述引线的一端连接,所述引线的另一端与测试台连接。

11、本公开第十方面提出了另一种测试电路的测试方法,所述测试方法适于对如上述第八方面中任一实施方式所述的电子器件的测试电路进行电学测试,所述测试方法包括:通过测试台对所述测试电路中的电子器件进行电流传输特性的测试,得到对应于至少一种形貌、凹槽形态和凹槽尺寸的电子器件的电流传输特性;以及依据测试得到的电子器件的电流传输特性确定符合要求的纳米电极形貌和凹槽形态的类型以及凹槽尺寸。

12、本公开第十一方面提出了又一种电子器件,包括:基底;形成于所述基底表面的纳米电极对,其中,所述纳米电极对包括至少两个纳米电极,所述两个纳米电极之间具有纳米间隙,所述两个纳米电极相向地布置;以及,包覆于所述两个纳米电极表面的包覆层,所述包覆层被构造为阻碍所述两个纳米电极之间的原子迁移;其中,所述基底表面形成有凹槽,所述凹槽位于所述纳米间隙下方,且所述凹槽的宽度不小于所述纳米间隙的宽度。

13、本公开第十二方面提出了又一种电子器件的制备方法,所述制备方法适于制备如上述第十一方面中任一实施方式所述的电子器件,所述制备方法包括:先通过液相合成方法在溶液中合成具有包覆层的纳米电极,然后利用纳米电极的自组装特性使得溶液相的纳米颗粒在基底表面形成自组装阵列,或者,先利用纳米电极的自组装特性使得溶液相的纳米颗粒在基底表面形成自组装阵列,然后通过原子层沉积技术或真空蒸镀工艺使包覆层沉积在纳米电极上;在非共价键的相互作用下,在同一所述电子器件的两个纳米电极之间形成纳米间隙;以及在所述基底上进行刻蚀形成位于所述纳米间隙下方的凹槽。

14、本公开第十三方面提出了一种电子器件的测试电路,包括:多个如上述第十一方面中任一实施方式所述的电子器件,所述多个电子器件包含的所有纳米电极中包括有至少一种形貌并且包括有至少一种包覆层,并且所述多个电子器件包含所有基底的凹槽中包括有至少一种凹槽形态和凹槽尺寸;以及形成于所述电子器件的基底表面的引线,所述引线的一端与所述纳米电极的外侧一端连接,所述引线的另一端与测试台连接,以便于通过所述测试台对所述电子器件进行电学测试,得到对应于至少一种形貌、包覆层、凹槽形态和凹槽尺寸的电子器件的原子迁移电学数据。

15、本公开第十四方面提出了一种测试电路的制备方法,所述制备方法适于制备如上述第十三方面中任一实施方式所述的电子器件的测试电路,所述制备方法包括:通过如上述第十二方面中任一实施方式所述的电子器件的制备方法制备得到电子器件;以及通过微纳加工的方式在所述电子器件的基底表面形成多条引线,其中,所述电子器件中的每个纳米电极外侧一端与所述引线的一端连接,所述引线的另一端与测试台连接。

16、本公开第十五方面提出了一种测试电路的测试方法,所述测试方法适于对如上述第十四方面中任一实施方式所述的电子器件的测试电路进行电学测试,所述测试方法包括:通过测试台对所述测试电路中的电子器件进行电流传输特性的测试,得到对应于至少一种形貌、包覆层、凹槽形态和凹槽尺寸的电子器件的电流传输特性;以及依据测试得到的电子器件的电流传输特性确定符合要求的纳米电极形貌、包覆层和凹槽形态的类型以及凹槽尺寸。

本文地址:https://www.jishuxx.com/zhuanli/20240726/124515.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表