半导体器件封装及制造其之方法与流程

- 国知局

- 2024-07-27 13:02:58

本发明涉及一种半导体器件封装,及更具体地涉及一种半导体器件封装,其包括具有一空气释放结构之一基板。

背景技术:

1、微机电系统(mems)芯片可包括膜和盖。mems芯片的盖可经由粘胶附接到基板以形成半导体封装。在制造过程中,可加热半导体封装以固化盖和基板之间的粘胶。然而,热循环可能导致半导体封装内的空气膨胀,因而可能损坏膜。

技术实现思路

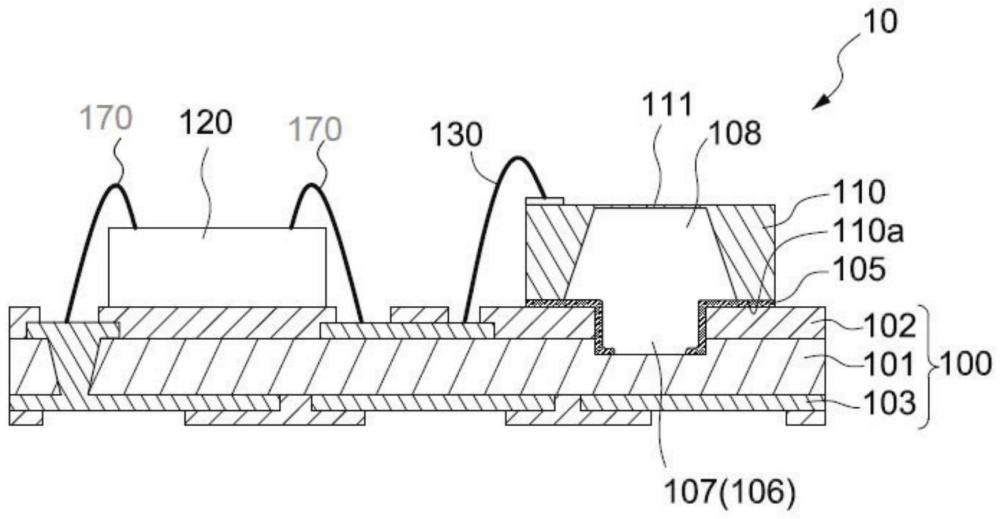

1、在一些实施例中,根据一态样,一种半导体器件封装,其包括具有一第一凹槽的一基板及一半导体器件。该第一凹槽具有一第一部分、一第二部分及一第三部分,该第二部分位于该第一部分与该第三部分之间。该半导体器件设置在该第一凹槽的该第二部分上。该半导体器件包括一膜且具有与该基板相邻且相对于该膜的一第一表面。该膜由该第一表面暴露。

2、在一些实施例中,根据另一态样,一种载体,其包括一核心层、在该核心层上的一半导体器件安装区域及设置在该核心层上且从该核心层暴露的一第一凹槽。该第一凹槽跨越该半导体器件安装区域。

3、在一些实施例中,根据另一态样,揭示一种用于制造半导体器件封装的方法。该方法包含:提供一载体,一半导体器件安装区域界定于该载体上;在该载体上形成一凹槽,该凹槽从该载体暴露且跨越该半导体器件安装区域;及经由一粘合剂将包括一膜的一半导体器件附接到该载体的该半导体器件安装区域以形成该半导体器件封装。

技术特征:1.一种半导体器件封装,其包含:

2.根据权利要求1所述的半导体器件封装,其中该第一凹槽经配置以将空气从该半导体器件的内部释放到该半导体器件的外部。

3.根据权利要求2所述的半导体器件封装,其中该基板还具有一第二凹槽,且其中该第一凹槽包括从该半导体器件暴露出来的第一部分及第二部分,该第二凹槽包括从该半导体器件暴露出来的第三部分。

4.根据权利要求3所述的半导体器件封装,其中该第一凹槽的该第一部分或该第二部分的经暴露长度不同于该第二凹槽的该第三部分的经暴露长度。

5.根据权利要求1所述的半导体器件封装,其中该基板进一步具有由该半导体器件覆盖的一空腔,且该第一凹槽与该空腔相连接。

6.根据权利要求5所述的半导体器件封装,其中该基板还具有一第二凹槽,该第二凹槽与该第一凹槽透過該空腔相连通且彼此相互正交,其中该第一凹槽的长度不同于该第二凹槽的长度。

7.根据权利要求1所述的半导体器件封装,其中该基板还具有一第二凹槽,其中对于由该半导体器件所覆盖的区域,该第一凹槽与该第二凹槽的配置以该第二凹槽为参考轴作对称,而该第一凹槽与该第二凹槽的配置以该第一凹槽为参考轴作非对称。

8.一种半导体器件封装,其包含:

9.根据权利要求8所述的半导体器件封装,其中该半导体器件经由一接合导线与该第一导电层直接连接。

10.根据权利要求9所述的半导体器件封装,其中该接合导线的一端高于该半导体器件的膜,且该接合导线的另一端低于该半导体器件的底表面。

11.根据权利要求8所述的半导体器件封装,其中该第一导电层被该第一绝缘层至少部分地覆盖。

12.根据权利要求8所述的半导体器件封装,其中该基板进一步包含设置于该核心层的一下表面上的一第二绝缘层及一第二导电层,且该第二导电层被该第二绝缘层至少部分地覆盖而从该第二绝缘层部份地暴露。

13.根据权利要求8所述的半导体器件封装,其中在一截面上,该第一绝缘层具有未与该半导体器件重迭且未与该第一导电层重迭的一部分。

14.一种半导体器件封装,其包含:

15.根据权利要求14所述的半导体器件封装,其中在一截面上,该半导体器件封装包含设置该mems器件的一第一区、设置该半导体器件的一第二区、以及设置在该第一区与该第二区之间的一第三区,其中该第一区中的該绝缘层之第一部分与该第三区中的該绝缘层之第二部分为不连续。

16.根据权利要求15所述的半导体器件封装,其中该第二区中的該绝缘层之第三部份是在该半导体器件与该核心层之间。

17.根据权利要求14所述的半导体器件封装,其中该半导体器件经由一第一接合导线与该导电层电连接,且该接合导线的一端低于该mems器件的一膜且高于该mems器件的一底表面,该接合导线的另一端低于该mems器件的该底表面。

18.根据权利要求17所述的半导体器件封装,其中该mems器件经由一第二接合导线电连接至该导电层,该半导体器件经由该第二接合导线与该mems器件电连接。

19.根据权利要求14所述的半导体器件封装,其进一步包含一黏合剂,其与该绝缘层的一上表面及一侧表面接触。

20.根据权利要求14所述的半导体器件封装,其中在該截面上该mems器件下方的绝缘层与该半导体器件下方的绝缘层彼此间是不连续的。

技术总结本发明的至少一些实施例涉及一种半导体器件封装及制造其之方法。该半导体器件封装包括具有一第一凹槽和一半导体器件的一基板。该第一凹槽具有一第一部分、一第二部分和一第三部分,且该第二部分位于该第一部分和该第三部分之间。该半导体器件包括一膜且设置在该第一凹槽的该第二部分上。该半导体器件具有与该基板相邻且相对于该膜的一第一表面。该膜被该第一表面暴露。技术研发人员:萧旭良,赖律名,黄敬涵,沈家弘受保护的技术使用者:日月光半导体制造股份有限公司技术研发日:技术公布日:2024/3/4本文地址:https://www.jishuxx.com/zhuanli/20240726/124686.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种微珠的组装方法与流程

下一篇

返回列表