一种红外探测器芯片晶圆及红外探测器的制作方法

- 国知局

- 2024-07-27 13:03:32

本申请涉及红外探测器,更具体地说,涉及一种红外探测器芯片晶圆、红外探测器。

背景技术:

1、用于探测物体红外辐射信号的电子元件被称为红外探测器。探测器的核心是探测器芯片,探测器芯片由mems传感器和cmos读出电路构成。红外探测器分为制冷红外探测器,非制冷红外探测器,非制冷光子探测器。

2、微测辐射热计是非制冷红外探测器应该最广泛的一种,微测辐射热计为mems(micro-electro-mechanical system,微机电系统)微桥结构。

3、目前,mems微测辐射热计结构的红外探测器大多采用横向互联引线键合技术实现与外部电路的连接,这种技术相对成熟,但是这种连接方式会导致互连可靠性低、信号传输存在延迟及红外探测器封装体积增加。

4、综上所述,如何增强非制冷红外探测器互连可靠性,降低信号传输延迟和封装体积,是目前本领域技术人员亟待解决的技术问题。

技术实现思路

1、有鉴于此,本申请的目的是提供一种红外探测器芯片晶圆及红外探测器,用于增强红外探测器互连可靠性,降低信号传输延迟和封装体积。

2、为了实现上述目的,本申请提供如下技术方案:

3、一种红外探测器芯片晶圆,包括衬底晶圆、设置在所述衬底晶上表面的外延层、设置在所述外延层上表面的层间介质、设置在所述层间介质中的集成电路、设置在所述层间介质的上表面且与所述集成电路相连的微测辐射热计;

4、所述集成电路处设有贯穿所述层间介质、所述外延层及所述衬底晶圆的通孔,所述通孔的侧壁设有绝缘层,且所述通孔内填充有导电材料,以使所述集成电路与所述导电材料相连;

5、所述衬底晶圆的下表面设有与所述导电材料相连的导电结构,以使所述集成电路通过所述导电结构与外部电路相连。

6、优选的,所述通孔内还设有位于所述绝缘层与所述导电材料之间的黏附阻挡层。

7、优选的,所述通孔内还设有位于所述黏附阻挡层和所述导电材料之间的种子层。

8、优选的,所述导电结构包括位于所述通孔处的第一导电结构;

9、或者,所述导电结构包括从所述通孔处延伸至所述通孔外的第二导电结构;各所述第二导电结构间并不相连。

10、优选的,所述第一导电结构包括第一金属化层、位于所述第一金属化层下表面的第一焊料。

11、优选的,所述第二导电结构包括位于所述衬底晶圆下表面除所述通孔处之外的位置处的第一pi层、从所述通孔处延伸至所述通孔外的第二金属化层、位于所述第二金属化层下表面再布线层、位于所述再布线层下表面的预设区域处的第三金属化层、位于所述第三金属化层下表面的第二焊料、位于所述第一pi层下表面未设置所述第二金属化层处及所述再布线层下表面未设置所述第二焊料处的第二pi层;

12、其中,位于所述通孔处的所述第二金属化层与所述导电材料相连,延伸至所述通孔外的所述第二金属化层位于所述第一pi层的下表面,所述预设区域为所述通孔对应区域之外的区域。

13、优选的,所述集成电路包括cmos区、多层导电电路互连区,所述cmos区中包括cmos组件,所述多层导电电路互连区包括用于将所述cmos组件与所述微测辐射热计相连的多层导电电路互连层,每层所述导电电路互连层均包括接触孔、位于所述接触孔处的导电层;

14、其中,位于底层的所述导电电路互连层中的接触孔与所述cmos组件相连,除位于底层的所述导电电路互连层外的其余所述导电电路互连层中的接触孔与下一层的所述导电电路互连层中的导电层相连,位于顶层的所述导电电路互连层中的导电层还与所述微测辐射热计相连,且位于顶层的所述导电电路互连层中还包括与所述导电材料相连的信号传输导电层。

15、一种晶圆级封装的红外探测器,包括如上述任一项所述的红外探测器芯片晶圆、键合在所述红外探测器芯片晶圆上方的窗口晶圆,所述红外探测器与所述窗口晶圆形成第一真空腔体,所述红外探测器芯片晶圆中的微测辐射热计位于所述第一真空腔体内。

16、优选的,所述窗口晶圆出射面还包括吸气剂区域。

17、一种像素级封装的红外探测器,包括如上述任一项所述的红外探测器芯片晶圆、设置在所述红外探测器芯片晶圆上表面的像素封装层;所述像素封装层与所述红外探测器芯片晶圆形成与所述红外探测器芯片晶圆中的各微测辐射热计一一对应的第二真空腔体,各所述微测辐射热计分别位于相应的所述第二真空腔体内。

18、优选的,所述像素封装层包括在与所述微测辐射热计对应区域内设置有释放孔的罩体层、位于所述罩体层上表面的密封层。

19、一种金属封装或陶瓷封装的红外探测器,包括管壳、设置在所述管壳中的如上述任一项所述的红外探测器芯片晶圆,其中,所述红外探测器芯片晶圆通过其中的导电结构与所述管壳中的电路相连。

20、本申请提供了一种红外探测器芯片晶圆及红外探测器,其中,红外探测器包括衬底晶圆、设置在衬底晶上表面的外延层、设置在外延层上表面的层间介质、设置在层间介质中的集成电路、设置在层间介质的上表面且与集成电路相连的微测辐射热计;集成电路处设有贯穿层间介质、外延层及衬底晶圆的通孔,通孔的侧壁设有绝缘层,且通孔内填充有导电材料,以使集成电路与导电材料相连;衬底晶圆的下表面设有与导电材料相连的导电结构,以使集成电路通过导电结构与外部电路相连。

21、本申请公开的上述技术方案,在集成电路处设置贯穿层间介质、外延层和衬底晶圆的通孔,并在通孔内填充导电材料,以使得红外探测器中的集成电路可通过通孔中的导电材料、衬底晶圆下表面设置的导电结构与外部电路相连,即使得集成电路可通过通孔与外部电路互连,也即使得红外探测器可通过通孔处的导电结构与外部电路互连,而不再需要通过从集成电路引出互连线来与外部电路相连,因此,可有效缩短电互联长度,提高互连可靠性,减少信号传输延迟,并可减小红外探测器封装体积,使得红外探测器可满足向着高密度互连、小型化、高性能、多功能的发展需求。其中,在通孔侧壁上设置绝缘层可阻断导电材料和衬底晶圆的电导通,以保证红外探测器的可靠性。

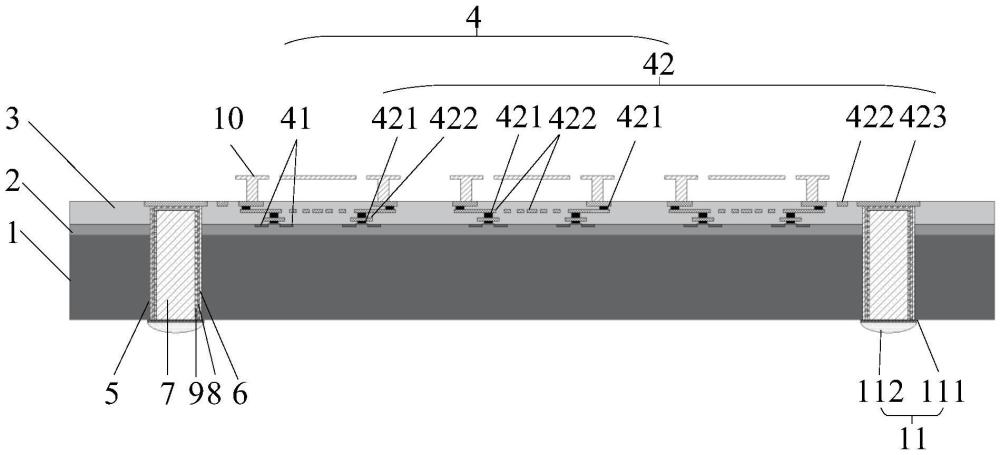

技术特征:1.一种红外探测器芯片晶圆,其特征在于,包括衬底晶圆(1)、设置在所述衬底晶圆(1)上表面的外延层(2)、设置在所述外延层(2)上表面的层间介质(3)、设置在所述层间介质(3)中的集成电路(4)、设置在所述层间介质(3)的上表面且与所述集成电路(4)相连的微测辐射热计(10);

2.根据权利要求1所述的红外探测器芯片晶圆,其特征在于,所述通孔(5)内还设有位于所述绝缘层(6)与所述导电材料(7)之间的黏附阻挡层(8)。

3.根据权利要求2所述的红外探测器芯片晶圆,其特征在于,所述通孔(5)内还设有位于所述黏附阻挡层(8)和所述导电材料(7)之间的种子层(9)。

4.根据权利要求1所述的红外探测器芯片晶圆,其特征在于,所述导电结构包括位于所述通孔(5)处的第一导电结构(11);

5.根据权利要求4所述的红外探测器芯片晶圆,其特征在于,所述第一导电结构(11)包括第一金属化层(111)、位于所述第一金属化层(111)下表面的第一焊料(112)。

6.根据权利要求4所述的红外探测器芯片晶圆,其特征在于,所述第二导电结构(12)包括位于所述衬底晶圆(1)下表面除所述通孔(5)处之外的位置处的第一pi层(121)、从所述通孔(5)处延伸至所述通孔(5)外的第二金属化层(122)、位于所述第二金属化层(122)下表面的再布线层(125)、位于所述再布线层(125)下表面的预设区域处的第三金属化层、位于所述第三金属化层下表面的第二焊料(123)、位于所述第一pi层(121)下表面未设置所述第二金属化层(122)处及所述再布线层(125)下表面未设置所述第二焊料(123)处的第二pi层(124);

7.根据权利要求1所述的红外探测器芯片晶圆,其特征在于,所述集成电路(4)包括cmos区(41)、多层导电电路互连区(42),所述cmos区(41)中包括cmos组件,所述多层导电电路互连区(42)包括用于将所述cmos组件与所述微测辐射热计(10)相连的多层导电电路互连层,每层所述导电电路互连层均包括接触孔(421)、位于所述接触孔(421)处的导电层(422);

8.一种红外探测器,其特征在于,所述红外探测器为晶圆级封装的红外探测器,包括如权利要求1至7任一项所述的红外探测器芯片晶圆、键合在所述红外探测器芯片晶圆上方的窗口晶圆(13),所述红外探测器芯片晶圆与所述窗口晶圆(13)形成第一真空腔体(14),所述红外探测器芯片晶圆中的微测辐射热计(10)位于所述第一真空腔体(14)内。

9.根据权利要求8所述的红外探测器,其特征在于,所述窗口晶圆(13)出射面还包括吸气剂区域(18)。

10.一种红外探测器,其特征在于,所述红外探测器为像素级封装的红外探测器,包括如权利要求1至7任一项所述的红外探测器芯片晶圆、设置在所述红外探测器芯片晶圆上表面的像素封装层(19);所述像素封装层(19)与所述红外探测器芯片晶圆形成与所述红外探测器芯片晶圆中的各微测辐射热计(10)一一对应的第二真空腔体(20),各所述微测辐射热计(10)分别位于相应的所述第二真空腔体(20)内。

11.根据权利要求10所述的红外探测器,其特征在于,所述像素封装层(19)包括在与所述微测辐射热计(10)对应区域内设置有释放孔(192)的罩体层(191)、位于所述罩体层(191)上表面的密封层(193)。

12.一种红外探测器,其特征在于,所述红外探测器为金属封装或陶瓷封装的红外探测器,包括管壳、设置在所述管壳中的如权利要求1至7任一项所述的红外探测器芯片晶圆,其中,所述红外探测器芯片晶圆通过其中的导电结构与所述管壳中的电路相连。

技术总结本申请公开了一种红外探测器芯片晶圆及红外探测器其封装结构,红外探测器芯片晶圆包括衬底晶圆、外延层、层间介质、集成电路、与集成电路相连的微测辐射热计;集成电路处设有贯穿层间介质、外延层及衬底晶圆的通孔,通孔的侧壁设有绝缘层,通孔内填充有导电材料,以使集成电路与导电材料相连;衬底晶圆下表面设有与导电材料相连的导电结构,以使集成电路通过导电结构与外部电路相连。本申请公开的技术方案,在集成电路处设置通孔,在通孔内填充导电材料,以使集成电路通过导电材料及导电结构与外部电路相连,而不再需要通过从集成电路引出互连线来与外部电路相连,从而缩短电互联长度,提高互连可靠性,降低信号传输延迟和封装体积。技术研发人员:刘继伟,李松华,刘向宏,胡汉林,王兴祥受保护的技术使用者:烟台睿创微纳技术股份有限公司技术研发日:20230818技术公布日:2024/3/27本文地址:https://www.jishuxx.com/zhuanli/20240726/124729.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表