一种多芯片双面腔式封装结构及封装方法与流程

- 国知局

- 2024-07-27 13:06:31

本发明属于轴角转换产品,特别是一种多芯片双面腔式封装结构及封装方法。

背景技术:

1、现代电子设备正在向小型化、轻量化、多功能、高可靠和低成本方向发展,对组装和互连技术提出了越来越高的需求,这就催生了系统级集成封装和微系统技术的研究。系统级封装技术是多种混合集成电路技术的集成,集成各种光电子器件、mems器件、模拟、数字以及无源元件,采用三维组装的制造技术实现元器件之间的结构和电气互连,构建功能单元,实现电子产品完整的系统或子系统功能。航空航天、军工等领域电子产品具有高性能、小型化、多品种和小批量等特点,系统级封装技术顺应了汽车、电子的应用需求,因此在这一技术领域具有广泛的应用市场和发展前景。

2、目前,轴角转换产品多为二维平面组装工艺,内部的元器件通过焊接、粘接等工艺方式固定在基板或壳体上,产品内部空间利用率低,芯片堆叠封装目前多用于实现存储功能,未涉及到轴角转换领域的多芯片堆叠技术。此外,超大超重规格的元器件采用粘接方式质量一致性差,不能通过产品高可靠的要求,经常出现元器件脱落问题。再有,单腔体封装无法适应如今轴角转换模块小型化的问题。

技术实现思路

1、本发明的目的在于针对上述现有技术存在的问题,提供一种多芯片双面腔式封装结构,通过设计一体化双面腔体,将多个芯片组装到一体化双面腔体中,多层芯片堆叠通过预植球低弧反向键合与板级实现电气互联,同时将无源元件一体板组装到一体化双面腔体中,并通过焊接方式实现与一体化腔体的电气互联。一体化双面结构腔体通过激光封焊、平行缝焊、高温焊接等方式实现气密封装要求,从而实现轴角转换产品的高密度封装,并提高产品的封装可靠性。

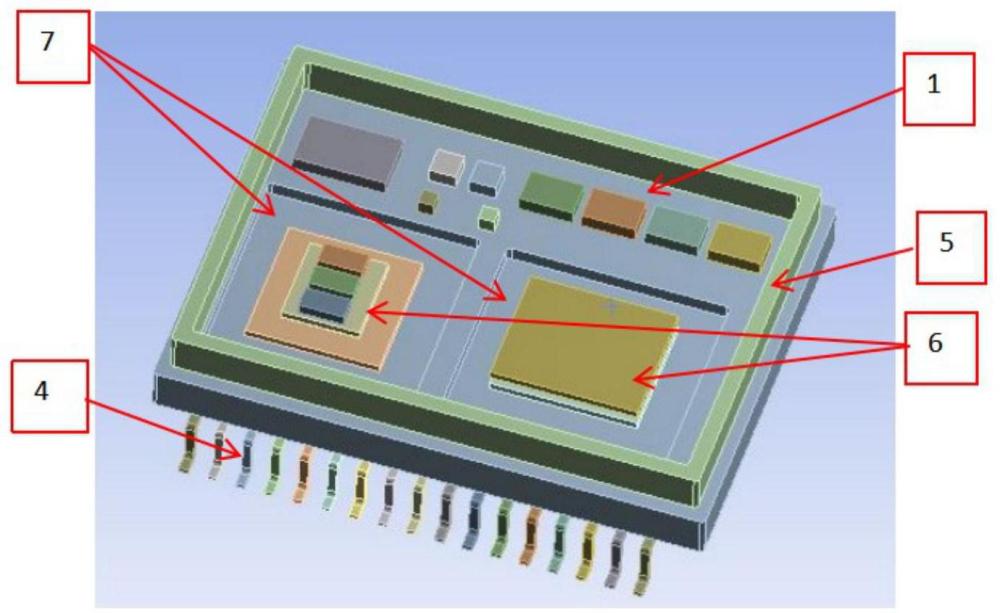

2、实现本发明目的的技术解决方案为:一方面,提供了一种多芯片双面腔式封装结构,该封装结构包括一体化双面腔体,多层芯片叠装在所述一体化双面腔体中,多层芯片堆叠通过预植球低弧反向键合与一体化双面腔体实现电气互联;同时,无源元件一体板组装在所述一体化双面腔体中,并通过焊接方式与一体化双面腔体实现电气互联;所述一体化双面腔体为密封结构,且其底部背面焊接引脚。

3、进一步地,所述一体化双面腔体包括上、下两个深腔,上深腔内设有多个嵌入式台阶腔体,作为多层芯片叠装的空间,下深腔内安装所述无源元件一体板。

4、进一步地,所述上深腔内设有多层台阶键合区域,用于降低键合点之间的高度差以实现多层芯片的空间键合走线,进而实现产品的电气连接。

5、进一步地,所述一体化双面腔体还包括分别装配在上下两个深腔上的上盖板和下盖板,以形成密封腔体结构;所述上盖板、下盖板与上下两个深腔之间为独立结构或一体化结构。

6、进一步地,所述上盖板和下盖板上镀镍,所述下盖板单面镀金,该单面与引脚焊接面共面。

7、进一步地,所述上深腔、下深腔的开口边缘处设有焊接环,通过高温钎焊的方式与一体化双面腔体焊接。

8、进一步地,所述上深腔和下深腔内的粘接区域和焊接区域采用镍金镍金交替镀覆。

9、进一步地,所述多层芯片堆叠的方式为:底层芯片上叠装基板材料,所述基板材料上布线实现电气的重新互联,通过键合方式实现顶层芯片与底层芯片、顶层芯片和上深腔的电气互联。

10、进一步地,所述多层芯片堆叠中,若相邻芯片为同规格同尺寸,两芯片之间通过硅中间层抬高。

11、另一方面,提供了一种多芯片双面腔式封装结构的封装实现方法,所述方法包括:

12、(1)完成无源元件一体板浆料印刷、烧结、阻容元件制备;

13、(2)在上深腔中完成若干元器件的焊接;

14、(3)无源元件一体板与一体化双面腔体通过焊接方式实现电气互联;

15、(4)在一体化双面腔体中根据不同的功能单元设计多层芯片叠装,并先完成底层芯片的粘接;

16、(5)在上深腔内的嵌入式台阶腔体内部粘接底层芯片,底层芯片四周设有多个pad,采用预植球工艺先在底层芯片pad上通过自动键合设备完成预植球,再完成低弧反向键和;

17、(6)在底层芯片上粘接中间层材料;

18、(7)在中间层材料上点涂胶水,再将第二层芯片粘接到中间层材料上;

19、(8)完成预植球,再采用低弧反向键合方式完成第二层芯片的粘接和电气互联,以此类推实现多层芯片堆叠;

20、(9)将上盖板和下盖板通过焊接或激光焊接或平行缝焊工艺实现与一体化双面腔体的气密封装;

21、(10)通过设计成形工装完成引脚成形,使其焊接面与下盖板上的焊接面共面。

22、本发明与现有技术相比,其显著优点为:

23、(1)设计了一体化双面腔体,包括上下两个深腔,上面深腔内部设计多个嵌入式台阶腔体,给多层芯片留有叠装的空间,并设计多层台阶键合区域,便于多层芯片的空间键合走线实现产品的电气连接。芯片堆叠的数量和嵌入式台阶腔体数量可灵活调节,适应性广。

24、(2)多层芯片叠装实现同规格同尺寸芯片的叠装,芯片之间通过硅中间层抬高,给底层芯片留有空间键合空间。

25、(3)多层芯片叠装,采用低应力粘接胶能降低温度循环过程对芯片造成的应力作用。

26、(4)无源元件一体板采用厚膜制成工艺,基板上设计电路和阻容元件,与一体化双面腔通过焊接方式实现电气互联,提高了元器件的可靠性。

27、(5)一体化双面结构腔体通过激光封焊、平行缝焊、高温焊接等方式实现气密封装要求,使得在同样面积大小的封装集成芯片数量成倍增加,缩小了产品封装的尺寸,从而实现轴角转换产品的高密度封装,并提高产品的封装可靠性。

28、(6)模块化设计可以灵活用于产品的扩容,提高产品的集成度。不同模块封装更有利于产品实现多功能化。

29、下面结合附图对本发明作进一步详细描述。

技术特征:1.一种多芯片双面腔式封装结构,其特征在于,该封装结构包括一体化双面腔体,多层芯片叠装在所述一体化双面腔体中,多层芯片堆叠通过预植球低弧反向键合与一体化双面腔体实现电气互联;同时,无源元件一体板组装在所述一体化双面腔体中,并通过焊接方式与一体化双面腔体实现电气互联;所述一体化双面腔体为密封结构,且其底部背面焊接引脚。

2.根据权利要求1所述的多芯片双面腔式封装结构,其特征在于,所述一体化双面腔体包括上、下两个深腔,上深腔内设有多个嵌入式台阶腔体,作为多层芯片叠装的空间,下深腔内安装所述无源元件一体板。

3.根据权利要求2所述的多芯片双面腔式封装结构,其特征在于,所述上深腔内设有多层台阶键合区域,用于降低键合点之间的高度差以实现多层芯片的空间键合走线,进而实现产品的电气连接。

4.根据权利要求2所述的多芯片双面腔式封装结构,其特征在于,所述一体化双面腔体还包括分别装配在上下两个深腔上的上盖板和下盖板,以形成密封腔体结构;所述上盖板、下盖板与上下两个深腔之间为独立结构或一体化结构。

5.根据权利要求4所述的多芯片双面腔式封装结构,其特征在于,所述上盖板和下盖板上镀镍,所述下盖板单面镀金,该单面与引脚焊接面共面。

6.根据权利要求2所述的多芯片双面腔式封装结构,其特征在于,所述上深腔、下深腔的开口边缘处设有焊接环,通过高温钎焊的方式与一体化双面腔体焊接。

7.根据权利要求2所述的多芯片双面腔式封装结构,其特征在于,所述上深腔和下深腔内的粘接区域和焊接区域采用镍金镍金交替镀覆。

8.根据权利要求1所述的多芯片双面腔式封装结构,其特征在于,所述多层芯片堆叠的方式为:底层芯片上叠装基板材料,所述基板材料上布线实现电气的重新互联,通过键合方式实现顶层芯片与底层芯片、顶层芯片和上深腔的电气互联。

9.根据权利要求7所述的多芯片双面腔式封装结构,其特征在于,所述多层芯片堆叠中,若相邻芯片为同规格同尺寸,两芯片之间通过硅中间层抬高。

10.基于权利要求1至9任意一项所述多芯片双面腔式封装结构的封装实现方法,其特征在于,所述方法包括:

技术总结本发明提供了一种多芯片双面腔式封装结构及封装方法。通过设计一体化双面腔体,将多个芯片组装到一体化双面腔体中,多层芯片堆叠通过预植球低弧反向键合与板级实现电气互联,同时将无源元件一体板组装到一体化双面腔体中,并通过焊接方式实现与一体化腔体的电气互联。一体化双面结构腔体通过激光封焊、平行缝焊、高温焊接等方式实现气密封装要求,使得在同样面积大小的封装集成芯片数量成倍增加,缩小了产品封装的尺寸,从而实现轴角转换产品的高密度封装,并提高产品的封装可靠性。且芯片堆叠的数量和一体化腔体数量可灵活调节,适应性广。技术研发人员:臧艳丽,高虎,丁成洋,王洋,刘盖特,徐绕琪,张甜,张永浩,姚海涛,武林,王建成受保护的技术使用者:连云港杰瑞电子有限公司技术研发日:技术公布日:2024/7/4本文地址:https://www.jishuxx.com/zhuanli/20240726/124958.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。