具有基极电流再分布电路的带隙电路的制作方法

- 国知局

- 2024-08-01 00:16:01

本公开涉及曲率补偿电路和带隙参考电压生成电路。

背景技术:

1、如下的带隙参考电压生成集成电路是期望的,该电路具有比简单带隙电路的典型温度系数(tc)低得多的tc,并且以这样的方式来实现这一点,即,tc可以在集成电路生产中使用传统的“魔术电压”型修调、在单一温度下进行单次测量来被修调。

技术实现思路

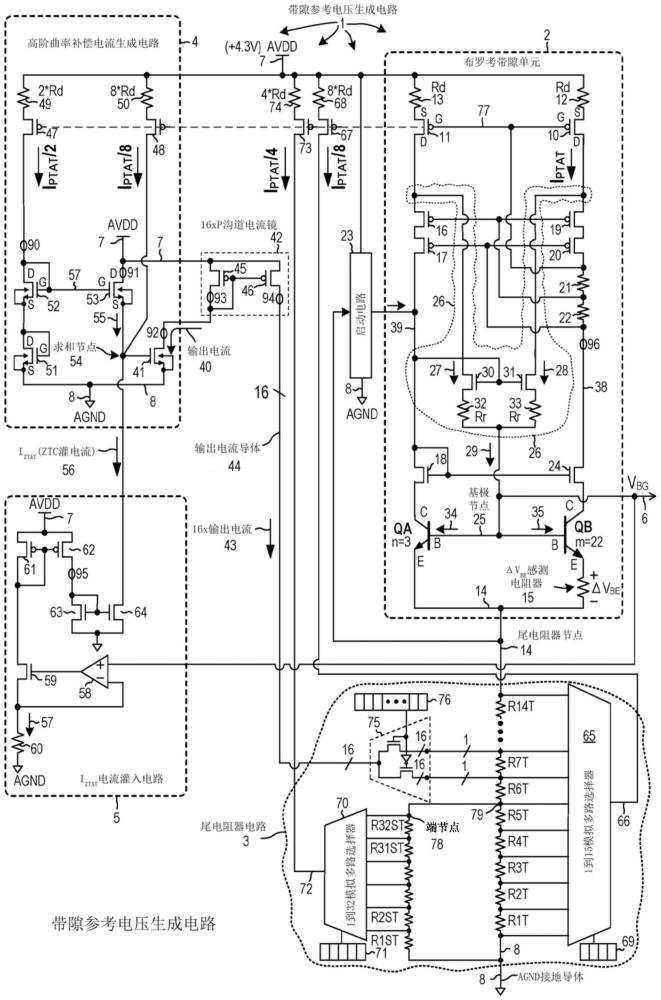

1、一种带隙参考电压生成电路包括布罗考(brokaw)带隙单元电路、尾电阻器电路、高阶曲率补偿电流生成电路和iztat电流灌入电路(current sink circuit)。带隙参考电压生成电路生成被供应到vbg带隙输出端子和导体上的带隙参考电压vbg。在一个实例中,vbg带隙输出电压在pvt上(在工艺变化上,在从5.7伏下至4.3伏的供电电压范围上,以及在从-40℃到+125℃的温度范围上)具有温度系数±3ppm/c。

2、布罗考带隙单元电路包含电流镜,电流镜包含第一p沟道晶体管和第二p沟道晶体管、第一双极npn晶体管qa、第二双极npn晶体管qb和δvbe感测电阻器。第一电流支路从电流镜的第一p沟道晶体管的漏极延伸到第一双极晶体管qa的集电极。第二电流支路从电流镜的第二p沟道晶体管的漏极延伸到第二双极晶体管qb的集电极。双极晶体管qa和qb的基极电极在基极节点处被耦合在一起。vbg带隙输出端子被连接到该基极节点,并且是该基极节点的一部分。δvbe感测电阻器被耦合在第一双极晶体管qa的发射极和第二双极晶体管qb的发射极之间。可修调的尾电阻器电路被耦合在第一双极晶体管qa的发射极和接地导体之间。

3、在第一新颖的方面,布罗考带隙单元电路进一步包含基极电流再分布电路。基极电流再分布电路被耦合来传导来自第一电流支路上的节点的第一基极再供电电流并且将该电流供应到基极节点上,并且还被耦合来传导来自第二电流支路上的节点的第二基极再供电电流并且将该电流供应到基极节点上。从第一电流支路和第二电流支路引入的基极再供电电流的总和提供流到第一双极晶体管qa和第二双极晶体管qb的基极中的基极电流。在一个实施方案中,基极电流再分布电路包含第一n沟道晶体管、第一电阻器、第二n沟道晶体管和第二电阻器。第一晶体管的漏极被耦合到第一电流支路以使得其可以从第一电流支路引入第一基极再供电电流。第一电阻器被耦合在第一晶体管的源极和基极节点之间。第二晶体管的漏极被耦合到第二电流支路以其可以从第二电流支路引入第二基极再供电电流。第二电阻器被耦合在第二晶体管的源极和基极节点之间。基极电流再分布电路的第一晶体管和第二晶体管的栅极被耦合在一起。在一个实例中,用于基极电流再分布电路的第一晶体管和第二晶体管的栅极电压是从第一电流支路上的节点获取的。

4、在第二新颖的方面,高阶曲率补偿电流生成电路包含p沟道电流镜和四个n沟道晶体管。p沟道电流镜具有第一电流支路、第二电流支路和第三电流支路。第二电流支路输出的第二镜像电流的幅值是第三电流支路输出的第三镜像输出电流的幅值的一部分。第一n沟道晶体管具有源极、漏极和栅极。栅极被耦合到漏极和接地导体。第二n沟道晶体管具有源极、漏极和栅极。源极被耦合到第一n沟道晶体管的漏极。第二n沟道晶体管的栅极和漏极被耦合在一起,并且被耦合来接收来自电流镜的第三支路的第三镜像输出电流。第三n沟道晶体管具有源极、漏极和栅极。第三n沟道晶体管的栅极被耦合到第二n沟道晶体管的栅极。第三n沟道晶体管的源极在求和节点处被耦合到第四n沟道晶体管的栅极。灌电流电路被耦合来灌入来自求和节点的灌电流。另外,电流镜的第二电流支路被耦合来将第二镜像输出电流供应到求和节点上。第四n沟道晶体管的源极在接地导体处被耦合到第一n沟道晶体管的源极。高阶曲率补偿电流生成电路的输出电流是流到第四n沟道晶体管中的漏极电流。第四n沟道晶体管在近阈值操作区域中操作。在一个实例中,从第一电流支路供应的第一镜像输出电流是iptat电流,第二镜像输出电流是iptat/8电流,第三镜像输出电流是iptat/2电流,并且灌电流是iztat恒定的固定电流,iztat恒定的固定电流具有电路的温度操作范围的基本上为零的温度系数。在整个带隙参考电压生成电路的一个实施方案中,来自高阶曲率补偿电流生成电路的输出电流被镜像以便生成多个相同的输出电流。这些输出电流中的每个都被供应到尾电阻器电路的电阻器串上的多个抽头节点中的选择的一个抽头节点上。

5、进一步的细节及实施方案和方法及技术在下面的详细描述中被描述。本概述内容无意限定本发明。本发明由权利要求限定。

技术特征:1.一种电压参考电路,所述电压参考电路包括:

2.根据权利要求1所述的电压参考电路,其中所述第一基极再供电电流和所述第二基极再供电电流是相同的电流。

3.根据权利要求1所述的电压参考电路,其中所述第一基极再供电电流与所述第二基极再供电电流成正比。

4.根据权利要求1所述的电压参考电路,其中所述电流再分布电路包括:

5.根据权利要求4所述的电压参考电路,其中所述第三晶体管的所述漏极被耦合到所述第一p沟道晶体管的所述漏极,并且其中所述第四晶体管的所述漏极被耦合到所述第二p沟道晶体管的所述漏极。

6.根据权利要求5所述的电压参考电路,其中所述电流再分布电路的所述第三晶体管和所述第四晶体管的所述栅极被耦合到所述第一电流支路上的节点。

7.根据权利要求4所述的电压参考电路,其中所述电流再分布电路的所述第三晶体管和所述第四晶体管是叉指型的。

8.根据权利要求1所述的电压参考电路,其中所述第一电流支路包括第一p沟道共源共栅晶体管,其中所述第二电流支路包括第二p沟道共源共栅晶体管,并且其中所述第一p沟道共源共栅晶体管的栅极被耦合到所述第二p沟道共源共栅晶体管的栅极。

9.根据权利要求1所述的电压参考电路,其中所述第一电流支路包括第一n沟道共源共栅晶体管,其中所述第二电流支路包括第二n沟道共源共栅晶体管,并且其中所述第一n沟道共源共栅晶体管的栅极被耦合到所述第二n沟道共源共栅晶体管的栅极。

10.根据权利要求1所述的电压参考电路,其中所述rtail电阻器电路包括:

11.根据权利要求1所述的电压参考电路,其中所述rtail电阻器电路包括:

12.一种方法,所述方法包括以下步骤:

13.根据权利要求12所述的方法,其中所述第一基极再供电电流和所述第二基极再供电电流彼此相同。

14.根据权利要求12所述的方法,其中在(d)中,所述第一基极再供电电流在所述第一p沟道晶体管的漏极处从所述第一电流支路被引入,并且其中在(e)中,所述第二基极再供电电流在所述第二p沟道晶体管的漏极处从所述第二电流支路被引入。

15.根据权利要求12所述的方法,其中在(d)中,所述第一基极再供电电流在所述第一p沟道晶体管的所述漏极处从所述第一电流支路被引入,并且在其到所述第一双极晶体管的所述集电极的途中流过第一共源共栅晶体管,并且其中在(e)中,所述第二基极再供电电流在所述第二p沟道晶体管的所述漏极处从所述第二电流支路被引入,并且在其到所述第二双极晶体管的所述集电极的途中流过第二共源共栅晶体管。

16.一种参考电压电路,所述参考电压电路包括:

17.根据权利要求16所述的参考电压电路,其中所述电流镜的所述第一电流镜支路包括第一电流支路晶体管,其中所述第一电流支路晶体管具有漏极,其中所述第四节点和所述第一电流支路晶体管的所述漏极是同一节点;其中所述电流镜的所述第二电流镜支路包括第二电流支路晶体管,其中所述第二电流支路晶体管具有漏极,并且其中所述第五节点和所述第二电流支路晶体管的所述漏极是同一节点。

18.根据权利要求16所述的参考电压电路,其中所述电流镜的所述第一电流镜支路包括第一电流支路晶体管,其中所述第一电流支路晶体管具有漏极,其中所述第四节点和所述第一电流支路晶体管的所述漏极不是同一节点;其中所述电流镜的所述第二电流镜支路包括第二电流支路晶体管,其中所述第二电流支路晶体管具有漏极,并且其中所述第五节点和所述第二电流支路晶体管的所述漏极不是同一节点。

19.根据权利要求16所述的参考电压电路,其中所述电流再分布电路包括:

20.根据权利要求16所述的参考电压电路,其中所述电流再分布电路将电流传导到所述第三节点或者传导来自所述第三节点的电流,并且其中所述电流再分布电路传导到所述第三节点或者所述电流再分布电路从所述第三节点传导的电流是所述第一基极再供电电流和所述第二基极再供电电流的总和。

技术总结一种带隙参考电压生成电路包含带隙单元、尾电阻器电路、高阶曲率补偿电流生成电路、I<subgt;ZTAT</subgt;电流灌入电路和启动电路。带隙单元具有基极电流再分布电路,基极电流再分布电路使用从单元的第一电流支路获取的第一基极再供电电流来驱动双极晶体管的基极,并且使用从单元的第二电流支路获取的匹配的第二基极再供电电流。由于双极电流增益变化而导致的V<subgt;BG</subgt;误差减小。曲率补偿电流生成电路的N沟道晶体管在近阈值区域中操作。补偿电路的输出电流按照输入电流的大约2.1的幂变化。尾电阻器电路可以以各种方式编程以使得曲率校正的量可以被定制和修调。技术研发人员:马克·平奇巴克受保护的技术使用者:湍泰半导体香港有限公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240730/200335.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表