一种嵌入式异质结二极管SiCMOSFET器件的制作方法

- 国知局

- 2024-07-31 18:25:01

本发明涉及一种嵌入式异质结二极管sic mosfet器件,属于半导体器件制造。

背景技术:

1、mosfet(金属氧化物半导体场效应晶体管)是一种广泛使用的半导体器件,其工作原理即基于源极(source)、漏极(drain)和栅极(gate)三个区域之间的电场来控制电流的流动,比如,在正常工作状态下,通过在栅极和源极之间施加电压(称为栅极电压),当栅极电压超过一定值(通常该值称为阈值电压)时,可以在栅极下方的半导体表面形成一个导电通道。这个通道允许电流从源极流向漏极,从而控制mosfet的导通和关闭状态。栅极电压的大小和极性决定了通道的导电性,从而控制流过通道的电流大小。

2、目前,大多数电力电子系统中使用的mosfet都是以硅为材料的硅基功率mosfet。然而,在制造高耐压的mosfet器件时,由于硅材料本身的限制,会导致巨大的导通电阻,这通常会增加电力电子系统中不必要的能量消耗。sic材料作为第三代半导体材料的杰出代表,具有多项优秀性能。它拥有宽禁带宽度、高热导率、大临界电场和高饱和电子漂移速度等优点,因此能够进一步满足电力电子系统对更大功率、更小损耗、更小体积、更轻重量以及在恶劣环境条件下使用的需求,被视为新一代功率mosfet器件的优选材料。相比于以硅为材料制造的mosfet器件,使用sic材料制造的mosfet器件具有更低的导通电阻和更高的击穿电压。此外,它还具有更快的开关速度和更低的开关损耗。sic mosfet还可以在simosfet难以达到的频率下工作,因此sic mosfet是电力电子器件中的重要研究方向。

3、然而,sic mosfet的寄生体二极管(pin二极管)由于其较高的导通电压,在功率模块中用作续流二极管时,会导致高开关能量损失,而使用体二极管会导致双极退化的问题。因此,通常采用反并联外部肖特基势垒二极管(sbd)来抑制本体二极管的激活。因此,嵌入式sbd的sic mosfet已被广泛研究,因为外部sbd会产生寄生电感,并且需要额外的芯片面积。为了解决这一问题,又出现了结合多晶硅和sic的嵌入式异质结二极管(heterojunction diode,hjd)的sic mosfet,但是在这些结构中,异质结的形成在沟道中引入了势垒。当施加漏极-源极电压时,这个势垒会被电场影响而发生调制。如果异质结的电场调制较强,那么沟道区域的势垒就会降低,从而影响了沟道的导电性能。可能会造成器件的漏极电流不饱和,并随着漏极偏置电压的增加而增加,具有很强的漏极诱导势垒降低(drain-induced barrier lowering,dibl)效应。在异质结区域,电场通常会比较集中,这是由于材料性质和结构的不同所造成的。当电场较强时,会加速势垒的降低过程,使得dibl效应更为显著。dibl效应导致mosfet的阈值电压降低,进而影响到器件的性能,比如可能阈值电压降低会导致晶体管在未完全开启的情况下产生较大的漏电流,这会增加功耗,在数字电路中还可能导致逻辑判断错误;且使器件的开关速度下降,原因是漏极电流增加,响应时间变长。漏极电流大意味着器件在导通状态下消耗的功率高,且会造成器件发热增加。高温会影响器件的稳定性和可靠性,甚至可能导致器件损坏。

技术实现思路

1、为了解决现有sic mosfet器件存在的饱和电流大,能耗大的问题,本发明提供了一种新型结构的嵌入式异质结二极管sic mosfet器件,包含嵌入式hjd和电场保护(efp)区域,即hjd-mosfet。该结构中,异质结二极管hjd设置在jfet区域中间的沟槽侧壁处。通过对mosfet的jfet区域进行沟槽来集成hjd,因此hjd-mosfet不需要额外的大单元面积来集成单极二极管。

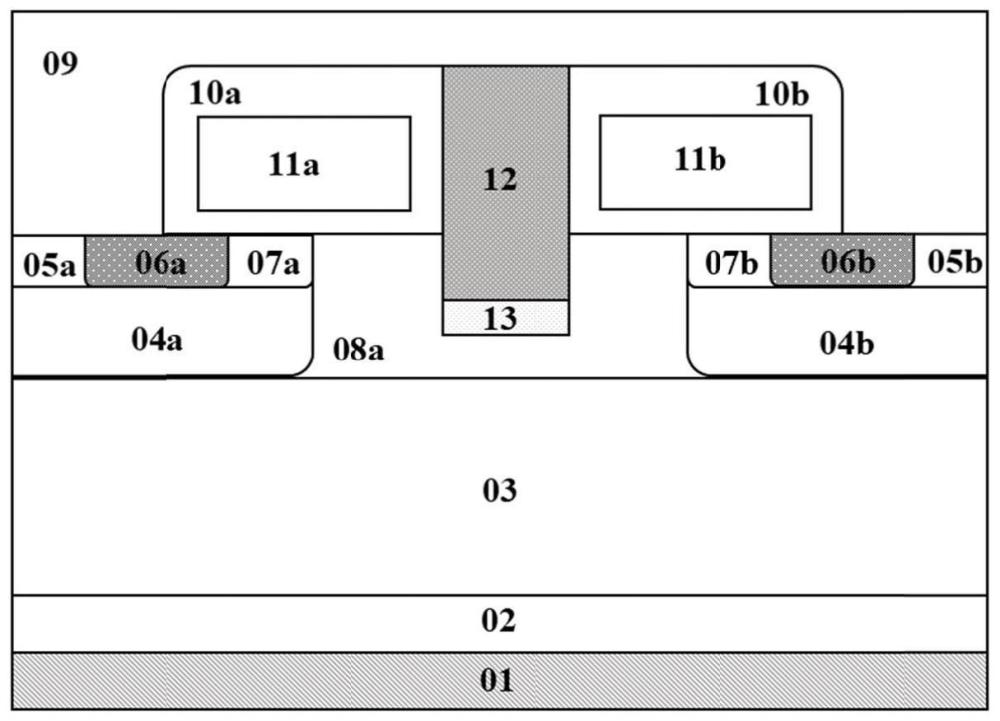

2、本发明的第一个目的在于提供一种嵌入式异质结二极管sic mosfet器件,所述sic mosfet从下而上依次包括:漏极金属区01、n型衬底区02、n型漂移区03、第一p+屏蔽区04a、第二p+屏蔽区04b、第一p型掺杂区05a、第二p型掺杂区05b、第一n型掺杂区06a、第二n型掺杂区06b、第一p型通道区07a、第二p型通道区07b、jfet中的电流扩展层csl区08a、源极金属区09、第一氧化物区10a、第二氧化物区10b、第一n型多晶硅栅极区11a、第二n型多晶硅栅极区11b、p型多晶硅区12、p型电场保护efp区13;其中,所述p型多晶硅区12处于第一氧化物区10a和第二氧化物区10b之间,且延伸至jfet中的电流扩展层csl区08a,将整块栅极改为分栅极结构;所述p型电场保护efp区13设置于所述p型多晶硅区12下方。

3、可选的,第一p+屏蔽区04a、jfet中的电流扩展层csl区08a和第二p+屏蔽区04b依次排布于n型漂移区03上方;第一p型掺杂区05a、第一n型掺杂区06a和第一p型通道区07a位于第一p+屏蔽区04a上方;第二p型掺杂区05b、第二n型掺杂区06b和第二p型通道区07b位于第二p+屏蔽区04b上方;jfet中的电流扩展层csl区08a位于p型多晶硅区12下方;第一n型多晶硅栅极区11a被第一氧化物区10a所包围;第二n型多晶硅栅极区11b被第二氧化物区10b所包围。

4、可选的,所述jfet中的电流扩展层csl区08a的掺杂浓度为9×1016cm-3,长度为2μm。

5、可选的,所述n型衬底区02材料为碳化硅,其掺杂浓度为1×1019cm-3,厚度为2~5μm,长度为6μm。

6、可选的,所述n型漂移区03材料为碳化硅,其掺杂浓度为8×1015~9×1015cm-3,厚度为8~12μm,长度为6μm。

7、可选的,所述第一p+屏蔽区04a、第二p+屏蔽区04b的掺杂浓度为4×1018~6×1018cm-3,长度为2μm。

8、可选的,所述第一p型掺杂区05a、第二p型掺杂区05b的掺杂浓度为1×1019cm-3,长度为0.5μm。

9、可选的,所述第一n型掺杂区06a、第二n型掺杂区06b的掺杂浓度为1×1019cm-3,长度为1μm。

10、可选的,所述第一p型通道区07a、第二p型通道区07b的掺杂浓度为1×1017~2×1017cm-3,长度为0.5μm。

11、可选的,所述第一氧化物区10a、第二氧化物区10b材料为二氧化硅。

12、本发明的第二个目的在于提供一种集成芯片,所述芯片采用上述嵌入式异质结二极管sic mosfet器件。

13、本发明有益效果是:

14、本发明的嵌入式异质结二极管sic mosfet采用屏蔽平面拓扑,在沟道区域下方放置p+屏蔽区域,以帮助保护沟道和栅氧化物免受高电场的影响。p+多晶硅下的高掺杂p型电场保护efp区和jfet中的电流扩展层(csl)使得mosfet表现出优异的静态性能,并且由于efp区和p+多晶硅的耗尽区造成电流路径有限,器件的饱和电流水平显著降低,从而降低了器件的功率损耗。其中,efp区域的存在可以有效保护器件免受过高电场的损害,例如电场过大导致击穿、漏电流增大的问题,调节电场分布和减小电场梯度,降低了器件的击穿风险,提高了器件在各种工作条件下的稳定性和可靠性。本技术提供的结构中,hjd设置在jfet区域中间的沟槽内壁处,因此不需要额外的大单元面积来集成单极二极管,mosfet和hjd不仅共享正向导电层,还共享边缘终端区域,从而可以减少sic晶圆面积。该结构可以减少总芯片的面积和提高功率密度,降低器件体积和成本,而且具有小单元间距可以降低器件在低电压下的导通电阻。异质结二极管的嵌入可以减小漏电流,提高器件的性能和稳定性。由于将整块栅极改成分栅极结构,减少了有效栅极面积,以及p+多晶硅区和efp区域的栅漏电容耦合的屏蔽效应,逆导电容(crss=cgd)得到降低,可以改善mosfet的开关速度,改善mosfet在高频下的性能,且有助于降低mosfet的功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240731/179074.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表