一种π型沟槽栅碳化硅MOSFET器件的制作方法

- 国知局

- 2024-07-31 18:43:43

本技术涉及功率半导体器件,特别是沟槽栅碳化硅 mosfet(金属氧化物半导体场效应晶体管)器件。

背景技术:

1、碳化硅是第三代功率半导体材料,相对于传统的硅材料,具有临界电场高,载流子饱和速度快,散热能力强等优势,更适合于高性能功率mosfet器件的制造。碳化硅mosfet的损耗包括导通损耗和开关损耗,其中导通损耗主要包括由沟道电阻,外延层电阻,衬底电阻以及金属接触电阻引起的损耗。对于碳化硅mosfet,由于栅介质层中存在大量的界面态,载流子迁移率会被界面态带来的库伦散射严重降低,这导致mosfet(bv≤1700v)的沟道电阻在总电阻中所占比例高。降低沟道电阻的一种思路是提高沟道密度,沟槽栅碳化硅mosfet可以消除平面栅结构中存在的jfet效应,实现更高的沟道密度,沟道密度的增加相当于并联了更多的沟道电阻,因此减小了总的沟道电阻。从而在相同芯片面积下,具有更高的过电流能力。

2、但是沟槽栅碳化硅mosfet在反向耐压过程中,因为曲率效应,在沟槽的底角位置电场强度高(>4mv/cm),可导致芯片击穿电压低和带来可靠性问题。因此,降低沟槽栅底角处的电场,提高击穿电压,同时保护栅介质层在高电场作用下不发生性能退化,对沟槽栅碳化硅mosfet非常重要。

3、现有技术的一种降低沟槽栅底部电场的方案为在沟槽栅底部引入p+埋层107,如图1。要实现对沟槽栅底部栅氧化层有效的保护,需要p+埋层107接到地电位。一种接地的方案为采用方形元胞设计,间隔几个元胞设计一个伪元胞沟槽,如图2,此伪元胞不导通电流,通过将源极接触孔刻蚀到伪元胞沟槽栅底部的p+埋层113,源极金属112与伪元胞p+埋层113形成欧姆接触,从而将伪元胞p+埋层113接到源极电位,在器件耐压过程中,源极电极接地,因而伪元胞p+埋层113的电位为零。而伪元胞p+埋层113与其它元胞沟槽栅底部的p+埋层107在碳化硅内部相交以实现电学连接。由于伪元胞不导通电流,因此伪元胞的数量越多,牺牲的导电沟道数量也越多,碳化硅mosfet的比导通电阻就越大。因此,伪元胞通常会间隔几个到10个元胞排列。这种情况下,距离伪元胞最远的元胞,其沟槽栅底部的p+埋层107需要通过一段很长距离的p+连接到伪元胞p+埋层113,考虑到碳化硅p型半导体电学激活率低,电阻率高,即等效为元胞沟槽底部的p+埋层107通过与一个电阻串联后连接到伪元胞p+埋层113。在碳化硅mosfet关断过程中,沟槽底部的p+埋层107中会有位移电流流过,沿着内部连通的p+埋层流动,从伪元胞接触孔流出到源极,因此元胞沟槽栅底部的p+埋层107电位不为零,这会导致对应位置的栅氧化层中的电场高,器件的可靠性降低。元胞沟槽栅底部的p+埋层107在开关过程中电位不为零,还会导致dv/dt变小,开关损耗增加。

4、现有技术的另一种实现p+埋层接地的方案是通过增加沟槽栅一侧的倾斜离子注入208,实现p+埋层207与p阱210的电学连接,如图3所示。但是这种方案不仅需要增加一次离子注入,还会牺牲一半的导电沟道,导致沟道电阻增大一倍。

技术实现思路

1、针对上文中所提到的现有技术沟槽栅碳化硅mosfet器件中存在的问题,需要一种新型沟槽栅碳化硅mosfet的器件结构及其制造方法,以在不增加器件的沟道电阻和工艺复杂度的条件下实现对沟槽栅氧化层的保护,降低电场强度,提高器件的可靠性,同时减小弥勒电容,增加dv/dt,降低开关损耗。

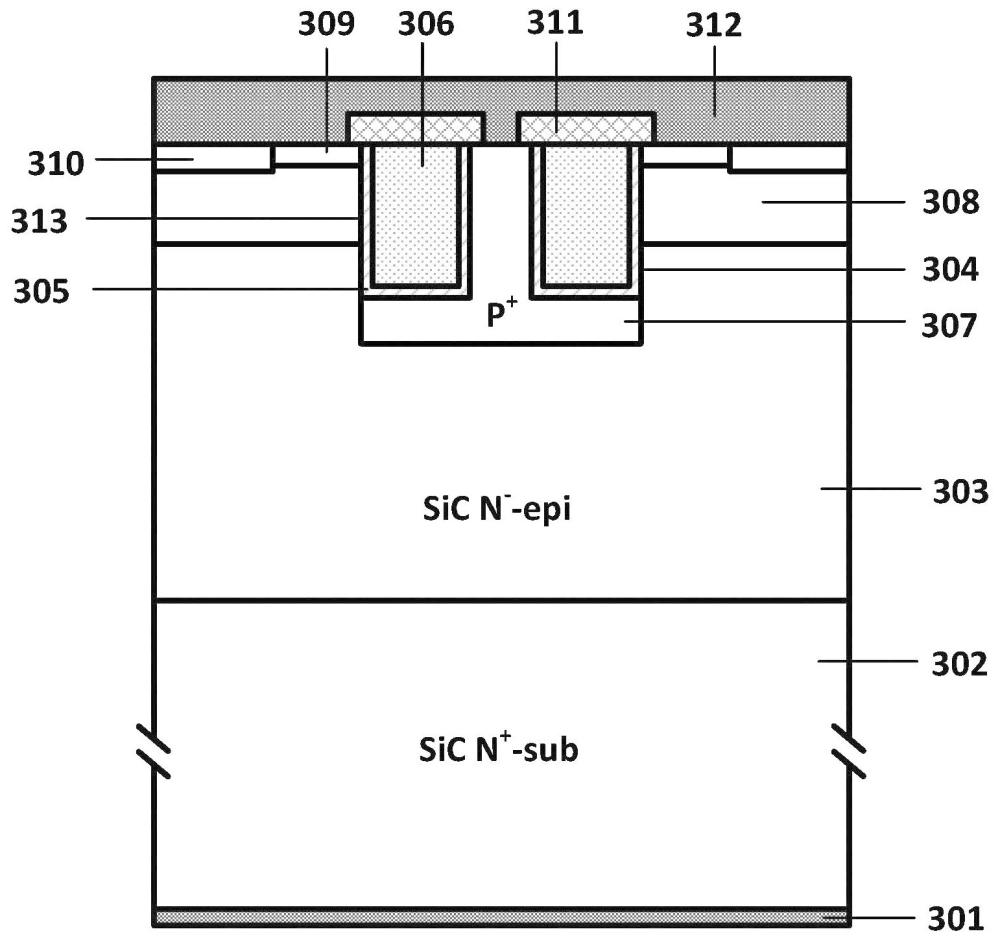

2、为实现以上所述目标,本实用新型提供一种π型沟槽栅碳化硅mosfet器件,所述的mosfet器件包括有位于底部的漏极电极和位于顶部的源极电极,所述的漏极电极上设有第一导电型重掺杂碳化硅衬底,所述的第一导电型重掺杂碳化硅衬底上设有第一导电型轻掺杂外延层,所述的第一导电型轻掺杂外延层上表面设有一个以上的周期性排列的并和所述的源极电极相连的第二导电型重掺杂深阱区、位于第二导电型重掺杂深阱区之间的第二导电型阱区、位于第二导电型阱区上方的第一导电型重掺杂源极区和第二导电型重掺杂接触区,其特征在于,所述的第二导电型重掺杂深阱区靠近左右侧壁分别设有深度浅于所述的第二导电型重掺杂深阱区的第一沟槽栅和第二沟槽栅,所述的第一沟槽栅和第二沟槽栅顶部分别设有层间介质层,所述的层间介质层分别向外侧延伸覆盖部分第一导电型重掺杂源极区,所述的第一沟槽栅和第二沟槽栅包括栅介质层和填充在栅介质层内的导电介质层。由于第一沟槽栅和第二沟槽栅分别设置在第二导电型重掺杂深阱区左右侧壁,使得第一沟槽栅和第二沟槽栅的外侧侧壁没有在第二导电型重掺杂深阱区内,而是从上到下依此与第一导电型重掺杂源极区,第二导电型阱区和第一导电型轻掺杂外延层相接触。

3、进一步的,所述的第二导电型阱区下方设有第一导电型电流扩展层,所述的第一导电型电流扩展层的掺杂浓度高于第一导电型轻掺杂外延层且低于第二导电型重掺杂深阱区。

4、进一步的,所述的源极电极与位于第一沟槽栅和第二沟槽栅之间部分的第二导电型重掺杂深阱区相连通。

5、进一步的,第一沟槽栅和第二沟槽栅的下方和中间均设有第二导电型重掺杂深阱区。

6、本实用新型工作原理解释如下:

7、本实用新型通过高能离子注入制造第二导电型重掺杂深阱区(p+深阱),该第二导电型重掺杂深阱区(p+深阱)的深度大于沟槽栅的深度,沟槽栅位于第二导电型重掺杂深阱区(p+深阱)内部,且第一沟槽左侧侧壁和第二沟槽右侧侧壁与第二导电型重掺杂深阱区(p+深阱)的侧边界重合,第一沟槽栅和第二沟槽栅之间的间距可以根据工艺能力调整,以确保能开出接触孔和正常填充金属,填充源极金属后可保持第二导电型重掺杂深阱区(p+深阱)的电位和源极电极相同,由于第二导电型重掺杂深阱区(p+深阱)直接和源极电极连接,不同于图1所示的现有技术方案中p+埋层需要通过一段很长距离的p+连接到源极,在mosfet反向耐压时,第二导电型重掺杂深阱区(p+深阱)的电位保持在地电位,可起到有效的屏蔽作用,降低沟槽栅底部栅氧化层中的电场,增强器件的可靠性。在器件开关过程中,由于第二导电型重掺杂深阱区(p+深阱)的电位保持和源极相同,因此第二导电型重掺杂深阱区(p+深阱)不会增加mosfet的弥勒电容, dv/dt高可以降低开关损耗。

8、相比于图3所示的现有技术方案,本实用新型可以通过控制第一沟槽栅和第二沟槽栅之间的间距减小元胞等效的周期长度,从而提高沟道密度,降低沟道电阻,同时,省去图3所示的现有技术方案中所需的倾斜离子注入,降低工艺复杂性。

技术特征:1.一种π型沟槽栅碳化硅mosfet器件,所述的mosfet器件包括有位于底部的漏极电极和位于顶部的源极电极,所述的漏极电极上设有第一导电型重掺杂碳化硅衬底,所述的第一导电型重掺杂碳化硅衬底上设有第一导电型轻掺杂外延层,所述的第一导电型轻掺杂外延层上表面设有一个以上的周期性排列的并和所述的源极电极相连的第二导电型重掺杂深阱区、位于第二导电型重掺杂深阱区之间的第二导电型阱区、位于第二导电型阱区上方的第一导电型重掺杂源极区和第二导电型重掺杂接触区,其特征在于,所述的第二导电型重掺杂深阱区左右侧壁分别设有深度浅于所述的第二导电型重掺杂深阱区的第一沟槽栅和第二沟槽栅,所述的第一沟槽栅和第二沟槽栅顶部分别设有层间介质层,所述的层间介质层分别向外侧延伸覆盖部分第一导电型重掺杂源极区,所述的第一沟槽栅和第二沟槽栅包括栅介质层和填充在栅介质层内的导电介质层。

2.如权利要求1所述的π型沟槽栅碳化硅mosfet器件,其特征在于,所述的第二导电型阱区下方设有第一导电型电流扩展层,所述的第一导电型电流扩展层的掺杂浓度高于第一导电型轻掺杂外延层且低于第二导电型重掺杂深阱区。

3.如权利要求1所述的π型沟槽栅碳化硅mosfet器件,其特征在于,所述的源极电极与位于第一沟槽栅和第二沟槽栅之间部分的第二导电型重掺杂深阱区相连通。

4.如权利要求1所述的π型沟槽栅碳化硅mosfet器件,其特征在于,第一沟槽栅和第二沟槽栅的下方和中间均设有第二导电型重掺杂深阱区。

技术总结一种π型沟槽栅碳化硅MOSFET器件,本技术涉及功率半导体器件,为了在不增加器件的沟道电阻和工艺复杂度的条件下实现对沟槽栅氧化层的保护,在第二导电型重掺杂深阱区左右侧壁分别设有深度浅于所述的第二导电型重掺杂深阱区的第一沟槽栅和第二沟槽栅,其中第一沟槽栅和第二沟槽栅顶部分别设有层间介质层,层间介质层分别向外侧延伸覆盖部分第一导电型重掺杂源极区,第一沟槽栅和第二沟槽栅包括栅介质层和填充在栅介质层内的导电介质层,本发明可以通过控制第一沟槽栅和第二沟槽栅之间的间距减小元胞等效的周期长度,从而提高沟道密度,降低沟道电阻。技术研发人员:刘永,冯浩,单建安受保护的技术使用者:安建科技(深圳)有限公司技术研发日:20231124技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/180196.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表