通过含硅反应物辅助的低温钼沉积的制作方法

- 国知局

- 2024-07-31 18:58:24

本发明涉及半导体设备制造的方法。具体而言,本发明的实施方案涉及在半导体处理中的含钼膜沉积。

背景技术:

1、在半导体设备的制造中,沉积和蚀刻技术用于形成材料图案,例如用于形成嵌入介电层中的金属线。一些图案化方案需要材料的保形沉积,其中沉积层应遵循衬底表面上的突起和/或凹陷特征的轮廓。原子层沉积(ald)通常是在衬底上形成保形膜的优选方法,因为ald依赖于一种或多种反应物(前体)吸附到衬底表面,以及吸附层随后化学转化为所需的材料。由于ald使用发生在衬底表面上的顺序反应,这些反应在时间上是分开的,并且通常受吸附反应物的量的限制,因此该方法可以提供具有出色台阶覆盖率的薄保形层。

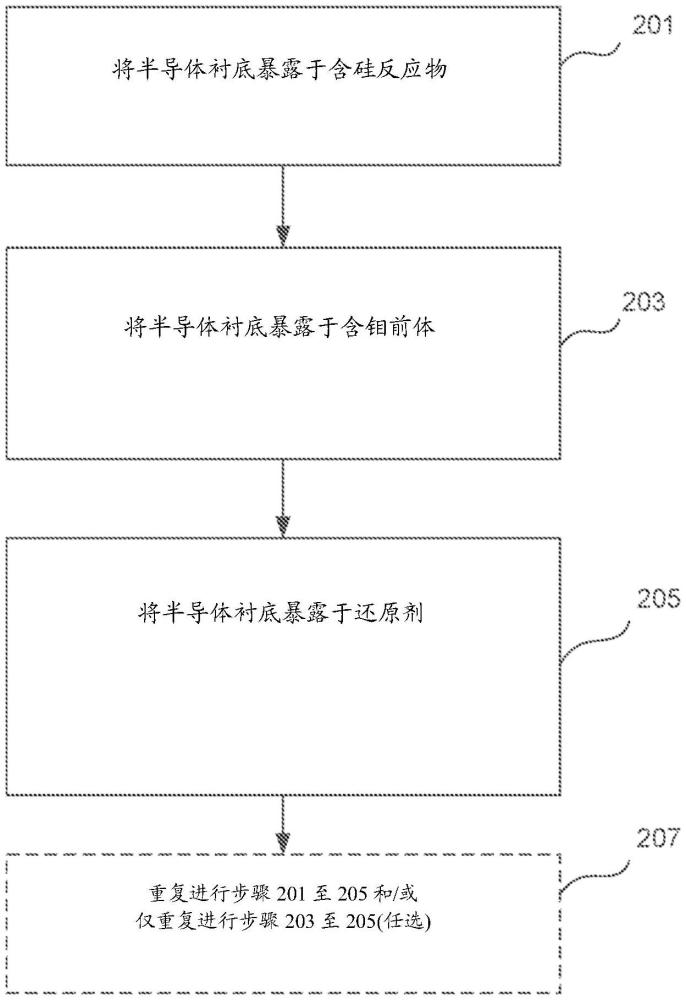

2、化学气相沉积(cvd)是另一种广泛用于半导体处理的沉积方法。在cvd中,反应发生在处理室的体积中,并且不受吸附到衬底上的反应物数量的限制。因此,cvd沉积膜通常不如ald沉积膜保形。cvd通常用于台阶覆盖率不太重要的应用中。

3、ald和cvd可以使用等离子体来促进沉积前体的反应,从而形成所需的膜。利用等离子体的方法被称为等离子体增强ald(peald)和等离子体增强cvd(pecvd)。不使用等离子体的方法称为热ald和热cvd。

4、虽然ald及cvd最通常被用于含硅膜(例如,硅氧化物、硅氮化物及硅碳化物)的沉积,但这些方法也适用于某些金属的沉积。

5、这里提供的背景描述是为了总体呈现本公开的背景的目的。当前指定的发明人的工作在其在此背景技术部分中描述的范围内以及在提交申请时不能确定为现有技术的说明书的各方面既不明确也不暗示地承认是针对本公开的现有技术。

技术实现思路

1、本文提供了通过在介于约100℃与约500℃之间的相对低温下还原含钼前体而沉积金属钼的方法。所述方法利用含硅反应物来改善含钼前体的还原和/或调整钼沉积的选择性。在一些实施方案中,所述方法用于在包括不同暴露材料(例如,暴露金属和暴露电介质)的半导体衬底上沉积钼金属。例如,含钼层可以基本无选择性地沉积在凹陷特征中,其中所述凹陷特征在侧壁处具有暴露电介质材料,而在底部处具有暴露金属。所提供的钼沉积方法例如可以用于间隙填充应用。虽然所提供的方法特别适用于沉积含钼层,但它们也可用于沉积具有可蒸发前体的其他金属,例如钴、钌和钨。

2、在一方面,提供了一种在半导体衬底上形成含钼层的方法。该方法包括:(a)将半导体衬底提供至处理室,其中所述半导体衬底具有凹陷特征;以及(b)在介于约100℃与约500℃之间的温度下将所述半导体衬底暴露于含钼前体、还原剂和含硅反应物以还原所述含钼前体并且在所述半导体衬底上形成含钼层,其中所述含钼层包括钼金属层。在一些实施方案中,所形成的所述含钼层还包括钼硅化物子层。

3、在一些实施方案中,所述含钼前体为moxnym,其中x为硫族元素(chalcogen),y为卤素,n为0、1或2,而m为2、3、4、5或6。

4、合适含钼前体的示例包括mocl5、mo2cl10、moo2cl2、moocl4或其任何组合。

5、在一些实施方案中,所述含硅反应物为sixry,其中x为1-4,y为4-18,且每个r独立地选自由h、卤素和烷基所构成的群组。合适含硅反应物的示例包括硅烷、氯硅烷、二氯硅烷、三氯硅烷、四氯硅烷、六氯乙硅烷、五氯乙硅烷、四氯乙硅烷、三氯乙硅烷、二氯乙硅烷、氯乙硅烷、乙硅烷或其任何组合。

6、在一实现方案中,所述还原剂为氢(h2),且将所述半导体衬底暴露于含钼前体、还原剂和含硅反应物包括:(i)在未将所述含钼前体输送至所述处理室的情况下,将所述半导体衬底与所述含硅反应物接触一段时间;以及(ii)在(i)后,使所述半导体衬底接触所述含钼前体,以及使所述半导体衬底接触h2。在一些实施方案中在未同时将氢输送至所述处理室的情况下,使所述半导体衬底接触所述含钼前体。在其他实施方案中,所述半导体衬底同时接触所述含钼前体和氢。在一些实施方案中,所述沉积方法包括重复进行步骤(i)和(ii)。在一些实施方案中,步骤(ii)包括使所述半导体衬底依次接触所述含钼前体和所述还原剂,并且重复使所述半导体衬底依次接触所述含钼前体和所述还原剂。在一些实施方案中,所述方法还包括:(iii)在步骤(ii)之后使所述半导体衬底接触所述含硅反应物。

7、在一些实现方案中,所述还原剂为氢(h2),且将所述半导体衬底暴露于含钼前体、还原剂及含硅反应物包括:将所述半导体衬底同时接触氢、所述含钼前体和所述含硅反应物。

8、在一些实现方案中,所述还原剂为氢(h2),且将所述半导体衬底暴露于含钼前体、还原剂和含硅反应物包括:(i)使所述半导体衬底同时接触氢和所述含硅反应物;以及(ii)在未同时将所述含硅反应物输送至所述处理室的情况下,使所述半导体衬底接触所述含钼前体。

9、在一些实现方案中,所述还原剂为氢(h2),且将所述半导体衬底暴露于含钼前体、还原剂及含硅反应物的步骤包括:(i)使所述半导体衬底同时接触所述含钼前体和所述含硅反应物;以及(iii)在未同时将所述含硅反应物输送至所述处理室的情况下,使所述半导体衬底接触氢。

10、在一些实施方案中,在所述半导体衬底上提供的所述凹陷特征包括位于所述凹陷特征的多个侧壁上的暴露含硅电介质,以及在所述凹陷特征的底部处暴露的金属(例如,钨或钴),其中所述含钼层以约1.3:1(底部比侧壁)以下的选择性沉积在所述凹陷特征的所述底部上及所述凹陷特征的所述侧壁上。在一些实施方案中,所述方法包括以所述含钼层完全填充所述凹陷特征,其中所述含钼层包括钼金属层。

11、在一些实施方案中,本文所提供的方法系与光刻处理整合在一起。例如,所述方法可以包括下列步骤:将光致抗试剂涂覆于所述半导体衬底;将所述光致抗试剂曝光;将所述光致抗试剂图案化,并且将所述图案转移至所述半导体衬底;以及将所述光致抗试剂从所述半导体衬底选择性移除。例如,这样的光刻图案化可以用于在沉积含钼材料之前,在所述衬底上形成凹陷特征。

12、在另一方面,提供了一种半导体衬底的处理装置,其中所述装置包括:(a)处理室,其具有用于保持所述半导体衬底的衬底保持件和用于将反应物引进所述处理室的一或更多个输入口;以及(b)控制器,其包括程序指令,所述程序指令用于致使本文所提供的任何方法的执行。例如,所述程序指令可以包括用于导致以下操作的指令:在具有凹陷特征的半导体衬底上,在介于约100℃与约500℃之间的温度下致使所述半导体衬底接触含钼前体、还原剂和含硅反应物,从而形成含钼材料层。例如,在一些实施方案中,所述程序指令可以被配置成导致:(i)在未同时将所述含钼前体输送至所述处理室的情况下,使所述半导体衬底接触含硅反应物;以及(ii)在(i)后,使所述半导体衬底接触所述含钼前体和氢。在一些实施方案中,所述程序指令包括被配置成导致以下操作的指令:(i)在未将所述含钼前体输送至所述处理室的情况下,使所述半导体衬底同时接触氢和所述含硅反应物;以及(ii)在未同时将所述含硅反应物输送至所述处理室的情况下,使所述半导体衬底接触所述含钼前体。在一些实施方案中,所述程序指令包括被配置成导致以下操作的指令:(i)在未同时将氢输送至所述处理室的情况下,使所述半导体衬底同时接触所述含钼前体和所述含硅反应物;以及(ii)在未同时将所述含硅反应物输送至所述处理室的情况下,使所述半导体衬底接触氢。

13、在另一方面,提供了一种计算机机器可读介质,其包括致使本文所提供的任何方法的步骤进行的代码。例如,可以提供代码,其用于:在具有凹陷特征的半导体衬底上,在介于约100℃与约500℃之间的温度下致使所述半导体衬底接触含钼前体、还原剂和含硅反应物,从而形成含钼材料层。

14、在另一方面,提供了一种系统,其包括本文所述的装置和步进器。

15、在另一方面,提供了一种在半导体衬底上形成含金属层(例如,含钼层、含钨层、含钴层或含钌层)的方法。在一些实施方案中,所述方法包括:(a)将半导体衬底提供至处理室,其中所述半导体衬底具有凹陷特征;以及(b)在介于约100℃与约500℃之间的温度下将所述半导体衬底暴露于金属前体(例如,钼前体、钨前体、钴前体或钌前体)、还原剂及含硅反应物,从而还原所述金属前体,并且在所述半导体衬底上形成含金属层,其中所述含金属层包括零氧化态的金属(例如,钼、钨、钴或钌)层。在一些实施方案中,所述含金属层包括金属硅化物(例如,钼硅化物、钨硅化物、钴硅化物或钌硅化物)层。

16、本说明书中所描述的目标主体的实现方案的这些及其他方面系于随附图式及下方的实施方式中阐述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181191.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表