一种防止隔离沟槽缺陷的方法及半导体制备方法与流程

- 国知局

- 2024-07-31 19:00:29

本发明涉及半导体,尤其是涉及一种防止隔离沟槽缺陷的方法及半导体制备方法。

背景技术:

1、半导体器件发展至今,sti(shal low trench isolation,浅沟隔离)技术已经在0.18微米以及以下制程广泛应用,伴随摩尔定律,器件尺寸不断下探至3纳米,沟槽临界尺寸(trench cd)也对应压缩,制程越发精细的同时对通过化学机械抛光技术加工sti(cmpsti layer process)也带来新的挑战,现今在对应站点,化学机械抛光技术(cmp)后通常会发现凹陷(dishing)和侵蚀缺陷(erosion defect),特别是间隙填充(gap fi l l)要求比较高的制程。

2、现有的防止隔离沟槽缺陷的方法通常是采用浅沟隔离工具将硅氮化物作为化学抛光过程的停止层,但是依然无法有效避免出现凹陷和侵蚀缺陷。

技术实现思路

1、本发明提供一种防止隔离沟槽缺陷的方法及半导体制备方法,以解决现有的防止隔离沟槽缺陷的方法通常是采用浅沟隔离工具将硅氮化物作为化学抛光过程的停止层,但是依然无法有效避免出现凹陷和侵蚀缺陷的技术问题。

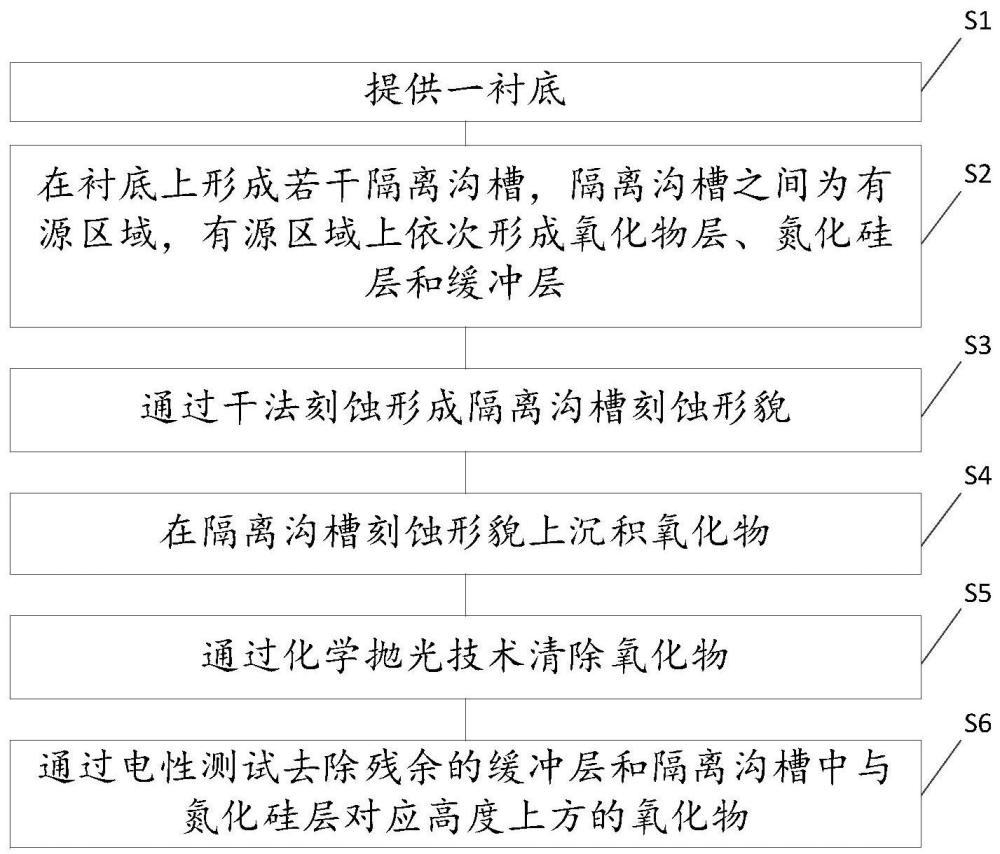

2、本发明提供了一种防止隔离沟槽缺陷的方法,包括:

3、提供一衬底;

4、在所述衬底上形成若干隔离沟槽,所述隔离沟槽之间为有源区域,所述有源区域上依次形成氧化物层、氮化硅层和缓冲层;

5、通过干法刻蚀形成隔离沟槽刻蚀形貌;

6、在所述隔离沟槽刻蚀形貌上沉积氧化物;

7、通过化学抛光技术清除所述氧化物;

8、通过电性测试去除残余的所述缓冲层和所述隔离沟槽中与所述氮化硅层对应高度上方的氧化物。

9、进一步的,所述缓冲层为多晶硅层。

10、进一步的,所述衬底为晶圆衬底。

11、进一步的,所述通过干法刻蚀形成隔离沟槽刻蚀形貌,包括:

12、对所述晶圆衬底的表面进行湿法处理;

13、在所述晶圆衬底的表面形成保护层薄膜;

14、在所述保护层薄膜上掺杂多晶硅;

15、通过光刻工艺依次进行上光阻、曝光和显影处理后,形成隔离沟槽图案;

16、根据所述隔离沟槽图案对所述隔离沟槽的背面进行刻蚀处理,形成隔离沟槽刻蚀形貌。

17、进一步的,所述在所述晶圆衬底的表面形成保护层薄膜,包括:

18、通过沉积方式或高温方式在所述晶圆衬底的表面形成一层氧化硅薄膜后,再形成一层氮化硅薄膜,所述氧化硅薄膜和所述氮化硅薄膜为保护层薄膜。

19、进一步的,所述在所述保护层薄膜上掺杂多晶硅,包括:

20、在所述保护薄膜上掺杂多晶硅后,掺杂增强型低介电常数材料,或通过光刻工艺附上顶部抗反射涂层和底部抗反射涂层。

21、进一步的,所述在所述隔离沟槽刻蚀形貌上沉积氧化物,包括:

22、在所述隔离沟槽刻蚀形貌上通过半导体薄膜沉积技术沉积氧化物。

23、进一步的,所述半导体薄膜沉积技术包括高密度等离子体化学气相沉积和亚大气化学气相沉积。

24、本发明还提供了一种半导体制备方法,包括:

25、采用如上述的防止隔离沟槽缺陷的方法制备得到隔离沟槽;

26、基于所述隔离沟槽制备得到半导体。

27、本发明还提供了一种半导体,采用如上述的半导体制备方法制备得到,包括:

28、衬底,在衬底上方形成的隔离沟槽,以及在所述隔离沟槽之间的有源区域;

29、所述有源区域包括依次向上形成的氧化物层和氮化硅层;

30、所述隔离沟槽的填充物为氧化物。

31、本发明通过在氮化硅层顶部增加一层缓冲层,在移除氮化硅层之前,该缓冲层能够在隔离沟槽形成凸起轮廓,在进行化学机械抛光技术过程中,能够起到缓冲作用,防止在处理隔离沟槽过程中,化学机械抛光过度导致出现凹陷和侵蚀缺陷。

32、进一步的,本发明的缓冲层为多晶硅层,能够填充氮化硅层表面的凹坑和坑洼,使得表面变得更加平坦,有利于提高后续光刻和薄膜沉积的制备性能;且还能够在化学抛光过程中提供结构支撑,减少半导体结构在化学抛光过程中的损坏风险。

技术特征:1.一种防止隔离沟槽缺陷的方法,其特征在于,包括:

2.如权利要求1所述的防止隔离沟槽缺陷的方法,其特征在于,所述缓冲层为多晶硅层。

3.如权利要求1所述的防止隔离沟槽缺陷的方法,其特征在于,所述衬底为晶圆衬底。

4.如权利要求3所述的防止隔离沟槽缺陷的方法,其特征在于,所述通过干法刻蚀形成隔离沟槽刻蚀形貌,包括:

5.如权利要求4所述的防止隔离沟槽缺陷的方法,其特征在于,所述在所述晶圆衬底的表面形成保护层薄膜,包括:

6.如权利要求4所述的防止隔离沟槽缺陷的方法,其特征在于,所述在所述保护层薄膜上掺杂多晶硅,包括:

7.如权利要求1所述的防止隔离沟槽缺陷的方法,其特征在于,所述在所述隔离沟槽刻蚀形貌上沉积氧化物,包括:

8.如权利要求7所述的防止隔离沟槽缺陷的方法,其特征在于,所述半导体薄膜沉积技术包括高密度等离子体化学气相沉积和亚大气化学气相沉积。

9.一种半导体制备方法,其特征在于,包括:

10.一种半导体,其特征在于,采用如权利要求9所述的半导体制备方法制备得到,包括:

技术总结本发明公开了一种防止隔离沟槽缺陷的方法及半导体制备方法,其中防止隔离沟槽缺陷的方法包括:提供一衬底;在衬底上形成若干隔离沟槽,隔离沟槽之间为有源区域,有源区域上依次形成氧化物层、氮化硅层和缓冲层;通过干法刻蚀形成隔离沟槽刻蚀形貌;在隔离沟槽刻蚀形貌上沉积氧化物;通过化学抛光技术清除氧化物;通过电性测试去除残余的缓冲层和隔离沟槽中与氮化硅层对应高度上方的氧化物。本发明通过在氮化硅层顶部增加一层缓冲层,在移除氮化硅层之前,该缓冲层能够在隔离沟槽形成凸起轮廓,在进行化学机械抛光技术过程中,能够起到缓冲作用,防止化学机械抛光过度导致出现凹陷和侵蚀缺陷。技术研发人员:柯才受保护的技术使用者:粤芯半导体技术股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181322.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表