一种DDR多比特ecc错误处理方法与流程

- 国知局

- 2024-07-31 19:15:40

本发明涉及存储器领域,具体涉及一种ddr多比特ecc错误处理方法。

背景技术:

1、双倍速率同步动态随机存储器(ddr)在高频率的工作状态下,有时会出现内存阵列位翻转,进而导致数据位产生错误。当单一bit出现错误时,ddr控制器一般可通过ecc(错误检查和纠正)校验位内部识别出具体bit位置后根据寄存器自行纠正,但当多bit出现错误时,ddr控制器只能识别多bit错误的对应地址而无法识别多bit错误本身,此时,若ddr控制器将出现多bit错误的数据返回到cpu用于后续程序运行,则会出现运行错误。

2、现有技术中,针对不同多bit错误应具有不同的处理方法,若多bit错误由软件引起,则需要通过备份数据进行纠正,若多bit错误由硬件引起,则需要判断数据出现错误是因为地址线间短路还是颗粒故障。

技术实现思路

1、本发明提供了一种ddr多比特ecc错误处理方法,可对具体出现的多bit错误判断数据出现错误的原因。

2、本申请的技术方案为:

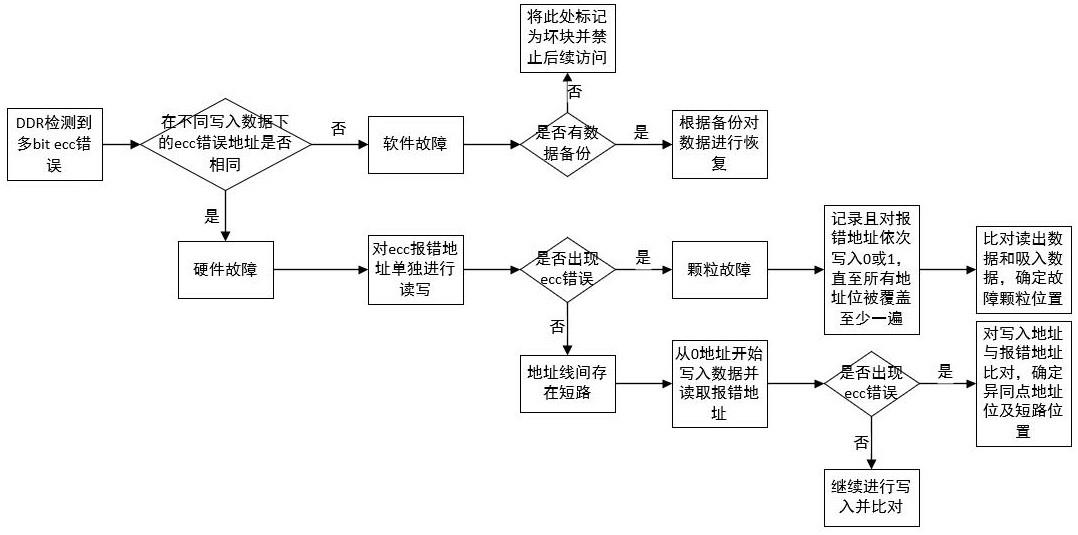

3、一种ddr多比特ecc错误处理方法,包括以下步骤:

4、s01)ddr控制器检测在不同写入数据下的ecc错误地址是否相同;

5、s02)若否,ddr控制器判定该ecc错误为软件故障;若是,ddr控制器判定该ecc错误为硬件故障;

6、s03)当ecc错误为硬件故障时,对ecc报错地址单独进行读写;

7、s04)根据读写结果判定ecc报错地址处是否出现ecc错误;

8、s05)若是,则判定为颗粒故障;

9、若否,则判定地址线间存在短路;

10、s06)当判定为颗粒故障时:对所述报错地址依次写入0或1,直至所有地址位均被0和1覆盖至少一遍;写入时,记录每次写入数据;写入后,将读出数据与所记录的写入数据比对后得出bit翻转位置,进而确定颗粒故障位置;

11、当判定为地址线间存在短路时,从0地址开始写入数据并在每次写入数据后读取所述报错地址数据,判定检测是否出现ecc错误;

12、若是,则对写入地址与所述报错地址的地址位进行比对,以通过异同点确定出现错误的地址位,根据出现错误的地址位检查通路上具体出现短路的位置;

13、若否,则继续进行写入并进行下一次比对。

14、进一步地,所述步骤s02)中,当ecc错误为软件故障时,检测ddr是否具有备份数据;若是,则根据备份数据对写入数据进行修复;若否,则将此处标记为坏块并禁止后续访问。

15、本发明的有益效果是:

16、1.本发明提供了针对多bit ecc错误的处理方法,提高了内存系统的稳定性。

17、2.当ddr产生多bit ecc错误时,硬件故障可被识别为颗粒故障或地址位短路,提高了故障识别效率。识别完成后,针对不同的故障种类采用不同的读写方式,可提高错误识别的准确率,可使用户快速对故障进行修复。

18、3.对颗粒故障的定位免去了逐一更换颗粒的繁琐步骤,也降低了维修成本。

技术特征:1.一种ddr多比特ecc错误处理方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种ddr多比特ecc错误处理方法,其特征在于,

技术总结本发明涉及存储器技术领域,具体涉及一种DDR多比特ecc错误处理方法,包括以下步骤:S01)DDR控制器检测在不同写入数据下的ecc错误地址是否相同;S02)判定该ecc错误为软件故障或硬件故障;S03)当ecc错误为硬件故障时,对ecc报错地址单独进行读写;S04)根据读写结果判定ecc报错地址处是否出现ecc错误;S05)若是,则判定为颗粒故障;若否,则判定地址线间存在短路;S06)对不同的故障类型进行不同方式的修复。本发明可提高错误识别的准确率,可使用户快速对故障进行修复,提高了内存系统的稳定性,降低了维修成本。技术研发人员:白祯帅,粟如发,王璞受保护的技术使用者:山东华芯半导体有限公司技术研发日:技术公布日:2024/1/16本文地址:https://www.jishuxx.com/zhuanli/20240731/182066.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表