一种基于反向器随机击穿的PUF电路、芯片及应用方法与流程

- 国知局

- 2024-07-31 19:16:58

本发明涉及芯片安全领域的安全芯片密钥产生技术,具体涉及一种基于反向器随机击穿的puf电路、芯片及应用方法。

背景技术:

1、在安全芯片中,通常采用物理不可克隆函数(physically unclonable function,puf)提供安全芯片所需的密钥,puf检测的是集成电路生产过程中构成电路器件的材料物理特性的随机变化,即使是芯片制造厂商和电路设计者也不可能采用相同的电路复制出完全相同的密钥,攻击者更无法通过反向工程推出原始密钥。现今存在多种puf结构,如基于延迟单元的瞬态效应环形振荡器型和arbiter型puf,基于环形振荡器振荡频率差异性的ro型puf,基于最小数据保持电压检测的sram puf,基于阻变式随机存储器和磁随机存储器的puf等,但这些传统puf采样的是器件或者电路的噪声、阻值、振荡频率、延时、阈值电压等特性之间的失配,极易受电压、温度影响,而新型磁随机存储器等新型存储器则与标准cmos工艺不兼容,需要进行特殊处理,大大增加了芯片成本。此外,采用举手表决和纠错码(errorcorrection code,ecc)对不稳定puf单元进行生产后修调的方式也会带来较大的数字电路开销。因此,现有传统puf存在稳定性不高、校正硬件成本较高等问题。

2、为了避免传统puf对电路或者器件的模拟特征进行采样带来的稳定性不高的问题,有研究提出了通-断(on-off)型puf,一种非常简单的设计方案是将两根金属互联线的间距缩小至小于工艺所能够允许的最小间距,在芯片实际生产过程中,由于工艺光刻分辨率有限,从而有可能使得两根互联线连接在一起,且连接概率受工艺随机偏差影响,实际芯片生产后两根互联线的连接状态将随机通或者断。这种puf实现方式不受温度和环境影响,互联线是通还是断在芯片生产后就永久确定,具有100%的稳定性,且实现成本也非常低,无需额外的校正电路。但需要指出的是,该种实现方式较难控制puf密钥的偏置特性,互联线之间连接状态极易受距离影响,距离稍远则两根互联线大概率不相交,而距离稍近则大概率相交,要想获得50%的相交概率将非常困难,需要对工艺本身进行多次分析和迭代以获得合适的间距,且每次投片的情况也会不一样,要实现不同工艺情况下的收敛对设计而言非常困难,极易受工艺影响。

3、为了获取较好的偏置特性,另外一种有效的通-断puf实现方式是采用片上mos晶体管击穿的方式获得永久稳定的puf密钥。现有技术[puf value generation using ananti-fuse memory array,wo 2017/117663 al]提出了一种基于芯片内部两个nmos晶体管随机击穿的puf电路,如图1所示,nmos1和nmos2为尺寸较小的n型mos晶体管,且nmos1和nmos2串联。整个puf分为两个阶段:(1)puf密钥生成阶段。此时,nmos1的源、漏极分别和nmos2的源、漏极相连,且栅极均接外部输入高压信号。当输入高压信号大至mos晶体管的击穿电压后,由于nmos1和nmos2尺寸和外部环境完全一致,两个晶体管被击穿的可能性相等,均为50%。当有晶体管被击穿后,puf进入密钥提取阶段。(2)puf密钥提取阶段。此时,两个晶体管的栅极分别接采样电压vsense和地gnd。若在阶段(1)中nmos1栅-源被击穿,则vsense直接与被击穿的源端相通,nmos2截止,输出点为vsense电压,经过比较器比较后,输出为逻辑“1”;反之,若在阶段(1)中nmos2栅-源被击穿,则gnd直接与被击穿的源端相通,即使nmos1处于导通的状态,输出点仍为gnd电压,经过比较器比较后,输出为逻辑“0”。

4、该种实现方式能够获取受工艺影响较小的偏置特性,但同时也面临以下问题:

5、(1)该种电路结构需要特殊的mos晶体管结构,无法与标准cmos工艺兼容,实现成本高。为了使晶体管栅极施加高压时实现栅源击穿,避免栅-漏和栅-衬底的击穿,以实现puf密钥提取阶段vsense或gnd与输出点的直连,mos晶体管需要采用特殊反熔丝结构,在靠近漏端范围,必须要添加厚场氧化层,以使栅-漏之间的击穿阈值更高,避免先出现栅-漏的击穿,且通过控制栅极电压,能够保证栅-源击穿发生在栅-衬击穿之前。

6、(2)该种结构易出现不稳定单元。虽然mos晶体管要么被击穿,要么不被击穿,不存在第三种状态,具有较高的稳定性,但由于可能出现2个晶体管均被击穿的情况,可能导致puf密钥不稳定。例如,若在puf密钥生成阶段栅极施加的高压较大,导致nmos1和nmos2均被击穿,则vsense和gnd直接通过击穿电阻连接在一起,首先存在较大的漏电,更重要的是输出端电压可能处于vsense和gnd之间任意电压,此时其与vref比较后,输出值可能为“1”,也可能为“0”,导致该种情况下puf密钥不稳定。

7、(3)此外,该种电路结构需要采用比较器和基准电压产生电路,电路成本高。

8、综上可以看出,现有基于晶体管击穿的通断型puf存在需要特殊工艺、电路成本高、易产生不稳定单元等问题,需寻找一种成本低、稳定性高的电路结构,避免特殊结构晶体管的使用,并提升两个晶体管均被击穿后puf密钥的稳定性。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种基于反向器随机击穿的puf电路、芯片及应用方法,本发明旨在实现简单的基于反向器中nmos管或pmos管随机熔断的、与标准cmos工艺兼容、成本低的高稳定性通断型puf电路,避免特殊结构晶体管的使用,并提升两个晶体管均被击穿后puf密钥的稳定性。

2、为了解决上述技术问题,本发明采用的技术方案为:

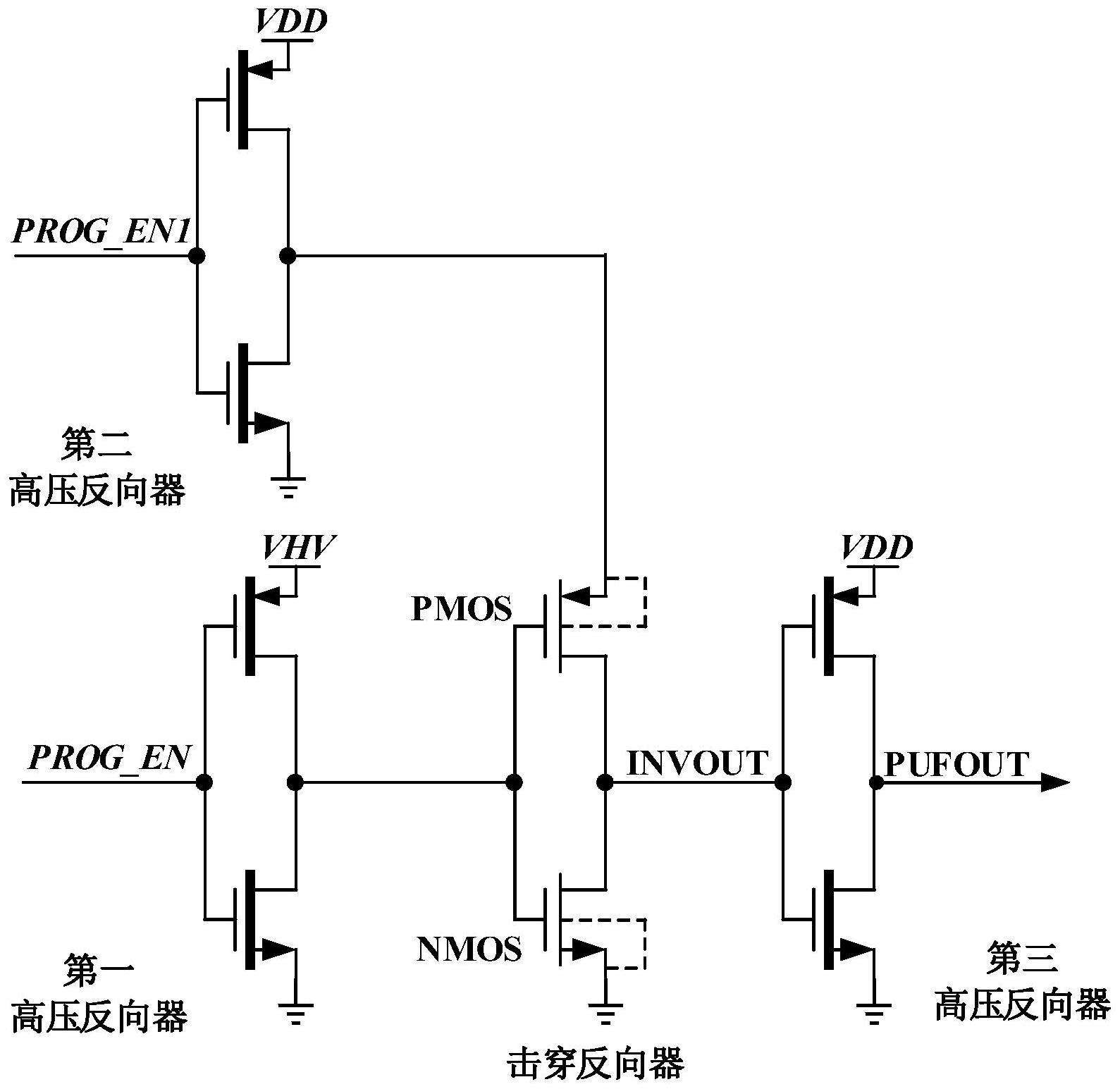

3、一种基于反向器随机击穿的puf电路,包括由尺寸、栅极厚度相同的nmos晶体管和pmos晶体管构成的击穿反向器,所述nmos晶体管和pmos晶体管的栅极共同作为击穿反向器的输入端,pmos晶体管和nmos晶体管的漏端作为击穿反向器的输出端,pmos晶体管的源端作为击穿反向器的电源端,nmos晶体管的源端接地,所述击穿反向器的输入端连接有用于在栅极高压vhv和地gnd之间选择的第一高压反向器,所述击穿反向器的电源端连接有用于在电源vdd和地gnd之间选择的第二高压反向器,且在输入端输入栅极高压vhv时nmos晶体管和pmos晶体管两者均发生栅极-衬底随机击穿以生成随机为“0”和“1”的puf密钥。

4、可选地,所述在输入端输入栅极高压vhv时nmos晶体管和pmos晶体管两者均发生栅极-衬底随机击穿时,若仅nmos晶体管的栅极-衬底被击穿时使得击穿反向器puf密钥为“1”,若仅pmos晶体管的栅极-衬底被击穿时使得击穿反向器的puf密钥为“0”,若nmos晶体管、pmos晶体管的栅极-衬底均被击穿时使得击穿反向器的puf密钥为“0”。

5、可选地,所述pmos晶体管的衬底电位钳制点与pmos沟道的间距大于设定值,以防止pmos晶体管的栅极-衬底被击穿时栅极低电位与pmos衬底所接的电源vdd之间形成的漏电流小于设定值。

6、可选地,所述击穿反向器的输出端连接有用于将puf密钥反向整形输出的第三高压反向器。

7、可选地,所述第三高压反向器由通过源端和漏端串联在电源vdd和地gnd之间的第三nmos晶体管和第三pmos晶体管构成,所述第三nmos晶体管和第三pmos晶体管的栅极作为第三高压反向器的输入端,所述第三nmos晶体管和第三pmos晶体管的漏端作为第三高压反向器的输出端,所述第三nmos晶体管的宽长比小于第三pmos晶体管的宽长比。

8、可选地,所述第一高压反向器由通过源端和漏端串联在栅极高压vhv和地gnd之间的第一nmos晶体管和第一pmos晶体管构成,所述第一nmos晶体管和第一pmos晶体管的栅极作为第一高压反向器的输入端连接控制信号prog_en,所述第一nmos晶体管和第一pmos晶体管的漏端作为第一高压反向器的输出端以输出最终的puf密钥pufout。

9、可选地,所述第二高压反向器由通过源端和漏端串联在电源vdd和地gnd之间的第二nmos晶体管和第二pmos晶体管构成,所述第二nmos晶体管和第二pmos晶体管的栅极作为第二高压反向器的输入端连接控制信号prog_en1,所述第二nmos晶体管和第二pmos晶体管的漏端作为第二高压反向器的输出端。

10、此外,本发明还提供一种puf电路,包括n个前文所述基于反向器随机击穿的puf电路以用于共同组合生成n位的puf密钥。

11、此外,本发明还提供一种芯片,包括芯片本体和设于芯片本体中的puf电路,所述puf电路为前文所述puf电路。

12、此外,本发明还提供一种前述所述基于反向器随机击穿的puf电路的应用方法包括:

13、s101,在puf密钥生成阶段,将控制信号prog_en置为“0”,击穿反向器的输入端通过第一高压反向器接入到栅极高压vhv,同时将控制信号prog_en1置为“1”,使得击穿反向器的电源端通过第二高压反向器接到地gnd,使得nmos晶体管和pmos晶体管两者均发生栅极-衬底随机击穿以生成随机为“0”和“1”的puf密钥;

14、s102,在puf密钥提取阶段,将控制信号prog_en置为“1”,击穿反向器的输入端接地gnd,同时将控制信号prog_en1置为“0”,使得击穿反向器的电源端通过第二高压反向器接到电源vdd,此时将根据击穿反向器中被击穿mos管类型的不同得到不同的puf密钥:(1)若仅nmos晶体管的栅极-衬底被击穿时使得击穿反向器puf密钥为“1”,并经过第三高压反向器反向并整形后输出最终的puf密钥pufout为“0”;(2)若仅pmos晶体管的栅极-衬底被击穿时使得击穿反向器puf密钥为“0”,并经过第三高压反向器反向并整形后输出最终的puf密钥pufout为“1”;(3)若nmos晶体管、pmos晶体管的栅极-衬底均被击穿时使得击穿反向器的puf密钥为“0”,并经过第三高压反向器反向并整形后输出最终的puf密钥pufout为“1”;

15、s103,在密钥提取完毕后,将控制信号prog_en和控制信号prog_en1均置为“0”,使得击穿反向器的输入端和电源端均接地以防止击穿反向器中的pmos晶体管被击穿时产生电源端与输入端之间的漏电。

16、和现有技术相比,本发明主要具有下述优点:本发明包括由尺寸、栅极厚度相同的nmos晶体管和pmos晶体管构成的击穿反向器,所述nmos晶体管和pmos晶体管的栅极共同作为击穿反向器的输入端,pmos晶体管和nmos晶体管的漏端作为击穿反向器的输出端,pmos晶体管的源端作为击穿反向器的电源端,nmos晶体管的源端接地,所述击穿反向器的输入端连接有用于在栅极高压vhv和地gnd之间选择的第一高压反向器,所述击穿反向器的电源端连接有用于在电源vdd和地gnd之间选择的第二高压反向器,且在输入端输入栅极高压vhv时nmos晶体管和pmos晶体管两者均发生栅极-衬底随机击穿以生成随机为“0”和“1”的puf密钥,本发明实现了简单的基于反向器中nmos管或pmos管随机熔断的、与标准cmos工艺兼容、成本低的高稳定性通断型puf电路,该puf电路无需特殊工艺的反熔丝晶体管,兼容标准cmos工艺;输出为确定的“0”或“1”,不存在中间状态;且无需基准电压产生电路和模拟比较器,电路简单,实现成本低,能够避免特殊结构晶体管的使用,并提升两个晶体管均被击穿后puf密钥的稳定性。本发明利用反向器中pmos或nmos被栅-衬击穿的可能性相同的特性获得为“0”、“1”概率均为50%的puf密钥,同时即使nmos和pmos均被击穿,puf密钥仍能够被稳定地提取,且pmos或nmos为最常用的cmos晶体管,无需特殊工艺,无需基准电压和模拟比较器,具有成本低、稳定性高的特点。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182153.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表