设置有按照使得最小化存储器块大小以允许管理行锤击效应的方式布置的DRAM存储器电路的存储器设备的制作方法

- 国知局

- 2024-07-31 19:20:32

本发明涉及存储器领域,并且特别地涉及动态随机存取存储器领域。特别地,本发明涉及存储器行锤击效应的管理。在这方面,本发明提出了一种存储器设备的架构,使得可以管理和防止针对大容量存储器设备的存储器行锤击效应,而不损害所述设备的性能。

背景技术:

1、动态随机存取存储器(“dram”)中的行锤击效应是本领域中的技术人员众所周知的。

2、该效应源于dram组的行的重复激活。更特别地,当被称为“攻击者行”的给定行的激活数量超过临界锤击值时,与其紧邻的被称为“受害者行”的行发现它们的位中的一些位被反转。

3、为了防止行锤击效应,可以设想在行变为攻击者之前,根据预防性刷新过程来刷新两个相邻受害者行。

4、在这方面,在文献fr3066842中描述了这种预防性刷新过程。该文献特别地公开了一种设置有用于检测行锤击的触发的逻辑部件的存储器设备。该检测逻辑部件被配置为监测和/或计数存储器设备的组或子组的每一行的激活的数量。在这方面,计数数据被存储在一个或更多个表中,该一个或更多个表的条目数量直接取决于存储器设备的大小(以及特别地存储器设备的容量)。

5、只要临界锤击值保持大于40000,从现有技术中已知的该存储器设备就特别高效。

6、然而,存储器设备的不断增加的容量需要考虑包括更多数量的条目的表,并且其因此消耗多得多的资源。

7、此外,如文献fr3066842中所提出的,当根据精细几何并且特别地以小于20nm的尺度制造存储器设备时,仅考虑在紧邻攻击者行的行处的行锤击达到其极限。

8、实际上,对更精细的图案或几何的考虑不可避免地导致增加行锤击效应的范围。特别地,存储器的组或子组的索引为“i”的攻击者行将不仅影响与其紧邻的行(具有索引“i-1”和“i+1”),而且在较小程度上影响具有索引“i-k”和“i+k”的行(其中“k”为严格大于1的整数)。

9、增大锤击效应的范围因此具有两种结果。首先,其有助于增加可以在文献fr3066842中考虑的表的大小。其次,其施加远低于40000或甚至低于4800的临界锤击值。

10、这两个组合效应直接影响在该文献中提出的用于检测行锤击的触发的逻辑部件的效果。

11、为了克服这些问题,在文献美国专利no.10,885,966中已提出了用于防止行锤击效应的另一算法。该文献也实现了表,并且考虑了超出紧邻攻击者行的行的锤击效应的范围。更特别地,为了限制对于其实现所必需的资源,所提出的算法监测按照子组级别的激活。

12、甚至比在文献fr3066842中提出的算法更高效的该算法可以针对某些存储器设备架构而被改善。

13、特别地,通常使用静态随机存取存储器(“sram”)块来实现该算法。然而,增加的存储器设备容量和所使用的几何的小的大小增加了对于适当执行用于防止行锤击效应的算法所必需的表的大小。

14、因此,这些因素使得有必要考虑具有更大容量的sram存储器块。然而,该类型的存储器消耗空间,并且能够显著增加存储器系统的总成本。

15、发明目的

16、本发明的一个目的是提出一种存储器设备,该存储器设备实现用于防止行锤击效应的算法,并且对于该存储器设备,sram存储器块具有有限的大小。

技术实现思路

1、本发明涉及一种存储器设备,并且更特别地,涉及如下存储器设备,当所述存储器设备的密度及其总容量增加时,该存储器设备的架构使得可以有效地管理行锤击效应。

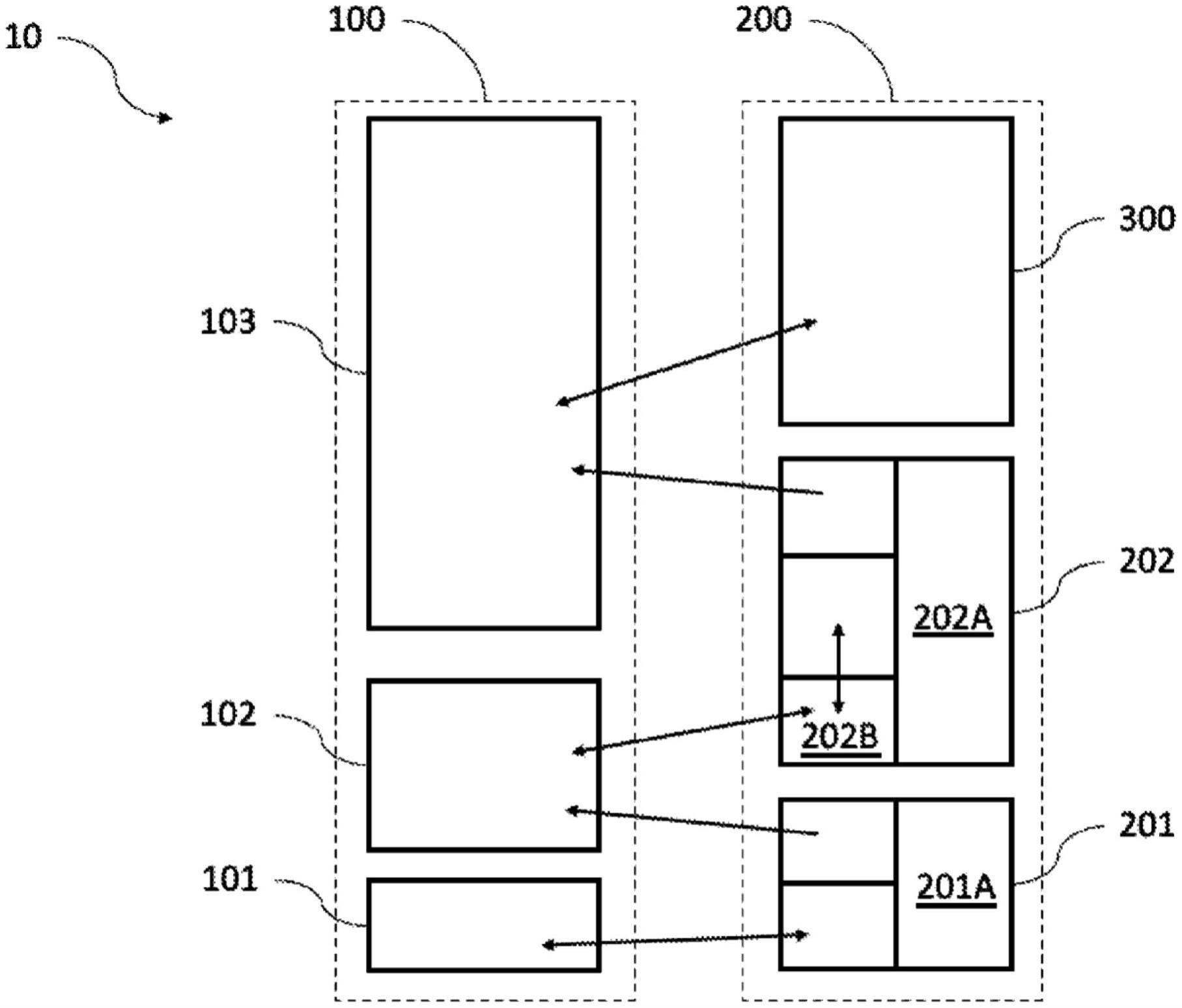

2、存储器设备包括“dram”类型的存储器电路,其总容量被划分为第一部分以及第二部分,该第一部分被称为“直接受保护部分”,该第二部分被称为“间接受保护部分”并且比第一部分大。

3、根据本发明,存储器设备包括控制电路,该控制电路实现分别被称为第一算法和第二算法的两种保护算法。

4、更特别地,控制电路包括实现第一算法的第一块以及实现第二算法的第二块。

5、在这方面,第一算法被配置为保护第一部分免受行锤击效应。

6、第二算法就其本身而言被配置为保护第二部分免受行锤击效应。第二算法特别地实现被保存在第一部分中的至少一个表,该表被称为主表。

7、本发明的目的通过一种存储器设备来实现,该存储器设备包括:

8、-存储器电路,这些电路包括“dram”类型的存储器,所述存储器电路的总容量被划分为第一部分以及第二部分,第一部分被称为“直接受保护部分”,第二部分被称为“间接受保护部分”并且比第一部分大;

9、-控制电路,该控制电路被配置为访问存储器电路,控制电路包括:

10、-第一块,该第一块被配置为执行第一算法,第一算法旨在保护第一部分免

11、受行锤击效应;

12、-第二块,该第二块被配置为执行第二算法,第二算法旨在保护第二部分免受可能发生的行锤击效应,第二算法使用被存储在第一部分中的主表;

13、根据一个实施方式,控制电路包括功能块,该功能块被配置为执行第二部分中的计算功能和程序,并且有利地也执行第一部分中的计算功能和程序。

14、根据一个实施方式,第一部分和第二部分被布置成使得由第一部分中的一行或第二部分中的一行施加的行锤击效应不被第一部分或第二部分中的另一者感觉到。

15、根据一个实施方式,第一部分和第二部分是根据以下配置中的一种配置被配置的:

16、-第一部分和第二部分不相交,以不共享dram存储器电路;

17、-第一部分和第二部分各自包括特定于它们的dram存储器电路组;

18、-在同一dram存储器电路组内,第一部分和第二部分各自包括特定于它们的一个或更多个子组,所述子组然后被布置成使得由第一部分的子组的行施加的行锤击效应不被第二部分的子组感觉到,并且由第二部分的子组的行施加的行锤击效应不被第一部分的子组感觉到;

19、-第一部分和第二部分共同具有被称为公共组的dram存储器电路组,所述公共组包括未使用的存储器行并且将公共组的与第一部分相关联的区段与公共组的与第二部分相关联的另一区段分开,未使用的存储器行的数量被选择为使得在公共组的两个区段中的各个区段之间不发生行锤击效应。

20、根据一个实施方式,第一部分的大小对应于第二部分的大小的小于0.1%。

21、根据一个实施方式,第一部分和第二部分能够相互施加行锤击效应,并且其中,第一算法和第二算法被配置为防止第一部分对第二部分的行锤击效应,并且被配置为防止第二部分对第一部分的行锤击效应。

22、根据一个实施方式,第二块包括高速缓存存储器,该高速缓存存储器旨在存储由第二算法使用的主表的数据。

23、根据一个实施方式,第一块使用被称为初始表的表,该初始表通过第一算法来实现并且被存储在被称为保护存储器块的存储器中。

24、根据一个实施方式,第一算法为不需要初始表的概率算法。文献“flipping bitsin memory without accessing them:an experimental study of dram disturbanceerrors”例如公开了“para”算法(概率相邻行激活),其代表不需要任何表的概率算法。

25、根据一个实施方式,第一块包括高速缓存存储器,该高速缓存存储器旨在存储来自由第一算法使用的初始表的数据并且位于保护存储器块中,当保护存储器块的性能受限时,使用这种高速缓存存储器是有利的。

26、根据一个实施方式,保护存储器块包括不受行锤击效应影响的存储器,特别地在非限制性示例中,所述存储器可以为sram、mram或cnram存储器。

27、根据一个实施方式,保护存储器块包括dram存储器,并且其中,存储器行被布置成防止所述块内的任何行锤击。

28、根据一个实施方式,保护存储器块包括dram存储器,并且其中,刷新速率增加以防止所述块内的任何行锤击。

29、根据一个实施方式,保护存储器块包括dram存储器,并且其中,电屏蔽将行分开,以防止所述块内的任何行锤击。

30、根据一个实施方式,保护存储器块包括dram存储器,并且其中,未使用的行将使用的行分开,以防止所述块内的任何行锤击。

31、根据一个实施方式,保护存储器块包括dram存储器,该dram存储器使用4种前述方法的技术上可行的组合,以防止所述块内的任何行锤击。

32、根据一个实施方式,dram存储器包括第三部分,并且第三块实现第三算法,该第三算法用于使用第二部分以实现所需要的表来防止行锤击效应。

33、根据一个实施方式,初始表由第一算法使用,并且对应保护存储器块为根据本发明的被保护免受锤击效应的dram存储器。

34、本发明还涉及一种dram存储器控制器,控制器旨在配置针对存储器行锤击效应来配置所述dram存储器的保护,所述保护涉及控制电路和具有预定容量的保护存储器块的实现,控制器被适配为:

35、-确定由控制器控制的dram存储器的总容量;

36、-如果dram存储器的总容量超过被称为阈值大小的大小,则控制器将dram存储器的总容量划分为n个部分,n≥2,每个部分为i,其中i的范围为从1到n,n和i为整数值,其中在超过所述阈值大小的情况下,通过实现被保存在保护存储器块中的单个表的算法来进行保护是不可能的,并且控制器配置控制电路使得该控制电路能够执行n种行锤击效应保护算法,每种行锤击效应保护算法被称为算法i,其中i的范围为从1到n,每种算法i旨在借助于表i来保护部分i免受行锤击效应,每个表i被保存在部分i-1中,其中,i的范围为从2到n,同时表1被保存在保护存储器块中,如果dram存储器的总容量未超过阈值大小,则控制器配置控制电路,使得该控制电路借助于实现被存储在保护存储器块中的表的单种算法来保护所述dram存储器。

37、根据一个实施方式,针对从1变化到n的i,部分i的容量增加。

38、根据一个实施方式,保护存储器块包括不受存储器行锤击效应影响的存储器,有利地,保护存储器块包括选自以下项的存储器中的至少一者:sram存储器、mram存储器以及cnram存储器。

39、根据一个实施方式,保护存储器块被包括在控制器中。

40、根据一个实施方式,保护存储器块包括dram存储器,有利地,保护存储器块形成dram存储器的部分0。

41、根据一个实施方式,控制电路被包括在控制器中。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182339.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表