一种EEPROM单元的数据存储时间检测电路及方法与流程

- 国知局

- 2024-07-31 19:38:37

本发明涉及一种检测电路及方法,特别是一种eeprom单元的数据存储时间检测电路及方法,属于半导体集成电路。

背景技术:

1、随着集成电路技术的不断发展,eeprom获得了广泛的应用。eeprom在完成写入操作后,在eeprom单元中浮栅mos管的浮栅上带有决定eeprom单元逻辑状态的负电荷,随着时间的增加,负电荷会慢慢地流失,最后改变eeprom单元的逻辑状态,也就影响eeprom单元中的数据存储时间,所以需要检测eeprom单元中浮栅mos管的状态,来确定eeprom单元的数据是否满足长久的存储。

2、如图3所示,现有的eeprom单元采用单个浮栅mos管的结构,检测电路使用电压检测并结合读取电路,通过设置不同的检测电压,观察读取电路的输出是否改变。这种检测方法在芯片中不能详细地检测到浮栅mos管的状态,不能准确地判断eeprom单元的数据存储时间。

技术实现思路

1、本发明所要解决的技术问题是提供一种eeprom单元的数据存储时间检测电路及方法,准确地判断eeprom单元的数据存储时间。

2、为解决上述技术问题,本发明所采用的技术方案是:

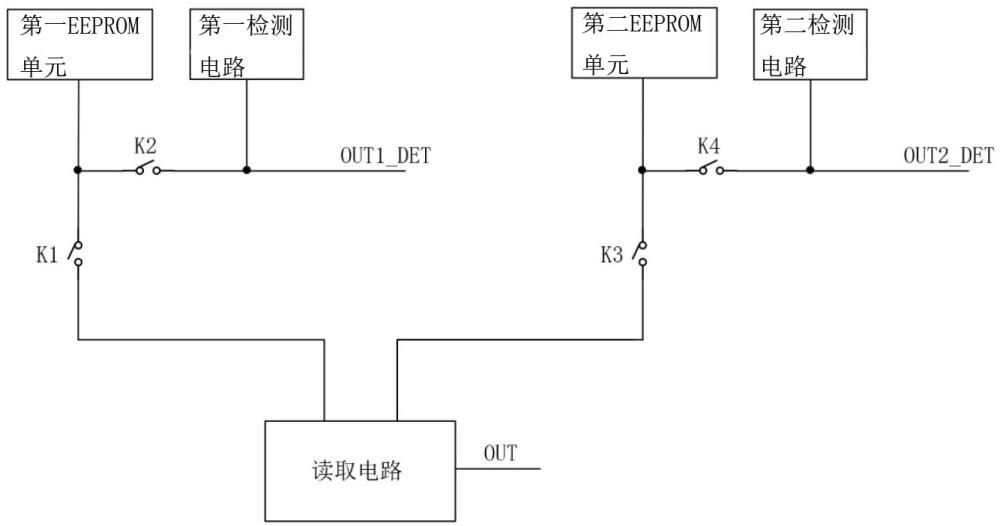

3、一种eeprom单元的数据存储时间检测电路,包含第一eeprom单元、第二eeprom单元、第一检测电路、第二检测电路、开关k1、开关k2、开关k3、开关k4和读取电路,第一eeprom单元的检测端与开关k1的一端和开关k2的一端连接,开关k1的另一端连接读取电路的第一输入端,开关k2的另一端连接第一检测电路的输出端并输出信号out1_det, 第二eeprom单元的检测端与开关k3的一端和开关k4的一端连接,开关k3的另一端连接读取电路的第二输入端,开关k4的另一端连接第二检测电路的输出端并输出信号out2_det。

4、进一步地,所述第一eeprom单元包含浮栅mos管m1,浮栅mos管m1的源极连接电源vdd,浮栅mos管m1的栅极连接浮栅fg1,浮栅mos管m1的漏极作为第一eeprom单元的检测端。

5、进一步地,所述第二eeprom单元包含浮栅mos管m2,浮栅mos管m2的源极连接电源vdd,浮栅mos管m2的栅极连接浮栅fg2,浮栅mos管m2的漏极作为第二eeprom单元的检测端。

6、进一步地,所述第一检测电路包含检测电流源idet1、检测电流源idet2、开关k5和开关k6,检测电流源idet1的一端和检测电流源idet2的一端连接电源vdd,检测电流源idet1的另一端与开关k5的一端连接,检测电流源idet2的另一端与开关k6的一端连接,开关k5的另一端与开关k6的另一端连接并作为第一检测电路的输出端。

7、进一步地,所述第二检测电路包含检测电流源idet3、检测电流源idet4、开关k7和开关k8,检测电流源idet3的一端和检测电流源idet4的一端连接电源vdd,检测电流源idet3的另一端与开关k7的一端连接,检测电流源idet4的另一端与开关k8的一端连接,开关k7的另一端与开关k8的另一端连接并作为第二检测电路的输出端。

8、进一步地,还包含外部电阻r1,外部电阻r1的一端连接信号out1_det,外部电阻r1的另一端接地。

9、进一步地,还包含外部电阻r2,外部电阻r2的一端连接信号out2_det,外部电阻r2的另一端接地。

10、一种eeprom单元的数据存储时间检测电路的检测方法,包含以下步骤:

11、第一eeprom单元和第二eeprom单元在完成写入操作后,浮栅mos管m1的栅极是高电平,浮栅mos管m2的栅极是低电平,或者浮栅mos管m1的栅极是低电平,浮栅mos管m2的栅极是高电平;

12、检测电流源idet1的电流加上检测电流源idet2的电流等于检测阈值电流,检测电流源idet1的电流值小于检测电流源idet2的电流值,检测电流源idet3的电流加上检测电流源idet4的电流等于检测阈值电流,检测电流源idet3的电流值小于检测电流源idet4的电流值。信号out1_det连接外接电阻r1,信号out2_det连接外接电阻r2;

13、进入eeprom单元检测模式,开关k1和开关k3断开,开关k2和开关k4导通;

14、如果浮栅mos管m1的栅极是高电平,浮栅mos管m2的栅极是低电平,则检测浮栅mos管m1和浮栅mos管m2的状态:开关k5和开关k6断开,开关k7和开关k8断开,分别测量信号out1_det和信号out2_det的电压,根据信号out1_det的电压和信号out2_det的电压判断浮栅mos管m1和浮栅mos管m2的电流能力和状态;

15、检测浮栅mos管m1和浮栅mos管m2的状态差异:开关k5和开关k6导通,开关k7和开关k8断开,分别测量信号out1_det和信号out2_det的电压,如果信号out2_det的电压大于信号out1_det的电压,则栅极电压是低电平的浮栅mos管m2的电流大于检测阈值电流,符合eeporm单元的数据存储时间要求;

16、如果浮栅mos管m1的栅极是低电平,浮栅mos管m2的栅极是高电平,则检测浮栅mos管m1和浮栅mos管m2的状态:开关k5和开关k6断开,开关k7和开关k8断开,分别测量信号out1_det和信号out2_det的电压,根据信号out1_det的电压和信号out2_det的电压判断浮栅mos管m1和浮栅mos管m2的电流能力和状态;

17、检测浮栅mos管m1和浮栅mos管m2的状态差异:开关k5和开关k6断开,开关k7和开关k8导通,分别测量信号out1_det和信号out2_det的电压,如果信号out1_det的电压大于信号out2_det的电压,则栅极电压是低电平的浮栅mos管m1的电流大于检测阈值电流,符合eeporm单元的数据存储时间要求。

18、本发明与现有技术相比,具有以下优点和效果:本发明的一种eeprom单元的数据存储时间检测电路及检测方法,采用双浮栅mos管结构,检测电路使用电流检测,通过外部的引脚可以测量浮栅mos管的电流值,通过电流值直接详细地反映出浮栅mos管的状态,并参考浮栅mos管的电流值和eeprom单元的数据存储时间的统计结果(如:电流值是50ua时,eeprom单元的数据存储时间是10年),可以准确地判断eeprom单元的数据存储时间,同时结合检测阈值电流,可以快速地判断eeprom单元是否符合数据存储时间的要求;本发明在检测过程中不需要使用读取电路,所以对eeprom中的每个eeprom单元都可以实现检测,检测电路更简单,成本更低。

技术特征:1.一种eeprom单元的数据存储时间检测电路,其特征在于:包含第一eeprom单元、第二eeprom单元、第一检测电路、第二检测电路、开关k1、开关k2、开关k3、开关k4和读取电路,第一eeprom单元的检测端与开关k1的一端和开关k2的一端连接,开关k1的另一端连接读取电路的第一输入端,开关k2的另一端连接第一检测电路的输出端并输出信号out1_det, 第二eeprom单元的检测端与开关k3的一端和开关k4的一端连接,开关k3的另一端连接读取电路的第二输入端,开关k4的另一端连接第二检测电路的输出端并输出信号out2_det。

2.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:所述第一eeprom单元包含浮栅mos管m1,浮栅mos管m1的源极连接电源vdd,浮栅mos管m1的栅极连接浮栅fg1,浮栅mos管m1的漏极作为第一eeprom单元的检测端。

3.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:所述第二eeprom单元包含浮栅mos管m2,浮栅mos管m2的源极连接电源vdd,浮栅mos管m2的栅极连接浮栅fg2,浮栅mos管m2的漏极作为第二eeprom单元的检测端。

4.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:所述第一检测电路包含检测电流源idet1、检测电流源idet2、开关k5和开关k6,检测电流源idet1的一端和检测电流源idet2的一端连接电源vdd,检测电流源idet1的另一端与开关k5的一端连接,检测电流源idet2的另一端与开关k6的一端连接,开关k5的另一端与开关k6的另一端连接并作为第一检测电路的输出端。

5.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:所述第二检测电路包含检测电流源idet3、检测电流源idet4、开关k7和开关k8,检测电流源idet3的一端和检测电流源idet4的一端连接电源vdd,检测电流源idet3的另一端与开关k7的一端连接,检测电流源idet4的另一端与开关k8的一端连接,开关k7的另一端与开关k8的另一端连接并作为第二检测电路的输出端。

6.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:还包含外部电阻r1,外部电阻r1的一端连接信号out1_det,外部电阻r1的另一端接地。

7.根据权利要求1所述的一种eeprom单元的数据存储时间检测电路,其特征在于:还包含外部电阻r2,外部电阻r2的一端连接信号out2_det,外部电阻r2的另一端接地。

8.一种权利要求1-7任一项所述的eeprom单元的数据存储时间检测电路的检测方法,其特征在于包含以下步骤:

技术总结本发明公开了一种EEPROM单元的数据存储时间检测电路及方法,第一EEPROM单元的检测端与开关K1的一端和开关K2的一端连接,开关K1的另一端连接读取电路的第一输入端,开关K2的另一端连接第一检测电路的输出端并输出信号OUT1_DET,第二EEPROM单元的检测端与开关K3的一端和开关K4的一端连接,开关K3的另一端连接读取电路的第二输入端,开关K4的另一端连接第二检测电路的输出端并输出信号OUT2_DET。本发明采用双浮栅MOS管结构,检测电路使用电流检测,详细地反映出浮栅MOS管的状态,可以准确地判断EEPROM单元的数据存储时间。技术研发人员:刘羽,张洪波,庄华龙受保护的技术使用者:江苏帝奥微电子股份有限公司技术研发日:技术公布日:2024/2/19本文地址:https://www.jishuxx.com/zhuanli/20240731/183369.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表