非易失性存储器及其编程方法、计算机系统与流程

- 国知局

- 2024-07-31 19:38:34

本技术涉及半导体存储器领域,具体地,涉及一种非易失性存储器的擦除技术。

背景技术:

1、半导体存储器设备一般可以被分类为易失性(volatile)存储器和非易失性(nv:non-volatile)存储器。易失性存储器(诸如dram、sram等)在缺乏所施加的电力的情况下会丢失存储的数据。相反,非易失性存储器(诸如eeprom、earom、prom、eprom、nand闪存、nor闪存等)能够在缺乏所施加的电力的情况下保持存储的数据。随着可携带电子产品(例如个人计算机、智能手机、数码相机、多媒体播放设备等等)的发展,对非易失性存储器的需求越来越大,对其性能的要求也越来越高。

2、在非易失性存储器中,有擦除、编程和读取三种基本操作。闪存(诸如,nand闪存或nor闪存)作为非易失性存储器被广泛使用。由于任何闪存器件的编程操作只能在空的或已擦除的存储单元内进行,因此在大多数情况下,在对闪存进行编程操作之前必须先执行擦除操作。通过擦除存储单元之后再将存储单元进行编程的方式,从而删除之前存储的信息再记录下新的信息。

3、以下以图1为例,示意性地描述存储单元的编程操作。

4、图1例示了现有的nor闪存中的一个存储单元100的结构示意图。nor闪存中的每个存储单元都是带有浮置栅极(也可称为浮栅)的金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)。如图1所示,存储单元100实质上为nmos晶体管,其包括衬底10(p阱衬底)、源极11、漏极12、隧道氧化层13、浮栅14、氧化层15和控制栅16,其中,隧道氧化层13、浮栅14、氧化层15和控制栅16的层叠结构构成栅极17。当存储单元100的源极11接地(施加0v电压),在漏极12上施加例如4v左右的电压,并在栅极17(具体是在控制栅16)上施加9v左右的编程电压时,漏极-源极间的电压差(4v-0v=4v)使得电子在雪崩效应下,如图1中粗箭头所示,从源极向漏极迁移而产生高能沟道热电子,与此同时,栅极17上的高电压(9v)将雪崩的电子如图1中的细箭头所示,隧穿隧道氧化层13而被吸引到浮栅14。当存储单元100的浮栅14中的电子增加到一定程度,或者换句话说当存储单元100的阈值电压(vt)高于参考电压时,认为存储单元100成功执行编程操作而记录下了新的信息。

5、另一方面,为了防止较大的漏电流,栅极电压通常会分阶段施加,例如按照5v→7v→9v的顺序依次增大栅极电压,以避免其与存储单元100的阈值电压相差太大而导致的漏电流增大。若漏电流增大,则存储单元100的阈值电压上升缓慢,导致编程效率降低,甚至可能导致编程失效,即阈值电压保持不变,不再上升。因此,存储单元100的阈值电压直接影响其编程效率。

6、图2为非易失性存储器中的经擦除和经编程的存储单元的阈值电压vt的分布图。经擦除的存储单元的阈值电压vt通常在2v-4v之间,经编程的存储单元的阈值电压vt通常在7v-9v之间。对于这些经擦除的存储单元,由于编程时的栅极初始电压vg0如上所述为5v,因此,对于选中的字线,栅极初始电压与阈值电压之差(=vg0-vt)在1v-3v的范围内,该字线上的存储单元不会漏电。未选中的字线上的存储单元也不存在漏电。因此,具有图2所示的正态分布的阈值电压vt的存储单元能够正常地进行编程。

7、然而,存储单元在擦除过程中可能因掉电等其他因素而发生过擦除的现象。过擦除是指擦除操作过后的存储单元的阈值电压小于0v或在0v附近。图3是示出在非易失性存储器中出现过擦除现象的情况下的存储单元的阈值电压分布的示意图。如图3所示,经擦除的存储单元中,有一部分存储单元的阈值电压小于或等于0v,由于非易失性存储器中同一条位线上可以连接多个存储单元,所以这些阈值电压小于或等于0v的存储单元会使得其所在的位线上有较大的漏电流,从而影响到该位线上其它存储单元的功能。

8、图4是示出在非易失性存储器中出现过擦除现象的情况下的存储单元的示意图。图4所示的物理块例如由2048条位线bl0~bl2047、2048条字线wl0~wl2047、以及并联连接到这些位线与字线的具有图1所示结构的存储单元构成,各存储单元的栅极连接至字线,漏极连接至位线。图4中,字线wl1被选中而向其连接的存储单元的栅极施加5v的电压,字线wl0、wl1023等其它字线未选中,即保持0v。同时通过位线电荷泵及编程加载器向位线bl0~bl511所连接的存储单元的漏极施加电压,即,要对wl1及bl0~bl511所连接的多个存储单元进行编程,如图中用椭圆圈出的部分所示。如果这些存储单元的阈值电压如图3所示那样出现过擦除现象,例如阈值电压vt的分布在1v左右(相比于图2所示的正常情况下大部分存储单元的阈值电压vt应该分布在3v左右),由于wl1上施加了5v电压,即编程时的初始电压vg0为5v,vg0-vt的电压差(=5v-1v=4v)过高,从而会在存储单元的漏极-源极之间产生漏电流ileak。一般来说,阈值电压vt越低的存储单元的数量越多,则漏电流越大。

9、而对于未选中的字线例如wl1023,当部分存储单元的阈值电压vt低于0v时,即使该未选中的字线上施加的是0v的电压,这些存储单元也在漏电,从而会影响到其它选中的字线上同属于一根位线上的存储单元的编程。

10、由于选中的字线上的存储单元(以及未选中的字线上的存储单元)的阈值电压vt过低,存储单元的栅极被导通,漏极-源极之间的漏电流过大时,对所选中的字线上的存储单元的编程可能会失效。

11、因此,期望提出一种技术方案,用以避免因过擦除现象导致的存储单元编程失效。

技术实现思路

1、本发明所提出的技术方案旨在解决以上所述的过擦除现象导致的存储单元编程失效的问题。

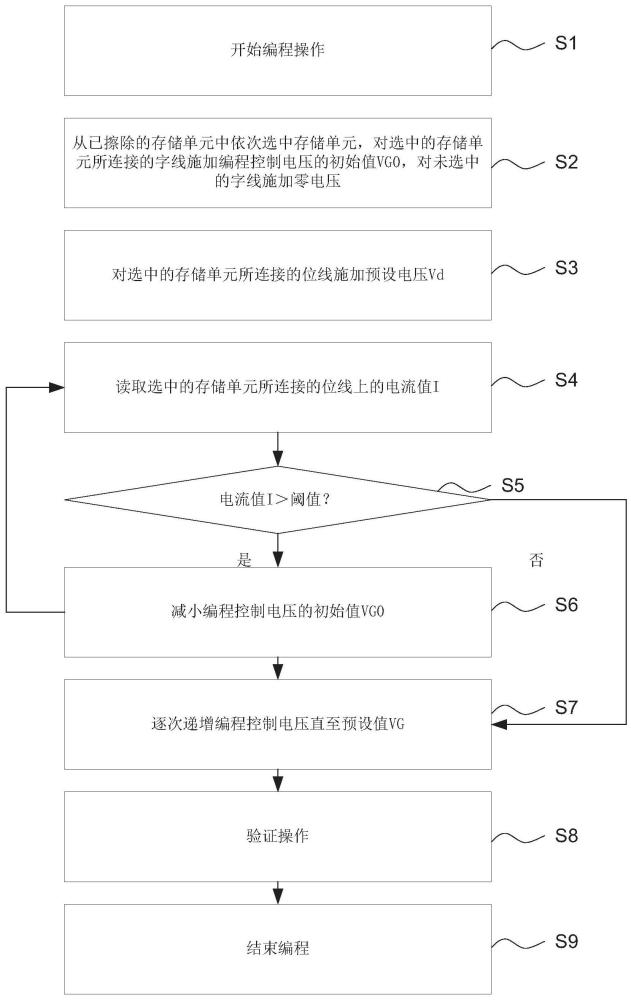

2、在本发明的一个方面,提供了一种非易失性存储器的编程方法,包括以下步骤:

3、从已擦除的存储单元中依次选中目标存储单元,对选中的所述目标存储单元所连接的字线施加第一电压作为编程控制电压的初始值,对未选中的字线施加零电压;

4、对所述目标存储单元所连接的位线施加作为固定值的第二电压;

5、读取所述目标存储单元所连接的位线上的电流值;

6、将所述电流值与规定的阈值进行比较;

7、在所述电流值大于所述阈值时,将小于所述第一电压的第三电压作为所述编程控制电压的初始值;以及

8、使所述编程控制电压自所述初始值起开始逐渐增大,在增大后的所述编程控制电压下执行编程操作,直至所述编程控制电压达到预设值。

9、在本发明的一个方面的至少一实施例中,所述目标存储单元包括:

10、与所述字线电连接的作为控制端的第一端;

11、与所述位线电连接的第二端;以及

12、接地的第三端。

13、在本发明的一个方面的至少一实施例中,施加于所述第一端的所述第一电压为5v,施加于所述第二端的所述第二电压为4v,所述预设值为9v。

14、在本发明的一个方面的至少一实施例中,所述第三电压为3v。

15、在本发明的一个方面的至少一实施例中,在选中所述目标存储单元之前,还包括对所述目标存储单元进行擦除及校验的步骤,以获取所述目标存储单元的阈值电压分布。

16、在本发明的一个方面的至少一实施例中,根据所述目标存储单元的阈值电压分布,设定所述第一电压及所述第三电压。

17、在本发明的一个方面的至少一实施例中,所述编程控制电压自所述初始值起以阶跃式递增的方式增大至所述预设值。

18、在本发明的一个方面的至少一实施例中,所述编程控制电压以3v→6v→9v的顺序逐渐增大。

19、在本发明的一个方面的至少一实施例中,在所述编程控制电压达到所述预设值之后,还包括对所述目标存储单元进行编程校验的步骤。

20、在本发明的另一方面,提供了一种非易失性存储器,存储有计算机指令,当所述计算机指令被处理部执行时,所述处理部对所述非易失性存储器执行如前述段落中的任一段落所述的编程方法。

21、在本发明的又一方面,提供了一种计算机系统,包括:存储有计算机指令的计算机存储介质;非易失性存储器;以及处理部,所述处理部在执行所述计算机指令时,对所述非易失性存储器执行如前述段落中的任一段落所述的编程方法。

22、本发明所提出的技术方案可以具有以下一项或多项优点:

23、(1)对于经过擦除后有可能存在过擦除现象的存储单元,为了防止因该存储单元的阈值电压过低而导致该存储单元所连接的位线上存在漏电流,通过降低编程操作时施加在该存储单元所连接的字线上的编程控制电压的初始值,以减小编程控制电压的初始值与该存储单元的阈值电压之差,从而能够减小甚至消除该存储单元所连接的位线上的漏电流,进而能够防止编程效率降低及编程失效。

24、(2)由于减小了因存储单元的阈值电压过低而导致该存储单元所连接的位线上存在的漏电流的影响,因此,能够确保经擦除的存储单元与经编程的存储单元之间的裕度,同时在后续的读取操作中有助于提高读取速度,提高nor flash等存储器本身的可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183361.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表