通过分组和筛选存储器单元来减少非易失性存储器中的随机电报噪声的方法与流程

- 国知局

- 2024-07-31 19:34:45

本发明涉及非易失性存储器设备,并且更具体地涉及提高读取操作期间存储器单元电流的稳定性。

背景技术:

1、非易失性存储器设备在本领域中是公知的。参见例如美国专利7,868,375,其公开了四栅存储器单元配置,并且以引用方式并入本文用于所有目的。具体地,本技术的图1示出了具有在硅半导体衬底12中形成的间隔开的源极区14和漏极区16的分裂栅存储器单元10。源极区14可以被称为源极线sl(因为其通常连接到同一行或列中其他存储器单元的其他源极区),并且漏极区16通常通过位线触点28连接到位线。衬底的沟道区18被限定在源极区14/漏极区16之间。浮栅20竖直地设置在沟道区18的第一部分上方并且与该第一部分绝缘(并且控制其电导率)(并且部分地竖直地位于源极区14上方并且与其绝缘)。控制栅22竖直地设置在浮栅20上方并且与其绝缘。选择栅24竖直地设置在沟道区18的第二部分上方并且与其绝缘(并控制其电导率)。擦除栅26竖直地设置在源极区14上方并且与其绝缘,并且与浮栅20侧向相邻。多个此类存储器单元可以按行和列排列以形成存储器单元阵列。

2、将各种组合的电压施加到控制栅22、选择栅24、擦除栅26和/或源极区14/漏极区16,以对分裂栅存储器单元10进行编程(即,将电子注入到浮栅上)、擦除分裂栅存储器单元10(即,从浮栅移除电子),以及读取分裂栅存储器单元10(即,测量或检测沟道区18的电导率以确定浮栅20的编程状态)。

3、分裂栅存储器单元10可以数字方式操作,其中分裂栅存储器单元10被设置为仅两种可能的状态中的一种:编程状态和擦除状态。通过在擦除栅26上施加高正电压并且可选地在控制栅22上施加负电压来擦除分裂栅存储器单元10,以引起电子从浮栅20到擦除栅26的隧穿(使浮栅20处于带更多正电荷的状态—擦除状态)。可以通过在控制栅22、擦除栅26、选择栅24和源极区14上施加正电压以及在漏极区16上施加电流来对分裂栅存储器单元10进行编程。然后,电子将沿着沟道区18从漏极区16流向源极区14,其中电子变得加速并且变热,由此它们中的一部分通过热电子注入被注入到浮栅20上(使浮栅20处于带更多负电荷的状态—编程状态)。可以通过在选择栅24(导通选择栅24下方的沟道区18的部分)和漏极区16(并且可选地在擦除栅26和/或控制栅22上)上施加正电压并且感测流过沟道区18的电流来读取分裂栅存储器单元10。如果浮栅20带正电荷(即,分裂栅存储器单元10被擦除),则分裂栅存储器单元10将被导通,并且电流将从漏极区16流动到源极区14(即,分裂栅存储器单元10基于所感测的电流流动而被感测为处于其擦除“1”状态)。如果浮栅20带负电荷(即,分裂栅存储器单元10被编程),则浮栅20下方的沟道区18的部分被关断,从而阻止可测量的电流流动(即,分裂栅存储器单元10基于无电流流动或最小的电流流动而被感测为处于其编程“0”状态)。

4、表1提供了用于分裂栅存储器单元的典型数字操作的擦除、编程和读取电压的非限制性示例,其中vcc是电源电压或另一正电压(诸如2.5v)。

5、表1

6、 wl(sg) bl(dram) 源极 eg cg 擦除 0v 0v 0v 11.5v 0v 编程 1v iμa 4.5 4.5v 10.5v 读取 vcc 0.6v 0v 0v vcc

7、分裂栅存储器单元10可另选地以模拟方式操作,其中分裂栅存储器单元10的存储器状态(即,浮栅20上的电荷量,诸如电子数)可被调谐到从完全擦除状态(浮栅20上电子数最少)到完全编程状态(浮栅20上的电子数最多)的任何地方,或通过改变一个或多个编程电压而只是调谐到这个范围的一部分,例如,可使用各种控制栅22(cg)编程电压用于模拟编程。这意味着分裂栅存储器单元10存储是模拟的,这允许对分裂栅存储器单元10的阵列中每个分裂栅存储器单元10进行非常精确和单独的调谐。另选地,分裂栅存储器单元10可以作为mlc(多级单元)来操作,其中其被配置为被编程到许多离散值(诸如16或64个不同值)中的一个值。在模拟或mlc编程的情况下,编程电压在有限的时间内或作为一系列脉冲施加,直到实现期望的编程状态。在多个编程脉冲的情况下,可以使用编程脉冲之间的中间读取操作来确定期望的编程状态是否已经实现(在这种情况下编程停止)或尚未实现(在这种情况下编程继续)。

8、以模拟方式或作为mlc操作的分裂栅存储器单元10可能对噪声和读取电流不稳定性更敏感,这会对分裂栅存储器设备10的准确度产生不利影响。模拟非易失性存储器设备中的读取电流不稳定性的一个来源是由位于栅极氧化物与存储器单元沟道区之间的界面和接近界面处的氧化物陷阱进行的电子捕获和发射。该栅极氧化物是隔离浮栅20和衬底12的沟道区18的绝缘层。当电子在界面阱上被捕获时,其减小了在读取操作期间的沟道电导率,并因此增大分裂栅存储器单元10的阈值电压vt(即,导通分裂栅存储器单元10的沟道区18以产生预定目标电流(例如1μa)所需的控制栅22上的最小电压)。当控制栅电压处于或高于阈值电压vt时,在源极区14和漏极区16之间形成导电路径,并且至少该预定目标电流的电流流动。当控制栅电压低于阈值电压vt时,不形成导电路径,并且源极区14和漏极区16之间的任何电流都被视为亚阈值或漏电流。在界面阱上被捕获的电子可以从该界面阱发射,这降低存储器单元的阈值电压vt,并因此增大在读取操作期间的沟道电导率。由界面阱进行的电子捕获和发射的这些单电子事件表现为读取电流噪声,并且被称为随机电报噪声(rtn)。通常,由单个界面阱产生的rtn通过两种状态来表征:电子从界面阱发射时的较低vt状态(和较高读取电流状态)和电子被界面阱捕获时的较高vt状态(和较低读取电流状态)。如上所述,分裂栅存储器单元10在读取期间的不稳定性可以通过阈值电压vt(即,对应于预定目标电流的控制栅电压)或通过在给定读取电压条件下的存储器单元电流来表征。本文示例关于存储器单元读取不稳定性被具体描述为阈值电压vt,然而,特别地设想在给定读取电压下使用存储器单元电流。

9、在存储器单元阵列内存在小但不可忽略百分比的存储器单元(诸如分裂栅存储器单元10)对于需要极高读取准确度的那些应用展现出不可容忍量的rtn。容易受rtn影响的存储器单元增大存储在存储器单元阵列中的一些模拟数据将至少在某种程度上被破坏的风险,因为此类存储器单元在编程之后从界面阱的电子发射将不良地减小存储器单元的阈值电压vt(并且因此不良地增大读取操作期间的沟道电导率),因此提供对所期望原始存储器单元编程状态的不准确读取。类似地,此类存储器单元在编程之后的电子捕获将不良地增大存储器单元的阈值电压vt(并且因此不良地降低读取操作期间的沟道电导率),因此提供对所期望原始存储器单元编程状态的不准确读取。因此,需要应对模拟和mlc非易失性存储器设备中的rtn以补偿编程后的rtn。

技术实现思路

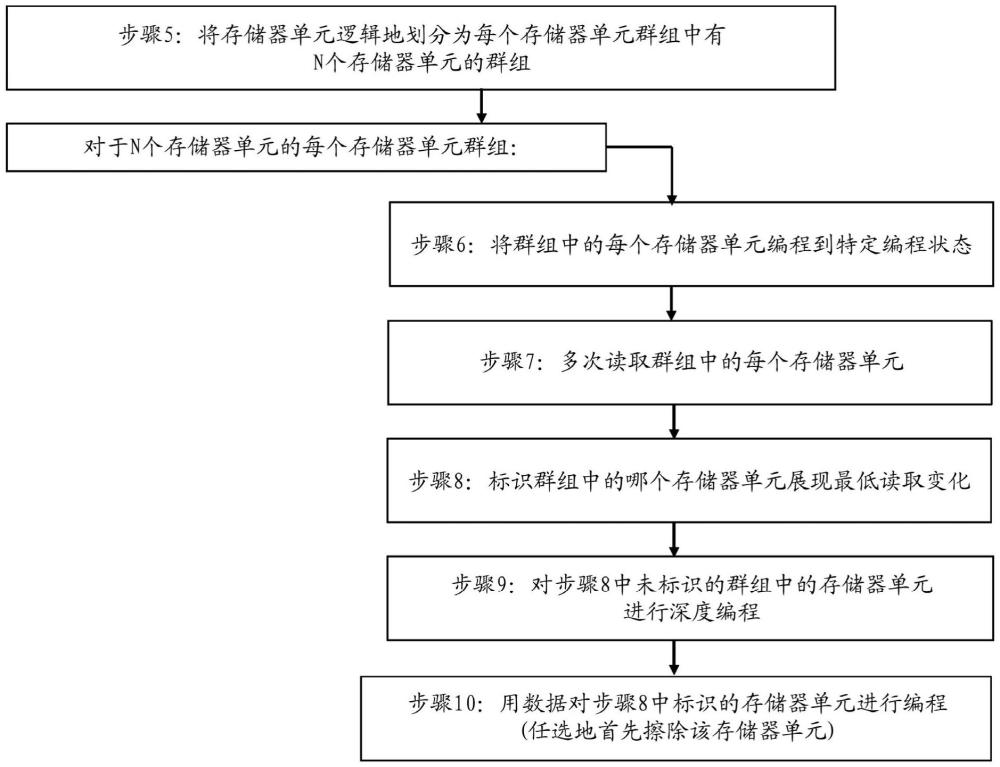

1、前述问题和需求通过一种存储器设备来解决,所述存储器设备包括多个存储器单元群组,其中所述存储器单元群组中的每一者包括n个非易失性存储器单元,其中n为大于或等于2的整数;以及控制电路。所述控制电路被配置为:对于所述存储器单元群组中的每一者,将所述存储器单元群组中的所述非易失性存储器单元中的每一者编程到特定编程状态;对所述存储器单元群组中的所述非易失性存储器单元中的每一者执行多个读取操作;标识所述存储器单元群组中的所述非易失性存储器单元中在所述多个读取操作期间展现最低读取变化的一者;对所述存储器单元群组中除所标识的非易失性存储器单元之外的所有所述非易失性存储器单元进行深度编程;以及用用户数据对所述存储器单元群组中的所标识的非易失性存储器单元进行编程。

2、一种对具有多个存储器单元群组的存储器设备进行编程的方法,其中所述存储器单元群组中的每一者包括n个非易失性存储器单元,其中n为大于或等于2的整数,其中对于每个存储器单元群组,所述方法包括:将所述存储器单元群组中的所述非易失性存储器单元中的每一者编程到特定编程状态;对所述存储器单元群组中的所述非易失性存储器单元中的每一者执行多个读取操作;标识所述存储器单元群组中的所述非易失性存储器单元中在所述多个读取操作期间展现最低读取变化的一者;对所述存储器单元群组中除所标识的非易失性存储器单元之外的所有所述非易失性存储器单元进行深度编程;以及用用户数据对所述存储器单元群组中的所标识的非易失性存储器单元进行编程。

3、通过查看说明书、权利要求书和附图,其他目的和特征将变得显而易见。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183126.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表