DRAM系统、校准训练方法、片上系统及电子设备与流程

- 国知局

- 2024-07-31 19:34:41

本公开涉及存储器,尤其涉及一种dram系统、校准训练方法、片上系统、电子组件及电子设备。

背景技术:

1、对于采用dram(dynamic random access memory,动态随机存储器)系统作为内存的片上系统(system on chip,soc)芯片来说,稳定的dram系统能减少读写传输发生错误的概率,为soc持续提供高带宽访问,因此,dram系统能否稳定工作在一个目标频点至关重要。

2、为保证dram系统稳定工作,目前一般的设计方法是要求dram系统根据pvt(器件工艺process,工作电压voltage,工作温度temperature)的变化,周期性地校准其内部的参数变量来维持dram系统的稳定性。如图1所示,也就是预先设定一个校准间隔t_interval,然后每计时到一个t_interval就触发一次dram系统的校准训练。

3、如此,周期性地进行校准训练虽然有助于dram系统的稳定工作,但是在校准训练期间不可避免地会对dram的访问带宽造成损失,增加访存时延,因此,传统的校准训练方式会周期性地影响dram系统的性能。

技术实现思路

1、本公开的目的是提供一种dram系统、校准训练方法、片上系统、电子组件及电子设备,有利于在保证dram系统稳定性的同时,提升dram系统的性能。

2、根据本公开的一个方面,提供一种dram系统,包括控制器以及端口物理层芯片phy,所述控制器包括用于记录第二次数的寄存器;所述第二次数表示所述dram系统所累积发生的错误的次数;所述控制模块,被配置为:每隔预设时间间隔统计dram系统在本时间间隔内发生错误的第一次数;根据所述第一次数与所述第二次数的和值和预先配置的错误阈值,确定在本时间间隔是否对所述phy发出校准训练指令;所述phy,被配置为:响应所述校准训练指令并执行校准训练。

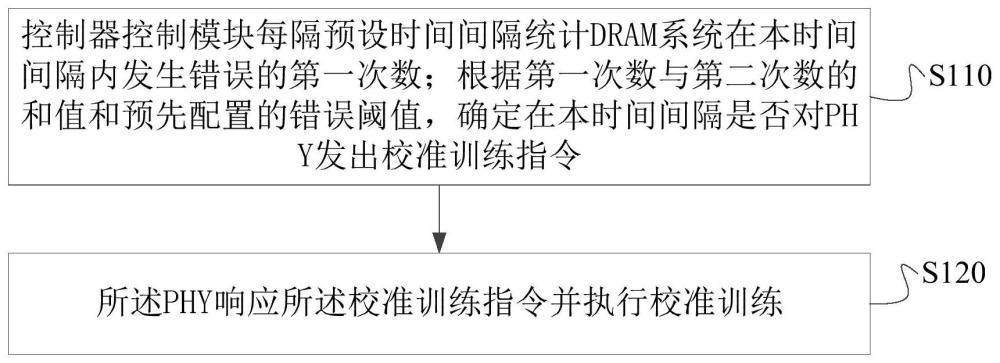

3、本公开一种可行的实现方式中,所述错误阈值包括第一阈值,所述在确定在本时间间隔是否对所述phy发出校准训练指令的情况下,所述控制模块具体被配置为:在所述和值小于所述第一阈值的情况下,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中;在所述和值大于或者等于所述第一阈值的情况下,在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器。

4、本公开一种可行的实现方式中,所述错误阈值包括第一阈值、第二阈值,所述第一阈值小于所述第二阈值,所述控制器还包括用于缓存上游设备的读写请求命令的命令缓冲器command buffer;所述在确定在本时间间隔是否对所述phy发出校准训练指令的情况下,所述控制模块具体被配置为:在所述和值小于所述第一阈值的情况下,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中;在所述和值大于或者等于所述第一阈值的情况下,根据所述和值与第二阈值之间的大小关系以及所述command buffer的空闲情况,确定在本时间间隔是否对所述phy发出校准训练指令。

5、本公开一种可行的实现方式中,所述在根据所述和值与第二阈值之间的大小关系以及所述command buffer的空闲情况,确定在本时间间隔是否对所述phy发出校准训练指令的情况下,所述控制模块具体被配置为:若所述和值小于所述第二阈值且所述commandbuffer为空,所述控制模块在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器;若所述和值小于所述第二阈值且所述command buffer不为空,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中。

6、本公开一种可行的实现方式中,所述校准训练指令包括慢校准训练指令;在所述控制模块在本时间间隔对所述phy发出校准训练指令的情况下,所述控制模块具体被配置为:向所述phy发出所述慢校准训练指令;所述phy,被配置为:响应所述慢校准训练指令,执行完整的校准训练过程。

7、本公开一种可行的实现方式中,所述控制模块还被配置为:若所述和值大于或等于所述第二阈值,所述控制模块在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器。

8、本公开一种可行的实现方式中,所述校准训练指令包括慢校准训练指令以及快校准训练指令;在所述控制模块在本时间间隔对所述phy发出校准训练指令的情况下,所述控制模块,具体被配置为:若所述和值大于或等于所述第二阈值,且所述command buffer为空,所述控制模块向所述phy发出慢校准训练指令;若所述和值大于或等于所述第二阈值,且所述command buffer不为空,所述控制模块向所述phy发出快校准训练指令,且在所述phy响应完所述快校准训练指令,且执行完所述command buffer内的读写请求命令后,再向所述phy发出慢校准训练指令;所述phy,具体被配置为:响应所述慢校准训练指令的情况下,执行完整的校准训练过程,响应所述快校准训练指令的情况下,执行所述完整的校准训练过程中的部分过程。

9、本公开一种可行的实现方式中,所述部分过程为对读命令的校准训练以及对写命令的校准训练。

10、本公开一种可行的实现方式中,所述控制器包括循环冗余校核crc模块以及错误检查和纠正ecc模块,在所述统计dram系统在本时间间隔内发生错误的第一次数的情况下,所述控制模块具体被配置为:统计所述crc模块和/或所述ecc模块在本时间间隔内检测出的总错误次数,所述总错误次数为所述第一次数。

11、根据本公开的另一方面,提供一种校准训练方法,应用于dram系统,所述dram系统包括控制器以及端口物理层芯片phy,所述控制器包括控制模块以及用于记录第二次数的寄存器;所述第二次数表示所述dram系统所累积发生的错误的次数;所述方法包括:所述控制模块每隔预设时间间隔统计dram系统在本时间间隔内发生错误的第一次数;根据所述第一次数与所述第二次数的和值和预先配置的错误阈值,确定在本时间间隔是否对所述phy发出校准训练指令;所述phy响应所述校准训练指令并执行校准训练。

12、本公开一种可行的实现方式中,所述错误阈值包括第一阈值,所述确定在本时间间隔是否对所述phy发出校准训练指令,包括:在所述和值小于所述第一阈值的情况下,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中;在所述和值大于或者等于所述第一阈值的情况下,在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器。

13、本公开一种可行的实现方式中,所述错误阈值包括第一阈值、第二阈值,所述第一阈值小于所述第二阈值,所述控制器还包括用于缓存上游设备的读写请求命令的命令缓冲器command buffer;所述确定在本时间间隔是否对所述phy发出校准训练指令,包括:在所述和值小于所述第一阈值的情况下,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中;在所述和值大于或者等于所述第一阈值的情况下,根据所述和值与第二阈值之间的大小关系以及所述command buffer的空闲情况,确定在本时间间隔是否对所述phy发出校准训练指令。

14、本公开一种可行的实现方式中,所述根据所述和值与第二阈值之间的大小关系以及所述command buffer的空闲情况,确定在本时间间隔是否对所述phy发出校准训练指令,包括:若所述和值小于所述第二阈值且所述command buffer为空,所述控制模块在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器;

15、若所述和值小于所述第二阈值且所述command buffer不为空,确定在本时间间隔不对所述phy执行校准训练,并将所述第一次数累加到用于记录所述第二次数的寄存器中。

16、本公开一种可行的实现方式中,所述校准训练指令包括慢校准训练指令;所述控制模块在本时间间隔对所述phy发出校准训练指令,包括:向所述phy发出所述慢校准训练指令;

17、相应的,所述phy响应所述校准训练指令并执行校准训练,包括:响应所述慢校准训练指令,执行完整的校准训练过程。

18、本公开一种可行的实现方式中,所述方法还包括:若所述和值大于或等于所述第二阈值,所述控制模块在本时间间隔对所述phy发出校准训练指令,并清空用于记录所述第二次数的寄存器。

19、本公开一种可行的实现方式中,所述校准训练指令包括慢校准训练指令以及快校准训练指令;所述控制模块在本时间间隔对所述phy发出校准训练指令,包括:若所述和值大于或等于所述第二阈值,且所述command buffer为空,所述控制模块向所述phy发出慢校准训练指令;若所述和值大于或等于所述第二阈值,且所述command buffer不为空,所述控制模块向所述phy发出快校准训练指令,且在所述phy响应完所述快校准训练指令,且执行完所述command buffer内的读写请求命令后,再向所述phy发出慢校准训练指令;

20、相应的,所述phy响应所述校准训练指令并执行校准训练,包括:响应所述慢校准训练指令的情况下,执行完整的校准训练过程;和/或响应所述快校准训练指令的情况下,执行所述完整的校准训练过程中的部分过程。

21、本公开一种可行的实现方式中,所述部分过程为对读命令的校准训练以及对写命令的校准训练。

22、本公开一种可行的实现方式中,所述控制器包括循环冗余校核crc模块以及错误检查和纠正ecc模块,所述统计dram系统在本时间间隔内发生错误的第一次数,包括:统计所述crc模块和/或所述ecc模块在本时间间隔内检测出的总错误次数,所述总错误次数为所述第一次数。

23、根据本公开的另一方面,还提供一种片上系统(system on chip,soc),该片上系统包括上述dram系统。在一些使用场景下,该soc的产品形式体现为gpu(graphicsprocessing unit,图形处理器)soc;在另一些使用场景下,该soc的产品形式体现为cpu(central processing unit,中央处理器)soc。

24、根据本公开的另一方面,还提供一种电子组件,该电子组件包括上述任一实施例中所述的片上系统soc。在一些使用场景下,该电子组件的产品形式体现为显卡;在另一些使用场景下,该电子组件的产品形式体现为cpu主板。

25、根据本公开的另一方面,还提供一种电子设备,包括上述的电子组件。在一些使用场景下,该电子设备的产品形式是便携式电子设备,例如智能手机、平板电脑、vr设备等;在一些使用场景下,该电子设备的产品形式是个人电脑、游戏主机等。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183118.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。