DRAM存储单元电路及DRAM存储器的制作方法

- 国知局

- 2024-07-31 19:33:18

本技术涉及电子,尤其涉及一种dram存储单元电路及dram存储器。

背景技术:

1、传统的dram(dynamic random access memory动态随机存储器)单元由一个晶体管和一个电容器组成,但随着集成度的增加,电容器基于无源器件的物理特性,随着其结构持续缩小,其电荷存储量持续降低,漏电过快,dram即将达到刷新频率的极限。

2、现有的存储单元包括基于双晶体管或者基于三晶体管加电容器的结构,其中双晶体管的存储单元在读取数据的阶段无法提供良好的电荷隔离效果,而三晶体管加电容器的存储单元存在集成度密度不够的问题,所以,亟待需要一种存储单元可以兼容解决上述问题。

技术实现思路

1、为了至少解决上述问题,本实用新型实施例的第一方面提供了一种dram存储单元电路,该dram存储单元电路包括:

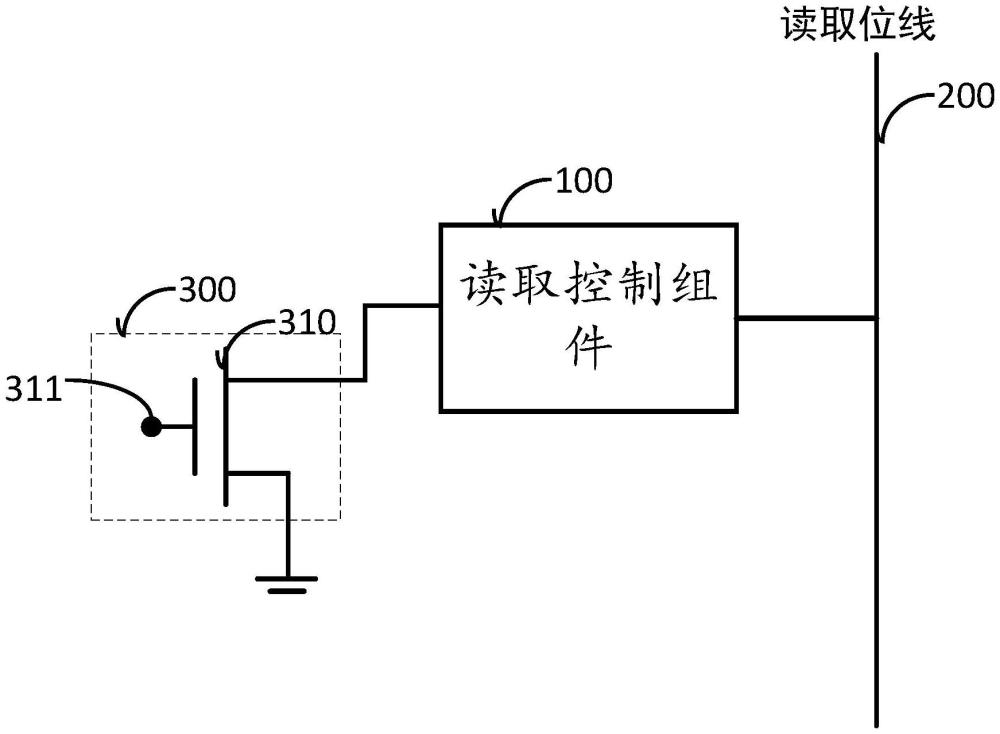

2、读取控制组件,上述读取控制组件与读取位线电连接,上述读取位线与写入位线不共用;

3、存储组件,上述存储组件包括第一晶体管,上述第一晶体管的栅极用于存储数据;

4、上述第一晶体管的漏极与上述读取控制组件电连接,上述第一晶体管的源极接地。

5、可选的,上述dram存储单元电路还包括:写入控制组件,上述写入控制组件与上述第一晶体管的栅极电连接,上述写入控制组件与上述写入位线电连接,上述写入控制组件与写入字线电连接,上述读取控制组件与读取字线电连接。

6、可选的,上述读取控制组件包括第二晶体管,上述第二晶体管的漏极与上述读取位线电连接,上述第二晶体管的源极与上述第一晶体管的漏极电连接,上述第二晶体管的栅极与读取字线电连接。

7、可选的,上述写入控制组件包括第三晶体管,上述第三晶体管的漏极与上述写入位线电连接,上述第三晶体管的源极与上述第一晶体管的栅极电连接,上述第三晶体管的栅极与写入字线电连接。

8、可选的,上述读取控制组件包括第二晶体管,上述第二晶体管的漏极与上述读取位线电连接,上述第二晶体管的源极与上述第一晶体管的漏极电连接,上述第二晶体管的栅极与读取字线电连接。

9、上述写入控制组件包括第三晶体管,上述第三晶体管的漏极与上述写入位线电连接,上述第三晶体管的源极与上述第一晶体管的栅极电连接,上述第三晶体管的栅极与写入字线电连接。

10、可选的,上述dram存储单元电路在读取数据阶段上述写入字线处于低电平状态,上述读取字线处于高电平状态,与上述读取字线电连接的上述读取控制组件处于导通状态,与上述写入字线电连接的写入控制组件处于截止状态,上述存储组件处于读取状态。

11、可选的,上述dram存储单元电路在写入数据阶段上述写入字线处于高电平状态,上述读取字线处于低电平状态,与上述写入字线电连接的上述写入控制组件处于导通状态,与上述读取字线电连接的上述读取控制组件处于截止状态,上述存储组件处于写入状态。

12、可选的,上述dram存储单元电路在准备阶段,上述写入字线处于低电平状态,上述读取字线处于低电平状态。

13、可选的,上述晶体管包括铟镓锌氧化物晶体管。

14、本实用新型实施例的第二方面提供了一种dram存储器,包括:

15、如第一方面上述的dram存储单元电路。

16、本申请实施例提供的dram存储单元电路及dram存储器,该dram存储单元电路包括:读取控制组件,上述读取控制组件与读取位线电连接,上述读取位线与写入位线不共用;存储组件,上述存储组件包括第一晶体管,上述第一晶体管的栅极用于存储数据;上述第一晶体管的漏极与上述读取控制组件电连接,上述第一晶体管的源极接地。通过设置读取控制组件和存储组件,存储组件包括第一晶体管,该第一晶体管的栅极用于存储数据,该存储数据由写入位线输入,通过不利用独立电容存储数据的设计方法,相比传统的存储电路单元具有更高的集成密度,极大节省传统技术中独立电容所带来的面积消耗,上述第一晶体管的漏极与上述读取控制组件电连接,在上述dram存储单元读取数据的情况下,通过上述读取控制组件的设置隔离了因上述读取存入位线电平变化产生的电势差,避免了使上述第一晶体管的栅极产生电势差,阻止了栅极内存储数据的因电势差产生的流失,相比于传统的存储单元设计,提供了更好的电荷隔离效果。

技术特征:1.一种dram存储单元电路,其特征在于,包括:

2.根据权利要求1所述的dram存储单元电路,其特征在于,还包括:

3.根据权利要求2所述的dram存储单元电路,其特征在于,

4.根据权利要求2所述的dram存储单元电路,其特征在于,

5.根据权利要求2所述的dram存储单元电路,其特征在于,

6.根据权利要求2至5中任一项所述的dram存储单元电路,其特征在于,

7.根据权利要求2至5中任一项所述的dram存储单元电路,其特征在于,

8.根据权利要求2至5中任一项所述的dram存储单元电路,其特征在于,

9.根据权利要求1至5中任一项所述的dram存储单元电路,其特征在于,

10.一种dram存储器,其特征在于,包括:

技术总结本申请实施例提供了一种DRAM存储单元电路及DRAM存储器,通过设置读取控制组件和存储组件,存储组件包括第一晶体管,该第一晶体管的栅极用于存储数据,该存储数据由写入位线输入,通过不利用独立电容存储数据的设计方法,相比传统的存储电路单元具有更高的集成密度,极大节省传统技术中独立电容所带来的面积消耗,上述第一晶体管的漏极与上述读取控制组件电连接,在上述DRAM存储单元读取数据的情况下,通过上述读取控制组件的设置隔离了因上述读取存入位线电平变化产生的电势差,避免了使上述第一晶体管的栅极产生电势差,阻止了栅极内存储数据的因电势差产生的流失,相比于传统的存储单元设计,提供了更好的电荷隔离效果。技术研发人员:汪令飞,卢年端,王桂磊,赵超,李泠受保护的技术使用者:北京超弦存储器研究院技术研发日:20230224技术公布日:2024/1/22本文地址:https://www.jishuxx.com/zhuanli/20240731/183047.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表