带环绕式栅极晶体管一次编程存储单元的制作方法

- 国知局

- 2024-07-31 19:34:23

本发明涉及一种非易失性存储单元,且特别是涉及一种用于物理不可复制技术的带环绕式栅极晶体管(gate-all-around transistor,简称gaa晶体管)一次编程存储单元。

背景技术:

1、众所周知,一次编程的存储器(one time programming memory,简称otp存储器)为一种非易失性存储器(non-volatile memory)。otp存储器中包括多个一次编程存储单元(简称otp存储单元)。otp存储单元仅能进行一次编程动作,一旦otp存储单元进行编程动作之后,otp存储单元的存储数据将无法修改。

2、物理不可复制技术(physically unclonable function,简称puf技术)是一种创新的方式用来保护半导体芯片内部的数据,防止半导体芯片的内部数据被窃取。根据puf技术,半导体芯片能够提供一随机码(random code)。此随机码可作为半导体芯片(semiconductor chip)上特有的身分码(id code),用来保护内部的数据。

3、一般来说,puf技术是利用半导体芯片的制造变异(manufacturing variation)来获得独特的随机码。此制造变异包括半导体的制作工艺变异(process variation)。亦即,就算有精确的制作工艺步骤可以制作出半导体芯片,但是其随机码几乎不可能被复制(duplicate)。因此,具有puf技术的半导体芯片通常被运用于高安全防护的应用(applications with high security requirements)。

4、举例来说,美国专利号码us 9,613,714揭露一种用于物理不可复制技术的一次编程存储单元与存储单元阵列及其相关随机码产生方法。

技术实现思路

1、本发明有关于一种运用于物理不可复制技术(puf技术)的反熔丝型一次编程存储单元,包括:一第一纳米线;一第二纳米线;一第一栅极结构,包括一第一间隙壁、一第二间隙壁、一第一栅极介电层、一第二栅极介电层与一第一栅极层;其中,该第一纳米线的一中间区域被该第一栅极介电层环绕,该第二纳米线的一中间区域被该第二栅极介电层环绕,该第一栅极介电层与该第二栅极介电层被该第一栅极层环绕,该第一栅极层连接至一反熔丝控制线,该第一纳米线的一第一侧区域被该第一间隙壁环绕,该第一纳米线的一第二侧区域被该第二间隙壁环绕,该第二纳米线的一第一侧区域被该第一间隙壁环绕,该第二纳米线的一第二侧区域被该第二间隙壁环绕;一第一漏/源结构,电性接触至该第一纳米线的一第一端以及电性接触至该第二纳米线的一第一端;一第二漏/源结构,电性接触至该第一纳米线的一第二端,且未电性接触至该第二纳米线的一第二端;一第一晶体管,该第一晶体管具有一第一漏/源端,一栅极端与一第二漏/源端,该第一晶体管的该第二漏/源端连接至该第一漏/源结构;以及,一第二晶体管,该第二晶体管具有一第一漏/源端,一栅极端与一第二漏/源端,该第二晶体管的该第一漏/源端连接至该第二漏/源结构。

2、本发明有关于一种运用于物理不可复制技术(puf技术)的反熔丝型一次编程存储单元,包括:一第一纳米线;一第一栅极结构,包括一第一间隙壁、一第二间隙壁、一第一栅极介电层与一第一栅极层;其中,该第一纳米线的一中间区域被该第一栅极介电层环绕,该第一栅极介电层被该第一栅极层环绕,该第一栅极层连接至一反熔丝控制线,该第一纳米线的一第一侧区域被该第一间隙壁环绕,该第一纳米线的一第二侧区域被该第二间隙壁环绕;一第一漏/源结构,电性接触至该第一纳米线的一第一端;一第二纳米线;一第二栅极结构,包括一第三间隙壁、一第四间隙壁、一第二栅极介电层与一第二栅极层;其中,该第二纳米线的一中间区域被该第二栅极介电层环绕,该第二栅极介电层被该第二栅极层环绕,该第二栅极层连接至该反熔丝控制线,该第二纳米线的一第一侧区域被该第三间隙壁环绕,该第二纳米线的一第二侧区域被该第四间隙壁环绕;一第二漏/源结构,电性接触至该第一纳米线的一第二端以及该第二纳米线的一第一端;一第三漏/源结构,电性接触至该第二纳米线的一第二端;一第一晶体管,该第一晶体管具有一第一漏/源端,一栅极端与一第二漏/源端,该第一晶体管的该第二漏/源端连接至该第一漏/源结构;以及,一第二晶体管,该第二晶体管具有一第一漏/源端,一栅极端与一第二漏/源端,该第二晶体管的该第一漏/源端连接至该第三漏/源结构。

3、本发明有关于一种运用于物理不可复制技术(puf技术)的反熔丝型一次编程存储单元,包括:一第一纳米线;一第二纳米线;一第一栅极结构,包括一第一间隙壁、一第二间隙壁、一第一栅极介电层、一第二栅极介电层与一第一栅极层;其中,该第一纳米线的一中间区域被该第一栅极介电层环绕,该第二纳米线的一中间区域被该第二栅极介电层环绕,该第一栅极介电层与该第二栅极介电层被该第一栅极层环绕,该第一栅极层连接至一反熔丝控制线,该第一纳米线的一第一侧区域被该第一间隙壁环绕,该第一纳米线的一第二侧区域被该第二间隙壁环绕,该第二纳米线的一第一侧区域被该第一间隙壁环绕,该第二纳米线的一第二侧区域被该第二间隙壁环绕;一第一漏/源结构,电性接触至该第一纳米线的一第一端,未电性接触至该第二纳米线的一第一端;一第三纳米线,该第三纳米线的一第一端电性接触至该第一纳米线的一第二端;一第四纳米线,该第四纳米线的一第一端电性接触至该第二纳米线的一第二端;一第二栅极结构,包括一第三间隙壁、一第四间隙壁、一第三栅极介电层、一第四栅极介电层与一第二栅极层;其中,该第三纳米线的一中间区域被该第三栅极介电层环绕,该第四纳米线的一中间区域被该第四栅极介电层环绕,该第三栅极介电层与该第四栅极介电层被该第二栅极层环绕,该第三纳米线的一第一侧区域被该第三间隙壁环绕,该第三纳米线的一第二侧区域被该第四间隙壁环绕,该第四纳米线的一第一侧区域被该第三间隙壁环绕,该第四纳米线的一第二侧区域被该第四间隙壁环绕;一第二漏/源结构,电性接触至该第三纳米线的一第二端以及电性接触至该第四纳米线的一第二端,其中该第二漏/源结构、该第三纳米线、该第四纳米线与该第二栅极结构形成一第一晶体管;以及一第二晶体管,该第二晶体管具有一第一漏/源端,一栅极端与一第二漏/源端,该第二晶体管的该第一漏/源端连接至该第一漏/源结构。

4、为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合所附的附图,作详细说明如下:

技术特征:1.一种运用于物理不可复制技术的反熔丝型一次编程存储单元,包括:

2.如权利要求1所述的反熔丝型一次编程存储单元,其中该第一纳米线与该第二纳米线沿着一条线排列,该条线垂直于半导体基板的表面,且该第一栅极结构形成于该半导体基板的上方。

3.如权利要求1所述的反熔丝型一次编程存储单元,其中该第一纳米线与该第二纳米线沿着一方向水平地排列,该方向平行于半导体基板的表面,且该第一栅极结构形成于该半导体基板的上方。

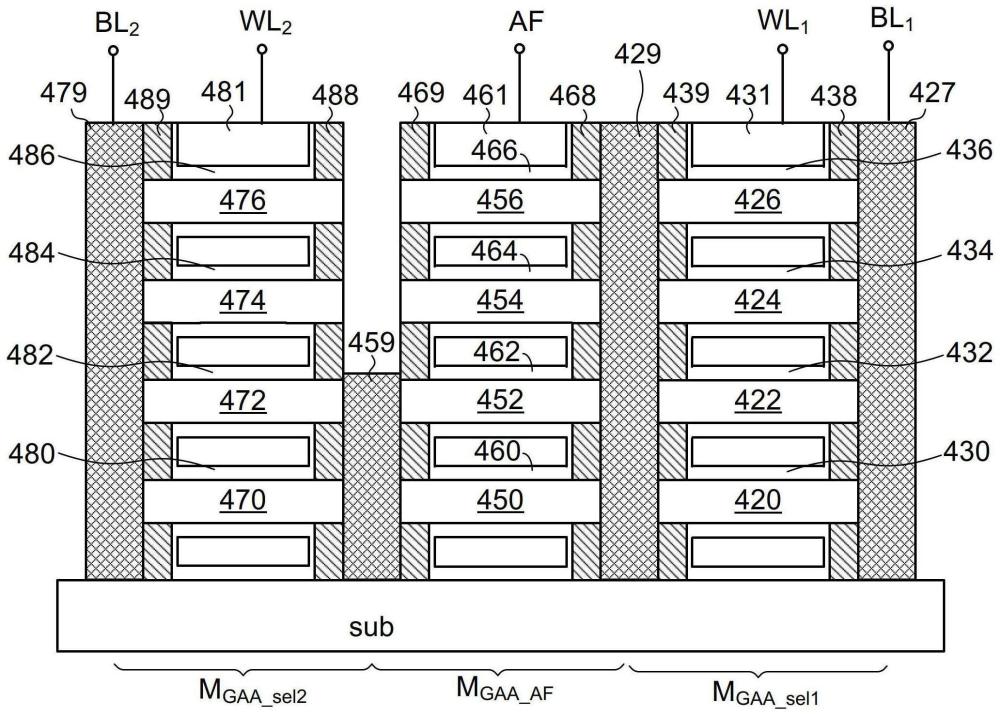

4.如权利要求1所述的反熔丝型一次编程存储单元,其中该第一晶体管为第一选择晶体管,该第二晶体管为第二选择晶体管,该第一选择晶体管的第一漏/源端连接至第一位线,该第一选择晶体管的栅极端连接至第一字线,该第一选择晶体管的第二漏/源端连接至该第一漏/源结构,该第二选择晶体管的第一漏/源端连接至该第二漏/源结构,该第二选择晶体管的栅极端连接至第二字线,该第二选择晶体管的第二漏/源端连接至第二位线,该反熔丝控制线与该第一位线之间为注册路径,该反熔丝控制线与该第二位线之间为第一读取路径。

5.如权利要求4所述的反熔丝型一次编程存储单元,在注册动作时,该注册路径开启,该第一读取路径关闭,该反熔丝控制线接收注册电压,该第一位线接收接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

6.如权利要求5所述的反熔丝型一次编程存储单元,其中在读取动作时,该注册路径关闭,该第一读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收该接地电压,使得该第二位线接收读取电流,并根据该读取电流的大小决定一位的随机码。

7.如权利要求4所述的反熔丝型一次编程存储单元,其中该第一选择晶体管包括:

8.如权利要求7所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

9.如权利要求7所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

10.如权利要求9所述的反熔丝型一次编程存储单元,其中该反熔丝控制线与该第三位线之间为第二读取路径,在读取动作时,该注册路径关闭,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收接地电压,该第三位线接收该接地电压,该第二位线接收第一读取电流,该第三位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

11.如权利要求1所述的反熔丝型一次编程存储单元,还包括第一选择晶体与第二选择晶体管,其中该第一晶体管为第一跟随晶体管,该第二晶体管为第二跟随晶体管,该第一选择晶体管的第一漏/源端连接至第一位线,该第一选择晶体管的栅极端连接至第一字线,该第一跟随晶体管的第一漏/源端连接至该第一选择晶体管的第二漏/源端,该第一跟随晶体管的一栅极端连接至第一跟随控制线,该第一跟随晶体管的第二漏/源端连接至该第一漏/源结构,该第二跟随晶体管的第一漏/源端连接至该第二漏/源结构,该第二跟随晶体管的栅极端连接至第二跟随控制线,该第二选择晶体管的第一漏/源端连接至该第二跟随晶体管的第二漏/源端,该第二选择晶体管的栅极端连接至第二字线,该第二选择晶体管的第二漏/源端连接至第二位线,该反熔丝控制线与该第一位线之间为注册路径,该反熔丝控制线与该第二位线之间为第一读取路径。

12.如权利要求11所述的反熔丝型一次编程存储单元,在注册动作时,该注册路径开启,该第一读取路径关闭,该反熔丝控制线接收注册电压,该第一位线接收接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

13.如权利要求12所述的反熔丝型一次编程存储单元,其中在读取动作时,该注册路径关闭,该第一读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收该接地电压,使得该第二位线接收读取电流,并根据该读取电流的大小决定一位的随机码。

14.如权利要求11所述的反熔丝型一次编程存储单元,其中该第一跟随晶体管包括:

15.如权利要求14所述的反熔丝型一次编程存储单元,其中该第一选择晶体管包括:

16.如权利要求15所述的反熔丝型一次编程存储单元,其中该第二跟随晶体管包括:

17.如权利要求16所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

18.如权利要求15所述的反熔丝型一次编程存储单元,其中该第二跟随晶体管包括:

19.如权利要求18所述的反熔丝型一次编程存储单元,其中该第二选择电晶包括:

20.如权利要求19所述的反熔丝型一次编程存储单元,其中该反熔丝控制线与该第三位线之间为第二读取路径,在读取动作时,该注册路径关闭,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收接地电压,该第三位线接收该接地电压,该第二位线接收第一读取电流,该第三位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

21.一种运用于物理不可复制技术的反熔丝型一次编程存储单元,包括:

22.如权利要求21所述的反熔丝型一次编程存储单元,其中该第一晶体管为第一选择晶体管,该第二晶体管为第二选择晶体管,该第一选择晶体管的第一漏/源端连接至第一位线,该第一选择晶体管的栅极端连接至字线,该第一选择晶体管的第二漏/源端连接至该第一漏/源结构,该第二选择晶体管的第一漏/源端连接至该第三漏/源结构,该第二选择晶体管的栅极端连接至该字线,该第二选择晶体管的第二漏/源端连接至第二位线。

23.如权利要求22所述的反熔丝型一次编程存储单元,在注册动作时,该反熔丝控制线与该第一位线之间为第一注册路径,该反熔丝控制线与该第二位线之间为第二注册路径,该第一注册路径与该第二注册路径开启,该反熔丝控制线接收注册电压,该第一位线接收接地电压,该第二位线接收该接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

24.如权利要求23所述的反熔丝型一次编程存储单元,其中在读取动作时,该反熔丝控制线与该第一位线之间为第一读取路径,该反熔丝控制线与该第二位线之间为第二读取路径,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第一位线接收该接地电压,该第二位线接收该接地电压,该第一位线接收第一读取电流,该第二位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

25.如权利要求22所述的反熔丝型一次编程存储单元,其中该第一选择晶体管包括:

26.如权利要求25所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

27.如权利要求21所述的反熔丝型一次编程存储单元,还包括第一选择晶体与第二选择晶体管,其中该第一晶体管为第一跟随晶体管,该第二晶体管为第二跟随晶体管,该第一选择晶体管的第一漏/源端连接至第一位线,该第一选择晶体管的栅极端连接至字线,该第一跟随晶体管的第一漏/源端连接至该第一选择晶体管的第二漏/源端,该第一跟随晶体管的栅极端连接至跟随控制线,该第一跟随晶体管的第二漏/源端连接至该第一漏/源结构,该第二跟随晶体管的第一漏/源端连接至该第三漏/源结构,该第二跟随晶体管的栅极端连接至该跟随控制线,该第二选择晶体管的第一漏/源端连接至该第二跟随晶体管的第二漏/源端,该第二选择晶体管的栅极端连接至该字线,该第二选择晶体管的第二漏/源端连接至第二位线。

28.如权利要求27所述的反熔丝型一次编程存储单元,在注册动作时,该反熔丝控制线与该第一位线之间为第一注册路径,该反熔丝控制线与该第二位线之间为第二注册路径,该第一注册路径与该第二注册路径开启,该反熔丝控制线接收注册电压,该第一位线接收接地电压,该第二位线接收该接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

29.如权利要求28所述的反熔丝型一次编程存储单元,其中在读取动作时,该反熔丝控制线与该第一位线之间为第一读取路径,该反熔丝控制线与该第二位线之间为第二读取路径,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第一位线接收该接地电压,该第二位线接收该接地电压,该第一位线接收第一读取电流,该第二位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

30.如权利要求27所述的反熔丝型一次编程存储单元,其中该第一跟随晶体管包括:

31.如权利要求30所述的反熔丝型一次编程存储单元,其中该第一选择晶体管包括:

32.如权利要求31所述的反熔丝型一次编程存储单元,其中该第二跟随晶体管包括:

33.如权利要求32所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

34.一种运用于物理不可复制技术的反熔丝型一次编程存储单元,包括:

35.如权利要求34所述的反熔丝型一次编程存储单元,其中该第一纳米线与该第二纳米线沿着一条线排列,该条线垂直于半导体基板的表面,且该第一栅极结构形成于该半导体基板的上方。

36.如权利要求34所述的反熔丝型一次编程存储单元,其中该第一纳米线与该第二纳米线沿着一方向水平地排列,该方向平行于半导体基板的表面,且该第一栅极结构形成于该半导体基板的上方。

37.如权利要求34所述的反熔丝型一次编程存储单元,其中该第一晶体管为第一选择晶体管,该第二晶体管为第二选择晶体管,该第二漏/源结构连接至第一位线,该第二栅极层连接至第一字线,该第二选择晶体管的第一漏/源端连接至该第一漏/源结构,该第二选择晶体管的栅极端连接至第二字线,该第二选择晶体管的第二漏/源端连接至第二位线,该反熔丝控制线与该第一位线之间为注册路径,该反熔丝控制线与该第二位线之间为第一读取路径。

38.如权利要求37所述的反熔丝型一次编程存储单元,在注册动作时,该注册路径开启,该第一读取路径关闭,该反熔丝控制线接收注册电压,该第一位线接收一接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

39.如权利要求38所述的反熔丝型一次编程存储单元,其中在读取动作时,该注册路径关闭,该第一读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收该接地电压,使得该第二位线接收读取电流,并根据该读取电流的大小决定一位的随机码。

40.如权利要求37所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

41.如权利要求37所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

42.如权利要求41所述的反熔丝型一次编程存储单元,其中该反熔丝控制线与该第三位线之间为第二读取路径,在读取动作时,该注册路径关闭,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收接地电压,该第三位线接收该接地电压,使得该第二位线接收第一读取电流,使得该第三位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

43.如权利要求34所述的反熔丝型一次编程存储单元,还包括第一选择晶体与第二选择晶体管,其中该第一晶体管为第一跟随晶体管,该第二晶体管为第二跟随晶体管,该第一选择晶体管的第一漏/源端连接至第一位线,该第一选择晶体管的栅极端连接至第一字线,该第一选择晶体管的第二漏/源端连接至该第二漏/源结构,该第二栅极层连接至第一跟随控制线,该第二跟随晶体管的第一漏/源端连接至该第一漏/源结构,该第二跟随晶体管的栅极端连接至第二跟随控制线,该第二选择晶体管的第一漏/源端连接至该第二跟随晶体管的第二漏/源端,该第二选择晶体管的栅极端连接至第二字线,该第二选择晶体管的第二漏/源端连接至第二位线,该反熔丝控制线与该第一位线之间为注册路径,该反熔丝控制线与该第二位线之间为第一读取路径。

44.如权利要求43所述的反熔丝型一次编程存储单元,在注册动作时,该注册路径开启,该第一读取路径关闭,该反熔丝控制线接收注册电压,该第一位线接收接地电压,使得该第一栅极介电层与该第二栅极介电层其中之一破裂。

45.如权利要求44所述的反熔丝型一次编程存储单元,其中在读取动作时,该注册路径关闭,该第一读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收该接地电压,使得该第二位线接收读取电流,并根据该读取电流的大小决定一位的随机码。

46.如权利要求43所述的反熔丝型一次编程存储单元,其中该第一选择晶体管包括:

47.如权利要求46所述的反熔丝型一次编程存储单元,其中该第二跟随晶体管包括:

48.如权利要求47所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

49.如权利要求46所述的反熔丝型一次编程存储单元,其中该第二跟随晶体管包括:

50.如权利要求49所述的反熔丝型一次编程存储单元,其中该第二选择晶体管包括:

51.如权利要求50所述的反熔丝型一次编程存储单元,其中该反熔丝控制线与该第三位线之间为第二读取路径,在读取动作时,该注册路径关闭,该第一读取路径与该第二读取路径开启,该反熔丝控制线接收读取电压,该第二位线接收接地电压,该第三位线接收该接地电压,该第二位线接收第一读取电流,该第三位线接收第二读取电流,并根据该第一读取电流与该第二读取电流的大小决定一位的随机码。

技术总结本发明公开一种用于物理不可复制技术的带环绕式栅极晶体管一次编程存储单元,其中反熔丝型一次编程存储单元,至少包括:一第一纳米线、一第二纳米线、一第一第一栅极结构、一第一漏/源结构与一第二漏/源结构。第一栅极结构包括:一第一栅极介电层、一第二栅极介电层与一第一栅极层。第一纳米线被第一栅极介电层所环绕。第二纳米线被第二栅极介电层所环绕。第一栅极介电层与第二栅极介电层被第一栅极层所环绕。第一漏/源结构电性接触于第一纳米线的第一端与第二纳米线的第一端。第二漏/源结构电性接触于第一纳米线的第二端。第二漏/源结构未电性接触于第二纳米线的第二端。技术研发人员:陈稐寯,何秉隆受保护的技术使用者:力旺电子股份有限公司技术研发日:技术公布日:2024/1/22本文地址:https://www.jishuxx.com/zhuanli/20240731/183109.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表