可电擦写的非易失性半导体存储装置的制作方法

- 国知局

- 2024-07-31 19:39:13

本技术实施例涉及半导体,特别涉及一种可电擦写的非易失性半导体存储装置。

背景技术:

1、近年来,对低成本、非易失性和可编程存储元件的需求日益增加。这是因为:1、随着微处理器单元(mpu)/微控制器单元(mcu)和片上系统(soc)芯片中sram容量的增加,对冗余存储器的需求也在增加。2、液晶显示器(lcd)中对低成本、非易失性和可编程保险丝元件的需求也在增加。3、液晶显示器驱动器等应用领域的拓展,这些应用领域包括调整应用及个人身份和安全信息,例如,id码、解密密钥和ic卡注册号等,这些应用领域的设置在安装到电路板上后可单独更改。

2、可以通过标准cmos制造工艺形成的传统非易失性存储器包括熔断存储器,这些存储器使用多晶硅或者布线金属层,通过激光或者电流熔断,或者使用绝缘栅极薄膜,通过电压破坏。但是,由于熔断存储器使用的是熔断或者介电击穿现象,因此,只能进行一次编程,不适用于上述这样需要重写的应用场景。

3、另一方面,电浮动栅极型的非易失性存储元件可以用作保险丝元件,并且可以进行电擦除和编程,但必须在标准cmos结构的晶体管添加电气浮置的栅极。即为了形成电浮动栅极,需要在标准cmos的制造工序中增加一个额外的制造工序,因此会导致制造成本的增加,对其应用产生限制。

4、参考日本出版的专利公报中的专利文献2006-66529,使用现有标准cmos工艺制造的单层多晶硅结构的非易失性存储器单元的制造如下:

5、参考图1,图1为一种非易失性存储单元的横截面结构示意图,使用标准cmos工艺制造的具有单层多晶硅结构的非易失性存储单元包括p型衬底21和位于p型衬底21上的p型阱23和n型阱24,其中,p型衬底21的电阻率可以为10ω·cm,n型阱24的平均磷掺杂浓度为2×1017/cm3,p型阱23的平均硼掺杂浓度为3×1017/cm3。

6、n型阱24包括n型掺杂区33和p型掺杂区28,n型掺杂区33和p型掺杂区28被深度为300nm的器件分离氧化膜22电隔离。选择晶体管st的源极29、漏极30、栅极绝缘膜25和选择栅极26均形成于p型阱23中,并由300nm深的器件分离氧化膜22进行电气隔离。

7、在栅极绝缘膜25设置在p型阱23和n型阱24远离p型衬底21的表面上,并分别与p型掺杂区28和源极29相连,栅极绝缘膜25远离p型衬底21的表面上设置有浮动栅极27,浮动栅极27覆盖栅极绝缘膜25远离p型衬底21的表面。

8、n型阱24与浮动栅极27之间的重叠区域可以作为耦合电容c2,其中,n型阱24与浮动栅极27的重叠区域指的是n型阱24和浮动栅极27正对的部分。p型阱23和浮动栅极27之间的重叠区域可以作为存储晶体管mt的晶体管通道,其中,p型阱23与浮动栅极27之间的重叠区域指的是p型阱23和浮动栅极27正对的部分。在编程操作过程中,n型阱24应用编程字线pwl电位时,可以控制浮动栅极27的电位,此外,在读取操作期间,n型阱24连接到源极线路vss。

9、在编程操作过程中,施加在n型阱24上的正电压与施加在与编程位线pbl相连的p型掺杂区28上的负电压之间的电位差,会被施加到p型掺杂区28的结点上,基于带间隧穿现象产生的热电子31被注入浮动栅极27,电子在浮动栅极27积聚,并且通过与n型阱24的静电耦合,浮动栅极27会被提升到正电位。

10、结合参考图1和图2,图2为单层多晶硅结构的非易失性存储单元的等效电路图。电荷注入区的耦合电容c2和结电容cj与带有栅极电容c1的存储晶体管mt的浮动栅极27相连。选择晶体管st的漏极30连接到读取位线rbl,电荷注入区连接到编程位线pbl,耦合电容器c2连接到编程字线pwl,其中,耦合电容c2的电容值可以设置为存储晶体管mt的栅极电容c1的电容值与电荷注入区的结点电容器cj的电容值之和,且耦合电容c2与浮动栅极27之间的静电耦合比为0.5左右。

11、参考图3,图3为单层多晶硅结构的非易失性存储单元的平面结构示意图。图3中,有源区41横跨n型阱34和p型阱32,在有源区41中,设置有一个选择晶体管的漏极30、一个选择栅极26(图中未示出)以及一个源极29和一个p型掺杂区28。在源极29和p型掺杂区28之间设置一个浮动栅极27(图中未示出),漏极30通过一个接触孔44连接到一个由第一金属膜46组成的读取位线45,而p型掺杂区28则连接到一个接触孔44,通过接触孔44与第一金属膜46相连,第一金属膜46通过连接孔47与由第二金属膜组成的编程位线48相连,n型阱34作为编程字线和用于读取的共源极线。

12、结合参考图1、图3和图4,图4为单层多晶硅结构的非易失性存储单元的工作电压条件示意图。在进行编程操作时,是通过向浮动栅极27注入由带间隧穿现象产生的热电子来实现的,编程操作过程中可以先在编程字线pwl上施加正电压,例如,施加3.3v的正电压,即电源电压;然后在编程位线pbl上施加负电压,例如,-2v的负电压。在这种编程操作中,编程位线pbl线上的电流约为100na,编程时间约为10µs,因此编程功耗为5pj,编程后存储晶体管的阈值电压vth约为5v。其中,晶体管的阈值电压vth指的是,晶体管建立导电沟道从而由关断状态进入导通状态时,晶体管的临界栅极电压。

13、读取操作是通过调整存储晶体管的导通状态实现的,在读取操作过程中,可以向读取位线rbl施加大小约为1v的电压,然后向选择晶体管的栅极施加3.3v的电压,即电源电压,并根据存储晶体管处于导通状态还是关断状态实现对存储晶体管的读取操作。

14、采用标准cmos工艺形成的单层多晶硅结构的非易失性存储单元有多种擦除操作方法。一种擦除方法是在编程位线pbl和编程字线pwl上施加正电压,例如,大小为5v的正电压等,并通过福勒-诺德海姆隧道(f-n隧道)电流将电子从浮动栅极27发射到p型掺杂区28,通过这种擦除方法进行擦除操作所需的擦除时间约为200毫秒,擦除后存储晶体管的阈值电压vth约为0.5v。

15、另一种擦除方法是,向编程位线pbl和选择栅极26上施加诸如6v的电压,以打开选择晶体管,并将选择晶体管的源极29充电至诸如5.5v的电位。这种情况下,电子通过f-n隧道电流从浮动栅极27发射到源极29。这种擦除方法进行擦除操作所需的擦除时间约为100毫秒,擦除后存储晶体管的阈值电压vth约为0.3v。

16、结合参考图3和图5a至图5d,图5a至图5d均为采用标准cmos工艺形成的单层多晶硅结构的非易失性存储单元的横截面示意图,且每一个截面图与图3所示平面结构中c→c'符号所指示的方向相对应。

17、图5a中所示的制造工艺显示了在电阻率为10ω·cm的p型硅衬底121表面区域按以下方式形成器件分离区124、n型阱122和p型阱123的过程。首先通过干法蚀刻开孔,然后通过化学气相沉积(后续简称cvd)沉积氧化硅薄膜,形成300nm深的器件分离区124,并通过化学机械抛光(后续简称cmp)方法将其平面化。然后,通过热氧化法生长出厚度为10纳米的表面氧化膜140,通过离子注入法注入p(磷)离子形成n型阱122,其中,离子注入的工艺参数包括:离子注入的加速能量包括1mev/1x1013cm2、500kev/3x1012cm2和150kev/1x1012cm2。并通过b(硼)离子注入形成p型阱123,其中,离子注入的工艺参数包括:离子注入的能量包括500kev/1x1013cm2、150kev/3x1012cm2和50kev/1x1012cm2。

18、在图5b所示的制造过程中,显示了以下处理过程。通过湿法蚀刻去除表面氧化膜140,通过热氧化法生成厚度为7纳米的栅极绝缘膜125,用离子注入法向通过化学气相沉积形成的厚度为200nm的多晶硅薄膜中注入加速能量为10kev的磷(p)离子,且注入量为4x1015cm2,用磷(p)离子注入法将注入加速能量为10kev的磷(p)离子注入后,用光刻和干法蚀刻形成浮动栅极126和选择栅极127。在光刻法掩膜之后,通过离子注入法注入加速能量为10kev,且注入量为1.5x1015cm2的bf2离子,形成p型掺杂区128,并通过光刻法绘制光刻胶掩膜141,注入加速能量为10kev,且注入量为1x1015cm2的as(砷)离子142,形成选择晶体管的源极130和漏极129。

19、在图5c所示的生产流程中,显示了以下过程。通过灰化法去除和清洁上述光刻胶掩模141后,通过化学气相沉积法和回蚀刻形成厚度为80nm的氧化膜侧垫片131。仅向p型掺杂区128注入加速能量为20kev,且注入量为2x1015cm2的bf2离子,仅向选择晶体管的源极130和漏极129植入加速能量为30kev,且注入量为2x1015cm2的as(砷)离子,在1000℃的氮气环境中进行10秒钟的高温热处理。在上述浮动栅极126和选择栅极127以及暴露的基底表面上生长厚度为50纳米的硅化钴薄膜132和硅化钴薄膜133,通过化学气相沉积工艺沉积氧化硅薄膜后,通过cmp方法平面化厚度为800nm的接触层间薄膜134,并通过光刻和干蚀刻工艺打开孔径为0.3µm的接触孔,然后采用cvd法沉积,并通过cmp方法进行平面化处理,形成嵌入钨(w)插塞135。

20、在图5d所示的生产过程中,通过溅射法、光刻法和干法蚀刻形成由铝(al)制成的第一金属线136和第一金属线137,且第一金属线136和第一金属线137的厚度均为500nm。然后采用cvd法沉积氧化硅薄膜,形成厚度为800nm的第一层夹层膜138,并通过cmp方法将其平面化,然后通过光刻和干蚀刻工艺开出孔径为0.3μm的通孔,通过采用cvd方法沉积和采用cmp方法平面化,形成嵌入式钨(w)插塞139。然后再通过溅射法、光刻法和干蚀刻法形成由铝(al)制成的第二金属导线143,且第二金属导线143的厚度为500nm。在该工艺完成后,表明本现有技术的标准cmos工艺制造单层多晶硅结构的非易失性存储单元可以使用。

技术实现思路

1、本技术一些实施例提供一种可电擦写的非易失性半导体存储装置,至少有利于提高非易失性半导体存储装置的电重写能力,降低非易失性半导体存储装置的成本和制作难度。

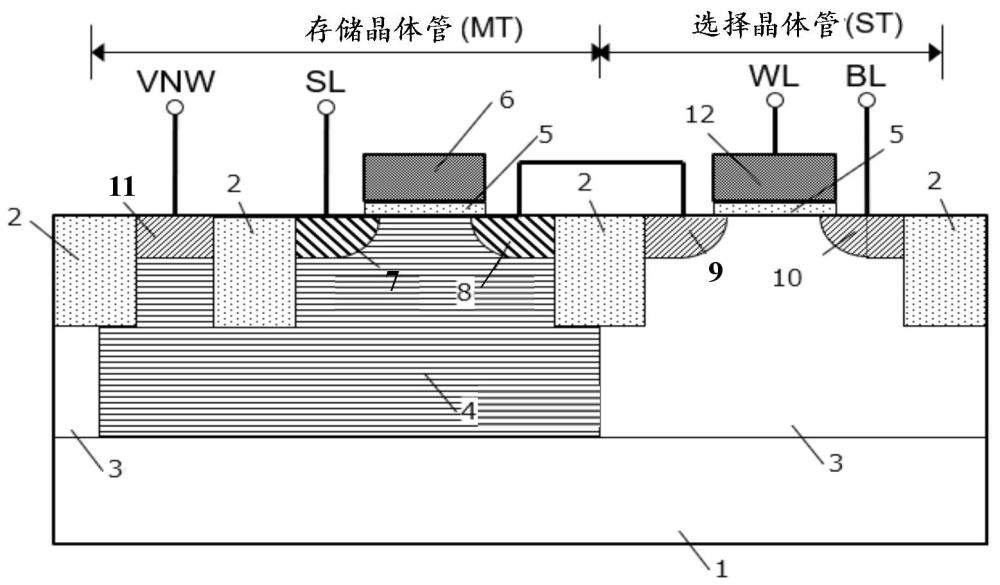

2、本技术实施例一方面提供了一种可电擦写的非易失性半导体存储装置,应用于外部接口电路和逻辑电路,具有至少一个具有单层栅极结构的mis晶体管,包括:选择晶体管,所述选择晶体管包括在第一导电类型阱中具有第二导电类型的源极和第二导电类型的漏极的所述mis晶体管;存储晶体管,所述存储晶体管包括在第二导电类型阱中具有第一导电类型的源极和第一导电类型的漏极的所述mis晶体管;所述选择晶体管的源极与所述存储晶体管的漏极相连,所述选择晶体管的漏极与位线相连,所述选择晶体管的栅极与字线相连;所述存储晶体管的源极与源极线相连,所述存储晶体管的栅极电气浮置;所述存储晶体管与共享所述字线另一所述存储晶体管共享第二导电类型阱。

3、在一些实施例中,所述存储晶体管的阈值电压在所述存储晶体管处于编程状态下为正,在所述存储晶体管处于擦除状态下为负。

4、在一些实施例中,所述存储晶体管的控制方法包括:在所述存储晶体管的编程过程中,将所述存储晶体管的漏极电位设置为公共接地端电位vss,所述存储晶体管的阱电位设置为大于或等于电源电压vcc的值;在所述存储晶体管的擦除过程中,将所述存储晶体管的漏极和源极电气浮置,将所述存储晶体管的阱电位设置为大于编程过程中阱电位的值。

5、本技术实施例另一方面还提供了一种可电擦写的非易失性半导体存储装置,用于外部接口电路和逻辑电路,具有至少一个具有单层栅极结构的mis晶体管,包括:选择晶体管,所述选择晶体管包括在第一导电类型阱中具有第二导电类型的源极和第二导电类型的漏极的所述mis晶体管;存储晶体管,所述存储晶体管包括在第二导电类型的第一阱中具有第一导电类型的源极和第一导电类型的漏极的所述mis晶体管;电容器,所述电容器包括在第二导电类型的第二阱中具有第一导电类型的源极和第一导电类型的漏极的所述mis晶体管;所述选择晶体管的源极与所述存储晶体管的漏极相连,所述选择晶体管的漏极与位线相连,所述选择晶体管的栅极与字线相连;所述存储晶体管的源极与源极线相连,所述存储晶体管的栅极与所述电容器的栅极相连,且处于电气浮置状态;所述电容器的源极和漏极与所述第二阱相连;所述存储晶体管与共享所述字线的另一所述存储晶体管共享第二导电类型的所述第一阱;所述电容器的第二导电类型的所述第二阱不与其他所述存储晶体管和所述电容器共享。

6、在一些实施例中,所述存储晶体管的阈值电压在所述存储晶体管处于编程状态和擦除状态的情况下均为负。

7、在一些实施例中,所述存储晶体管的控制方法包括:在所述存储晶体管的编程过程中,将所述存储晶体管的漏极电位设置为公共接地端电位vss,将所述存储晶体管的阱电位的电位设置为大于或等于电源电压vcc的值,在选择所述字线后,将所述电容器的所述第二阱的电位设定为所述公共接地端电位vss,并将所述第二阱的电位上升至所述电源电压;在所述存储晶体管的擦除过程中,将所述存储晶体管的漏极和源极电气浮置,将所述存储晶体管的所述第一阱的电位值设置为一个大于编程过程中所述第一阱的电位值的值,将所述电容器的所述第二阱的电位从所述电源电压下降到所述公共接地端电位;在读取所述存储晶体管的过程中,将所述电容器的所述第二阱的电位从所述电源电压下降到所述公共接地端电位。

8、本技术实施例提供的技术方案至少具有以下优点:通过标准cmos工艺形成的单层多晶硅结构非易失性存储器单元,存储晶体管通过一个选择晶体管与位线相连,存储晶体管的栅极不与其他存储晶体管共用,因此,存储晶体管在编程过程中受到的干扰大大降低,避免了采用标准cmos工艺制造单层多晶硅结构的非易失性存储器单元易受栅极干扰的问题,即,存储晶体管栅极不与其他存储晶体管共用,且每一个字线都有一个选择晶体管,利用选择晶体管的设置和栅极独立规避了栅极干扰。对于未被选择的位线,施加到位线上的电位为电源电压vcc,选择晶体管不会发生带间隧穿,因此,存储晶体管也不会发生字线干扰。存储晶体管的第一导电类型的源极和第一导电类型的漏极设置在第二导电类型阱中,栅极电气浮置将电子电存储并保持在浮游状态,从而实现存储的非易失性,有效的改善了存储晶体管的保持特性。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183427.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表