支持常规存储器存取模式和数字存储器内计算处理模式两者的存储器架构的制作方法

- 国知局

- 2024-07-31 19:43:15

本文的实施例涉及存储器架构,并且特别地涉及常规存储器存取模式和数字存储器内计算处理模式两者的存储器支持。

背景技术:

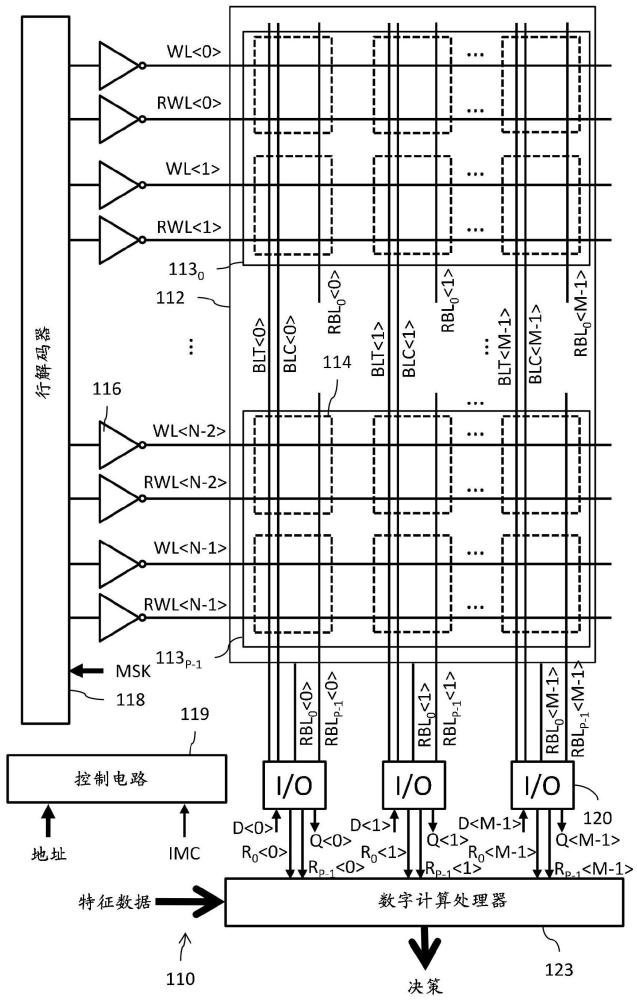

1、参考图1,其示出了模拟存储器内计算电路10的示意图。电路10利用包括静态随机存取存储器(sram)阵列12的存储器电路,该静态随机存取存储器(sram)阵列12由以具有n行和m列的矩阵格式布置的标准6t sram存储器单元14形成。作为替代方案,可以代替地使用标准8t存储器单元或具有类似功能性和拓扑的sram。每个存储器单元14被编程为存储用于存储器内计算操作的计算权重或内核数据的位。在本上下文中,存储器内计算操作被理解为高维矩阵向量乘法(mvm)的一种形式,其支持存储在存储器的多个位单元中的多位权重。位单元的组(在多位权重的情况下)可以被视为虚拟突触元素。计算权重的每一位具有逻辑“1”或逻辑“0”值。

2、每个sram单元14包括字线wl以及一对互补位线blt和blc。8t类型sram单元将附加地包括读字线rwl和读位线rbl。矩阵的公共行中的单元14通过公共字线wl(并且在8t类型实施方式中通过公共读字线rwl)彼此连接。矩阵的公共列中的单元14通过公共的一对互补位线blt和blc(并且在8t型实现中通过公共读取位线rbl)彼此连接。每条字线wl、rwl由字线驱动器电路16驱动,字线驱动器电路16可以被实现为cmos驱动器电路(例如,形成逻辑反相器电路的串联连接的p沟道和n沟道mosfet晶体管对)。施加到字线并且由字线驱动器电路16驱动的字线信号是根据输入到存储器内计算电路10的特征数据生成的并且由行控制器电路18控制。列处理电路20感测用于m列的互补位线对blt和blc上(和/或读位线rbl上)的模拟信号,将模拟信号转换成数字信号,对数字信号执行数字计算并且为存储器内计算操作生成决策输出。

3、虽然图1中未明确示出,但是应该理解的是,电路10还包括本领域技术人员已知的常规行解码电路、列解码电路和读-写电路,其用于与向存储器阵列12的sram单元14写入数据的位(例如,计算权重数据)以及从存储器阵列12的sram单元14读取数据的位结合使用。这个操作被称为常规存储器存取模式并且与上面讨论的模拟存储器内计算操作区分。

4、行控制器电路18接收用于存储器内计算操作的特征数据,并且响应于此而执行选择字线wl<0>至wl<n-1>(或读字线rwl<0>至rwl<n-1>)中的哪些将在模拟存储器内计算操作期间被同时并行访问(或致动)的功能,以及根据该存储器内计算操作控制将脉动信号施加到字线的功能。图1仅以示例的方式图示了用脉动字线信号同时致动所有n条字线,应理解的是,存储器内计算操作可以代替地利用少于sram阵列的所有行的同时致动。给定的互补位线对blt和blc上的模拟信号(或者8t类型实施方式中的读位线rbl上的模拟信号)取决于存储在对应列的存储器单元14中的计算权重的位的逻辑状态以及施加到那些存储器单元14的脉动字线信号的(一个或多个)宽度。

5、图1所示的实施方式示出了采用脉宽调制(pwm)形式的示例,适用于根据接收到的特征数据进行存储器内计算操作的所施加的字线信号。对所施加的字线信号使用pwm或周期脉冲调制(ptm)是基于用于乘法-累加(mac)运算的向量的线性度用于存储器内计算操作的常用技术。脉动字线信号格式还可以发展为编码的脉冲串,以管理存储器内计算操作的特征数据的块稀疏性。相应地认识到,当同时驱动多条字线时,可以使用用于所施加的字线信号的任意组编码方案。此外,在更简单的实施方式中,应理解的是,同时致动的所有施加的字线信号可以代替地具有相同的脉冲宽度。

6、模拟存储器内计算操作存在许多问题,包括:对存储器的并行同时字线访问可能导致无意的位翻转,这扰乱所存储的权重数据的逻辑状态;乘法和累加(mac)运算采用共享信号线上的模拟信号电平形式,并进行模数转换;由于模拟信号电平变化,计算本质上是近似值;而且电路布置复杂并且可测试性是个挑战。因此,模拟存储器内计算的方案对于需要确定性计算(诸如安全性或保障性)的应用来说是不可接受的。优选地执行数字计算或可预测的计算。

技术实现思路

1、一种电路,包括:存储器阵列,包括多个子阵列,其中每个子阵列包括以多行和多列的矩阵布置的存储器单元,每行包括连接到该行的存储器单元的字线,并且每列包括连接到该列的存储器单元的局部位线;用于每行的字线驱动电路,具有被连接成驱动该行的字线的输出端;以及行解码器电路,耦合到字线驱动电路。

2、控制电路被配置为支持存储器电路操作的两种模式,包括:第一模式,其中行解码器电路在存储器存取操作期间仅致动存储器阵列中的一条字线;以及第二模式,其中行解码器电路在存储器内计算操作期间同时致动每个子阵列中的一条字线。

3、在实施例中,用于每列的输入/输出电路包括:多个位线输入端,耦合到子阵列的局部位线;列数据输出端,耦合到多个位线输入端并且被配置为生成用于在第一模式下输出的列数据位;以及多个子阵列数据输出端,其中每个子阵列数据输出端耦合到多个位线输入端中的对应一个,并且被配置为生成用于在第二模式下输出的多个子阵列数据位。处理电路被配置为接收特征数据并执行作为特征数据和多个子阵列数据位的函数的计算操作。

4、在另一个实施例中,用于每列的输入/输出电路包括:多个位线输入端,耦合到子阵列的局部位线;列数据输出端,耦合到多个位线输入端并且被配置为生成用于在第一模式下输出的列数据位;计算电路,被配置为存储特征数据并执行作为特征数据和存在于多个位线输入端处的多个子阵列数据位的函数的计算操作以生成多个计算数据位;以及多个子阵列数据输出端,耦合到计算电路并且被配置为在第二模式下输出多个计算数据位。处理电路被配置为接收多个计算数据位并且执行应用特定信号处理操作。

技术特征:1.一种电路,包括:

2.如权利要求1所述的电路,其中每个存储器单元是静态随机存取存储器(sram)单元。

3.如权利要求2所述的电路,其中sram单元是8t类型单元,其中字线是8t类型单元的读字线并且局部位线是8t类型单元的读位线。

4.如权利要求2所述的电路,其中sram单元是6t类型单元,其中字线是6t类型单元的字线并且局部位线是用于6t类型单元的互补的位线对中的一条位线。

5.如权利要求1所述的电路,其中每个存储器单元是具有确定性输出的非易失性存储器单元。

6.如权利要求1所述的电路,其中用于每列的输入/输出电路在每个位线输入端和对应的子阵列数据输出端之间还包括:

7.如权利要求6所述的电路,其中用于每列的输入/输出电路还包括耦合在位线输入端与第一多路复用电路的第一输入端之间的读电路。

8.如权利要求6所述的电路,其中用于每列的输入/输出电路在所述多个位线输入端和列数据输出端之间还包括:

9.如权利要求8所述的电路,其中用于每列的输入/输出电路还包括耦合在所述多个位线输入端与第二多路复用电路的第一输入端之间的读电路。

10.如权利要求1所述的电路,其中用于每列的输入/输出电路在耦合到存储器阵列的列数据输入端与列写入位线之间还包括:

11.如权利要求10所述的电路,其中用于每列的输入/输出电路在每个位线输入端与对应的子阵列数据输出端之间还包括:

12.如权利要求11所述的电路,其中用于每列的输入/输出电路在每个位线输入端与对应的子阵列数据输出端之间还包括:

13.如权利要求11所述的电路,其中反相控制信号与所述多个子阵列中的特定子阵列相关联。

14.如权利要求1所述的电路:

15.如权利要求14所述的电路,其中在第一模式下,所述多个子解码器电路中仅一个生成一个字线信号,并且其中在第二模式下,所述多个子解码器电路中的每个子解码器电路在字线上生成一个字线信号。

16.如权利要求15所述的电路,其中控制电路被配置为生成掩蔽信号,并且其中所述多个子解码器电路中的每个子解码器电路响应于掩蔽信号而被选择性地使能以生成所述一个字线信号。

17.如权利要求1所述的电路:

18.如权利要求1所述的电路:

19.一种电路,包括:

20.如权利要求19所述的电路,其中用于每列的输入/输出电路在每个位线输入端和对应的子阵列数据输出端之间还包括:

21.如权利要求20所述的电路,其中用于每列的输入/输出电路还包括耦合在位线输入端与第一多路复用电路的第一输入端之间的读电路。

22.如权利要求20所述的电路,其中用于每列的输入/输出电路在所述多个位线输入端和列数据输出端之间还包括:

23.如权利要求22所述的电路,其中用于每列的输入/输出电路还包括耦合在所述多个位线输入端与第二多路复用电路的第一输入端之间的读电路。

24.一种电路,包括:

25.如权利要求24所述的电路,还包括处理电路,该处理电路耦合到所述多个子阵列数据输出端并且被配置为处理所述多个部分计算数据位。

26.如权利要求24所述的电路,其中计算操作是布尔运算。

27.如权利要求26所述的电路,其中布尔运算选自异或运算、异或非运算、与非运算和或非运算。

28.如权利要求24所述的电路,其中计算操作是向量处理运算。

29.如权利要求24所述的电路,其中控制电路被配置为生成掩蔽信号,并且其中响应于掩蔽信号而选择性地使能对每个子阵列数据位的计算操作的执行。

30.如权利要求24所述的电路,其中每个存储器单元是静态随机存取存储器(sram)单元。

31.如权利要求30所述的电路,其中sram单元是8t类型单元,其中字线是8t类型单元的读字线并且局部位线是8t类型单元的读位线。

32.如权利要求30所述的电路,其中sram单元是6t类型单元,其中字线是6t类型单元的字线并且局部位线是用于6t类型单元的互补的位线对中的一条位线。

33.如权利要求24所述的电路,其中每个存储器单元是具有确定性输出的非易失性存储器单元。

34.如权利要求24所述的电路,其中用于每列的输入/输出电路:

35.如权利要求34所述的电路,其中用于每列的所述输入/输出电路还包括耦合在位线输入端与第一多路复用电路的第一输入端之间的读电路。

36.如权利要求34所述的电路,其中用于每列的输入/输出电路:

37.如权利要求36所述的电路,其中用于每列的输入/输出电路还包括耦合在所述多个位线输入端与第二多路复用电路的第一输入端之间的读电路。

38.如权利要求24所述的电路:

39.如权利要求38所述的电路,其中在第一模式下,所述多个子解码器电路中仅一个子解码器电路生成一个字线信号,并且其中在第二模式下,所述多个子解码器电路中的每个子解码器电路在字线上生成一个字线信号。

40.如权利要求39所述的电路,其中控制电路被配置为生成掩蔽信号,并且其中所述多个子解码器电路中的每个子解码器电路响应于掩蔽信号而被选择性地使能以生成所述一个字线信号。

41.如权利要求24所述的电路:

42.如权利要求24所述的电路:

技术总结本公开涉及支持常规存储器存取模式和数字存储器内计算处理模式两者的存储器架构。电路的存储器阵列包括具有以行‑列矩阵布置的存储器单元的子阵列,其中每行包括字线并且每个子阵列的列包括局部位线。控制电路支持两种电路操作模式:第一模式,其中在存储器读期间仅致动存储器阵列中的一条字线;以及第二模式,其中在存储器读期间同时致动每个子阵列中的一条字线。用于每列的输入/输出电路包括到子阵列的局部位线的输入端、耦合到位线输入端的列数据输出端,以及耦合到每个位线输入端的子阵列数据输出端。在存储器中,根据存储在存储器中的特征数据和权重数据在第二模式下执行计算操作。技术研发人员:H·拉瓦特,N·乔拉,P·库玛,K·J·多里,M·阿约提亚瓦西受保护的技术使用者:意法半导体国际公司技术研发日:技术公布日:2024/3/4本文地址:https://www.jishuxx.com/zhuanli/20240731/183659.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。