非易失性存储单元以及装置、计算存储单元以及装置的制作方法

- 国知局

- 2024-07-31 19:44:59

本发明涉及存储器,具体涉及一种非易失性存储单元、装置、设备及存储介质。

背景技术:

1、目前,商业中最常用的sram(static random-access memory,静态随机存取存储器)为6t-cell(6晶体管)结构,即由两个反相器和两个选通管组成,一个sram结构中共6根场效应晶体管。而在数字型存内计算电路中,为了能够实现更好的数据稳定性以及防止多行读取过程中的读破坏风险,在6t-sram的基础上改进了8t-sram、9t-sram和10t-sram等新型结构,sram的集成度进一步降低。而在整体的数字型存内计算架构中,sram存算阵列的面积占比最大,在整体架构中起着关键性的作用,决定着电路系统性能的优劣。过大的单个sram面积提高了后端布局布线的难度,使得在设计中不得不增加面积开销,极大的降低了存算芯片的面积利用率。并且sram属于易失性存储单元,断电后无法维持存储状态,信号快速衰减,维持正常的电源电压则会提高电路工作的功耗。因此,目前亟需一种面积开销小的非易失性数字型存算单元的设计方案。

技术实现思路

1、鉴于上述问题,本发明实施例提供了一种非易失性存储单元,用于解决现有技术中sram存算阵列的面积占比较大的技术问题。

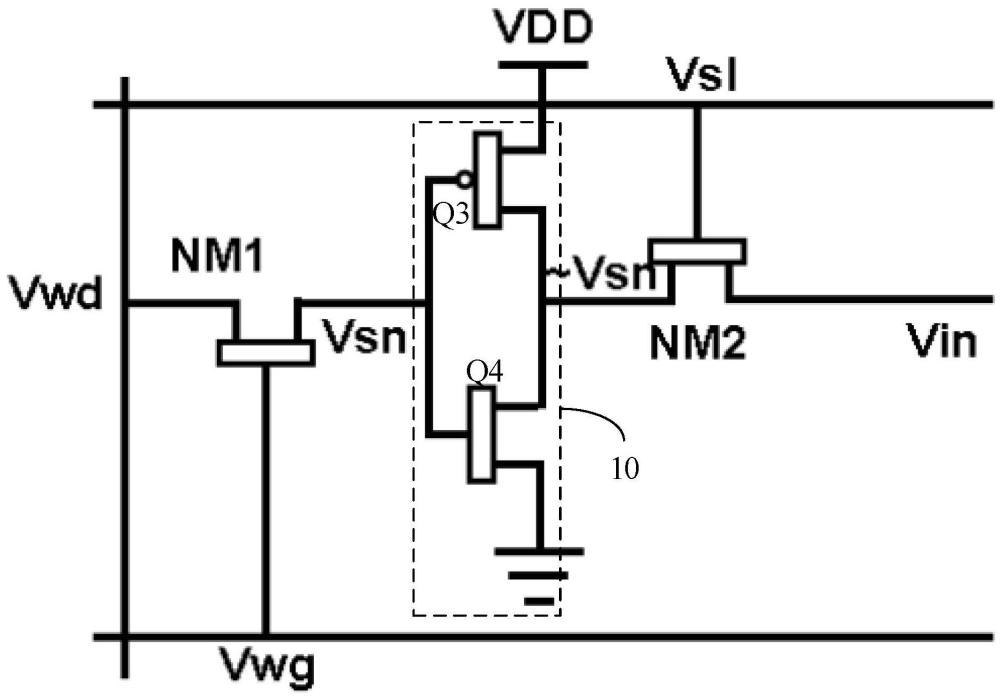

2、根据本发明实施例的一个方面,提供了一种非易失性存储单元,包括第一晶体管、第二晶体管、反相器、第一过程控制端、第二过程控制端、信号输入端以及信号输出端;所述第一晶体管的第一端与所述信号输入端连接,所述第一晶体管的第二端与所述反相器的第一端连接,所述第一晶体管的受控端与所述第一过程控制端连接;所述第二晶体管的第一端与所述反相器的第二端连接,所述第二晶体管的第二端与所述信号输出端连接,所述第二晶体管的受控端与所述第二过程控制端连接;

3、所述第一过程控制端,用于获取第一过程控制信号;

4、所述第二过程控制端,用于获取第二过程控制信号;

5、所述信号输入端,用于获取存储信号;

6、所述第一晶体管,用于根据所述第一过程控制信号导通或者关断;

7、所述第二晶体管,用于根据所述第二过程控制信号导通或者关断;

8、所述反相器,用于在所述第一晶体管关断且所述第二晶体管导通时,将所述反相器所存储的所述存储信号反相输出。

9、在一种可选的方式中,当所述第一晶体管关断时,所述第一晶体管的泄露电流小于第一预设电流值。

10、在一种可选的方式中,所述反相器包括第三晶体管以及第四晶体管,所述第三晶体管与所述第四晶体管其中之一为nmos管,另一为pmos管。

11、在一种可选的方式中,所述第一晶体管以及所述第二晶体管通过氧化铟镓锌工艺制造。

12、在一种可选的方式中,所述非易失性存储单元还包括逻辑门,所述逻辑门设置于所述第二晶体管的第二端与所述信号输出端之间,所述逻辑门的第一端接入所述第二晶体管输出的所述存储信号,所述逻辑门的第二端接入特征信号;

13、所述逻辑门,用于将所述存储信号以及所述特征信号进行逻辑运算后输出。

14、在一种可选的方式中,所述逻辑门为或非门。

15、在一种可选的方式中,当所述第一过程控制信号为高电平,所述第二过程控制信号低电平时,所述非易失性存储单元处于写入状态,以写入所述存储信号;

16、当所述第一过程控制信号为低电平,所述第二过程控制信号为低电平时,所述非易失性存储单元处于保持状态,以将写入的所述存储信号存储在所述反相器中;

17、当所述第一过程控制信号为低电平,所述第二过程控制信号为高电平时,所述非易失性存储单元处于读取状态,以将存储的所述存储信号通过所述反相器后输出。

18、根据本发明实施例的另一方面,提供了一种计算存储单元,所述计算存储单元包括n个第一字线、n个第二字线、m个第一位线以及多个如权利要求1-8任一项所述的非易失性存储单元;多个所述非易失性存储单元组成n*m的存储矩阵,n以及m均大于或等于1;第n行的每一所述非易失性存储单元的第一晶体管的受控端均连接至第n个所述第一字线,第n行的每一所述非易失性存储单元的第二晶体管的受控端均连接至第n个所述第二字线;第m列所述非易失性存储单元的第一晶体管的第一端均连接至第m个所述第一位线;

19、所述所述第一字线,用于获取多个第一过程控制信号;

20、所述第二字线,用于获取多个第二过程控制信号;

21、所述第一位线,用于传输存储信号;

22、所述非易失性存储单元,用于根据所述第一过程控制信号以及所述第二过程控制信号进行所述存储信号的存储、保持以及输出等操作。

23、在一种可选的方式中,所述计算存储单元还包括移位加法器,每一所述存储单元的逻辑门的输出端均连接至所述移位加法器;

24、所述移位加法器,用于将每一所述存储单元输出的所述存储信号进行存内运算。

25、根据本发明实施例的另一方面,提供了一种非易失性存储装置,所述非易失性存储装置包括上所述的非易失性存储单元。

26、根据本发明实施例的又一方面,提供了计算存储装置,所述计算存储装置包括如上所述的计算存储单元。

27、本发明实施例通过第一过程控制端获取第一过程控制信号,所述第二过程控制端获取第二过程控制信号,信号输入端获取存储信号,其中,所述第一晶体管根据所述第一过程控制信号导通或者关断,所述第二晶体管根据所述第二过程控制信号导通或者关断,所述反相器在所述第一晶体管关断且所述第二晶体管导通时,将所述反相器所存储的所述存储信号反相输出。从而可以通过第一晶体管以及第二晶体管的关断以及导通组合分别实现存储信号的写入、存储信号的读出以及存储信号的保存,从而实现了存储单元的存储以及读取功能,而且减少了晶体管的使用数量,从而解决了现有技术中sram存算阵列的面积占比较大的技术问题。

28、上述说明仅是本发明实施例技术方案的概述,为了能够更清楚了解本发明实施例的技术手段,而可依照说明书的内容予以实施,并且为了让本发明实施例的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

技术特征:1.一种非易失性存储单元,其特征在于,所述非易失性存储单元包括第一晶体管、第二晶体管、反相器、第一过程控制端、第二过程控制端、信号输入端以及信号输出端;所述第一晶体管的第一端与所述信号输入端连接,所述第一晶体管的第二端与所述反相器的第一端连接,所述第一晶体管的受控端与所述第一过程控制端连接;所述第二晶体管的第一端与所述反相器的第二端连接,所述第二晶体管的第二端与所述信号输出端连接,所述第二晶体管的受控端与所述第二过程控制端连接;

2.根据权利要求1所述的非易失性存储单元,其特征在于,当所述第一晶体管关断时,所述第一晶体管的泄露电流小于第一预设电流值。

3.根据权利要求1所述的非易失性存储单元,其特征在于,所述反相器包括第三晶体管以及第四晶体管,所述第三晶体管的第一端接入电源、所述第三晶体管的第二端与所述第四晶体管的第一端连接,其连接节点为所述反相器的第一端,所述第三晶体管以及所述第四晶体管的受控端连接,其连接节点为所述反相器的第二端;所述第四晶体管的第二端接地。

4.根据权利要求1所述的非易失性存储单元,其特征在于,所述非易失性存储单元还包括逻辑门,所述逻辑门设置于所述第二晶体管的第二端与所述信号输出端之间,所述逻辑门的第一端接入所述第二晶体管输出的所述存储信号,所述逻辑门的第二端接入特征信号;

5.根据权利要求1所述的非易失性存储单元,其特征在于,当所述第一过程控制信号为高电平,所述第二过程控制信号低电平时,所述非易失性存储单元处于写入状态,以写入所述存储信号;

6.根据权利要求1所述的非易失性存储单元,其特征在于,当所述第一过程控制信号为低电平,所述第二过程控制信号高电平时,所述非易失性存储单元处于写入状态,以写入所述存储信号;

7.一种计算存储单元,其特征在于,所述计算存储单元包括n个第一字线、n个第二字线、m个第一位线以及多个如权利要求1-6任一项所述的非易失性存储单元;多个所述非易失性存储单元组成n*m的存储矩阵,n以及m均大于或等于1;第n行的每一所述非易失性存储单元的第一晶体管的受控端均连接至第n个所述第一字线,第n行的每一所述非易失性存储单元的第二晶体管的受控端均连接至第n个所述第二字线;第m列所述非易失性存储单元的第一晶体管的第一端均连接至第m个所述第一位线;

8.根据权利要求7所述的计算存储单元,其特征在于,还包括移位加法器,每一所述存储单元的逻辑门的输出端均连接至所述移位加法器;

9.一种非易失性存储装置,其特征在于,所述非易失性存储装置包括权利要求1-6任一项所述的非易失性存储单元。

10.一种计算存储装置,其特征在于,所述计算存储装置包括权利要求7-8任一项所述的计算存储单元。

技术总结本发明实施例涉及存储器技术领域,公开了一种非易失性存储单元以及装置、计算存储单元以及装置,非易失性存储单元包括第一晶体管、第二晶体管、反相器、第一过程控制端、第二过程控制端、信号输入端以及信号输出端;其中,反相器在所述第一晶体管关断且所述第二晶体管导通时,将所述反相器所存储的所述存储信号反相输出,通过上述方案,可以减少存储单元中的晶体管的数量,从而减少单个非易失性存储单元的面积,进而减少SRAM存算阵列的面积占比。技术研发人员:黄明强,李子晔,胡万波,文婉婷受保护的技术使用者:深圳先进技术研究院技术研发日:技术公布日:2024/3/17本文地址:https://www.jishuxx.com/zhuanli/20240731/183840.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表