一种多模式硬件单元和可重构阵列电路

- 国知局

- 2024-07-31 19:55:48

本发明涉及计算机,具体来说涉及基于存内计算架构的计算机,更具体地说,涉及一种多模式硬件单元和可重构阵列电路。

背景技术:

1、传统的fpga架构如图1所示,其主要由可编程逻辑单元、互联单元和嵌入式随机存储器块(block ram,也可称嵌入式bram)组成。在使用fpga时,根据需要完成的功能,会将可编程逻辑单元编写为不同的输入输出映射,同时使用互联单元将可编程逻辑单元和设计在固定位置的嵌入式bram按照预想的方式连接起来,从而使整个fpga按照目标要求进行运行。

2、就目前已有的技术而言,可编程逻辑单元通常由查找表组成。查找表是用简单的查询操作替换运行时计算的硬件结构,一个n输入查找表可以预先存储2n个结果,通过不同的输入查询到不同的结果从而产生对应的输出。传统的fpga中的可编程逻辑单元通常由2个6输入查找表构成组成。

3、忆阻器作为一种新型器件,其阻值在两端输入特定的电压时将在高/低阻态间变化。且这种变化是非易失性的,即掉电和施加小电压等都不会对当前忆阻器的阻值产生影响。这就使得忆阻器拥有存储信息的能力(不同阻态代表不同信息)以及开关特性(高阻值阻止信号通过,低阻值允许信号通过)。

4、但是,发明人在进行fpga架构研究时,发现现有技术存在以下问题:

5、1.嵌入式bram在fpga中所占比例过低,在面对目前大量的数据密集型应用(如大型神经网络和推荐系统)时,嵌入式bram无法达到应用需要的缓存需求。如果加入外置存储器,则较长的读写延时(嵌入式bram读取延时约为外置存储器的十分之一)将显著降低应用性能。

6、2.路由开销过大。嵌入式bram的位置是固定的,获取嵌入式bram的数据时,需要使用过多的互联模块进行路由,这进一步增加了路由难度。

7、需要说明的是:本背景技术仅用于介绍本发明的相关信息,以便于帮助理解本发明的技术方案,但并不意味着相关信息必然是现有技术。相关信息与本发明方案一同提交和公开,在没有证据表明相关信息已在本发明的申请日以前公开的情况下,相关信息不应被视为现有技术。

技术实现思路

1、因此,本发明的目的在于克服上述现有技术的缺陷,提供一种多模式硬件单元和可重构阵列电路。

2、本发明的目的是通过以下技术方案实现的:

3、根据本发明的第一方面,提供一种多模式硬件单元,该多模式硬件单元用于构建可重构阵列电路或者处理器,所述多模式硬件单元能被配置为多种模式中的任意一种模式,且在被配置为一种模式后还能被重构配置为其他模式,其中,所述多种模式包括:第一模式,多模式硬件单元被配置为用于行使查找表功能的可编程逻辑单元;第二模式,多模式硬件单元被配置为用于行使路由功能的互联单元;以及第三模式,多模式硬件单元被配置为用于行使块内存功能的嵌入式bram。本发明的技术方案至少能够实现以下有益技术效果:针对第一个问题,上述可重构阵列电路中的每个多模式硬件单元都可以配置为嵌入式bram,因此完美解决了现有技术中嵌入式bram占比过低的问题;针对第二个问题,上述可重构阵列电路中每个多模式硬件单元都可以配置为可编程逻辑单元;且相邻单元可使用直接相连的方式,只有跨单元连接才需要将连线上的单元配置为互联单元。本发明阵列中每个单元都可以配置为嵌入式bram,不再受现有技术中嵌入式bram位置固定的限制,而且本发明很好地解决了现有技术中存在的路由开销过大的问题。

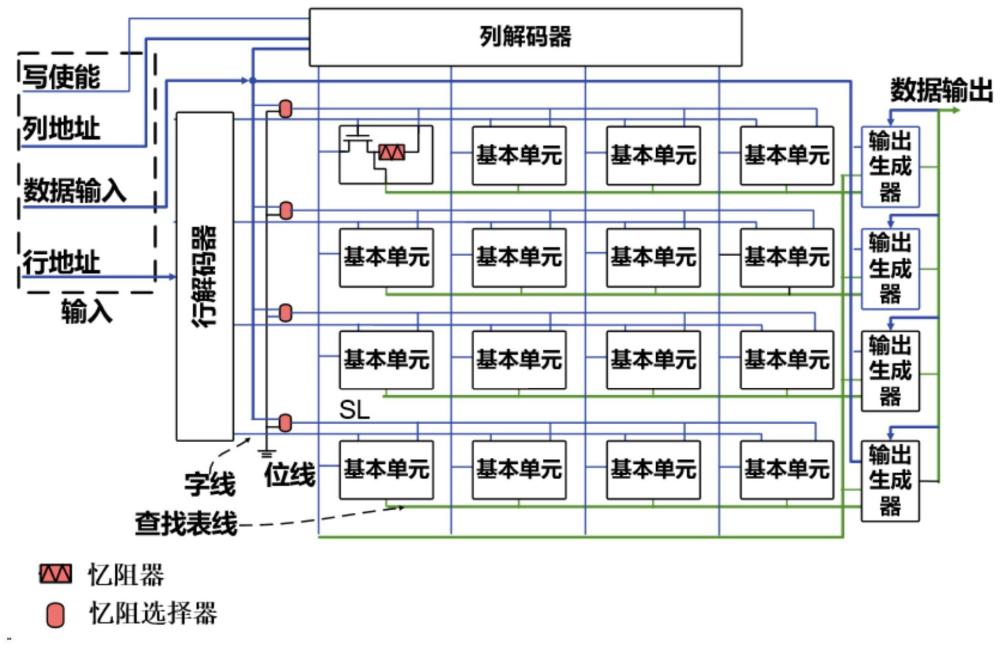

4、可选的,所述多模式硬件单元包括:由多个基本单元组成的功能阵列,所述基本单元为包括一个晶体管和一个忆阻器的1t1r单元;与多个所述基本单元分别连接的行解码器和列解码器;与多个所述基本单元分别连接的多个输出生成器;其中,在第一模式下,所述功能阵列中的每一行的基本单元构成一个查找表,通过所述功能阵列和输出生成器的配合,执行查找表功能;在第二模式下,所述功能阵列中的每一行的基本单元存储路由信息,通过所述功能阵列和输出生成器的配合,执行路由功能,将输入数据按路由信息路由到对应的输出生成器,不同的输出生成器用于连接不同的邻居多模式硬件单元;在第三模式下,所述功能阵列中的每一行的基本单元存储数据,通过所述行解码器、列解码器和输出生成器的配合,执行对所述功能阵列中所需访问的行和列对应基本单元的数据读/写操作。

5、可选的,所述功能阵列为n*n个基本单元构成的阵列,且含有n条字线、n条位线、n条感应线和n*n条查找表线,n≥32,且n取2的幂次;其中,每行基本单元中的晶体管的栅极连接同一条字线;每行基本单元中的晶体管的源极连接同一基本单元中的忆阻器的一端和一条查找表线,同行基本单元中的忆阻器的另一端连接同一条感应线,且每条感应线通过忆阻选择器分别连接本多模式硬件单元的数据输入的一位和地线;每列基本单元中的晶体管的漏极连接同一条位线。

6、可选的,每个多模式硬件单元包括n个输出生成器,其中,功能阵列中第i行的所有的查找表线都与第i个输出生成器相连;功能阵列中第i条位线与第i个输出生成器相连,0<i<n+1;本多模式硬件单元的数据输入和/或数据输出作为输入反馈连接到每个输出生成器;每个输出生成器的输出连接数据输出中的1位;每个输出生成器根据本多模式硬件单元的数据输入和数据输出以及当前多模式硬件单元的模式,从n条查找表线和1条位线中选择对应的输入到输出生成器中,产生数据输出。

7、可选的,处于第一模式的多模式硬件单元中,被配置为:基本单元的忆阻器的另一端通过感应线接地;由输出生成器产生参考电压,将参考电压施加至由数据输入和/或数据输出决定的查找表线和忆阻器以产生参考电流,施加参考电压后,由输出生成器识别预设时长后的电压降以确定查找的结果。

8、可选的,处于第二模式的多模式硬件单元中,被配置为:当数据输入的第i位需路由连接至数据输出的第j位,则第i行第j列的基本单元的忆阻器被置于低阻态,第j列其余忆阻器被置于高阻态,以此实现存储路由地址;各字线置高以使得基本单元中的晶体管处于导通的状态;基本单元的忆阻器的另一端通过感应线连接数据输入,再通过基本单元的忆阻器和晶体管,连接到对应列的位线上;由任一行的输出生成器直接接收来自感应线的电压,确定路由到当前输出生成器的数据。

9、可选的,处于第三模式的多模式硬件单元中,在读操作时,被配置为:将各基本单元的忆阻器的另一端通过感应线接地;行解码器使得输入行地址对应行的字线置高,其余字线置低,使得对应行基本单元内的晶体管导通;输出生成器接受位线作为输入;由输出生成器产生参考电压,将参考电压通过对应位线施加至晶体管和忆阻器;施加参考电压后,由输出生成器识别预设时长后的电压降以获取读取的值。

10、可选的,处于第三模式的多模式硬件单元中,在写操作时,被配置为:将各基本单元的忆阻器的另一端通过感应线接地;行解码器使得输入行地址对应行的字线置高,列解码器使得输入列地址对应列的位线置为输入数据需要的高/低写入电压,其余字线和位线接地,使得选中行的基本单元的晶体管导通且忆阻器两端加上能写入高/低阻态的电压脉冲,实现写入功能。

11、根据本发明的第二方面,提供一种可重构阵列电路,其包括多个如第一方面所述的多模式硬件单元,多个所述多模硬件单元构成m×m的阵列。

12、根据本发明的第三方面,提供一种可重构阵列电路,其包括多个如第一方面所述的多模式硬件单元,其中,所述可重构阵列电路的用途包括:根据任务的需求,将多模式硬件单元中的相应单元分别配置为第一模式、第二模式和第三模式;根据所述任务执行的流程,建立处于第一模式、第二模式或第三模式的相关单元间的连接,以利用所述可重构阵列电路构建用于处理所述任务的处理器;和/或获取所述任务,利用所述处理器完成任务的处理。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184739.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表