命令处理方法和装置与流程

- 国知局

- 2024-07-31 19:56:21

本技术实施例涉及计算机,尤其涉及命令处理方法和装置。

背景技术:

1、随机存储器是电子设备的重要部件,随机存储器用于暂时存放电子设备的处理器中的运算数据,以及与电子设备的外部存储器交换的数据。电子设备在运行应用程序时,需要将待运算的数据从随机存储器调到处理器中进行运算,当运算完成,处理器将运算结果传送出来。

2、随着电子的发展,随机存储器的容量越来越大,功耗也随之增加。为降低机存储器的功耗,可以在随机存储器空闲时使随机存储器进入低功耗状态以降低随机存储器的功耗。

3、然而,随机存储器处于低功耗状态时,访问随机存储器的命令在到达内存控制器后,需要先等待较长时间,等随机存储器退出低功耗状态后,才能正常访问随机存储器,访问时延较高。

技术实现思路

1、本技术实施例提供了命令处理方法和装置,能够降低处于低功耗状态下的随机存储器的访问时延。为达到上述目的,本技术实施例采用如下技术方案:

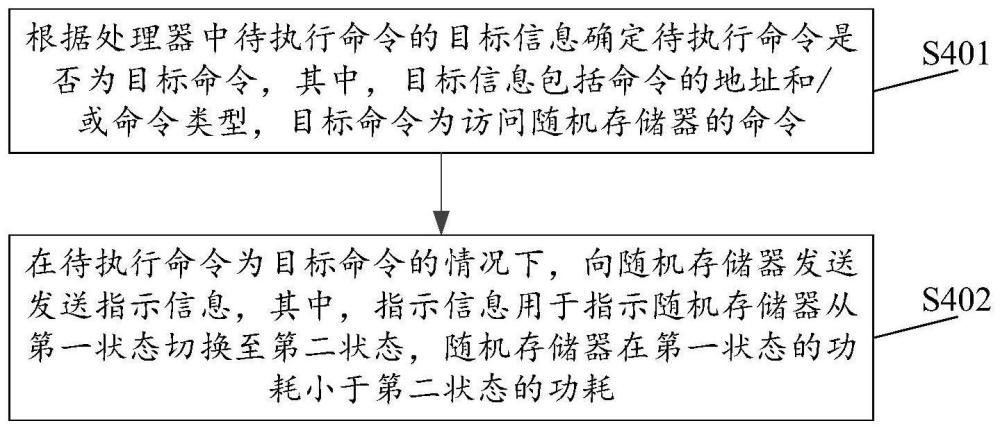

2、第一方面,本技术实施例了一种命令处理方法,应用于电子设备,所述电子设备包括处理器和随机存储器,该方法包括:首先根据所述处理器中待执行命令的目标信息确定所述待执行命令是否为目标命令,然后在所述待执行命令为目标命令的情况下,向所述随机存储器发送指示信息,所述指示信息用于指示所述随机存储器从第一状态切换至第二状态。其中,所述目标信息包括地址和/或命令类型。所述目标命令为访问所述随机存储器的命令。所述随机存储器在第一状态的功耗小于所述第二状态的功耗。

3、相关技术中,处于低功耗状态下的随机存储器在收到处理器下发的命令后,需要等待一段时间(如14纳秒左右)从低功耗状态切换至正常状态,然后才能执行处理器下发的命令,访问时延较高。而本技术实施例提供命令处理方法可以根据处理器中待执行命令的地址确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,提前向随机存储器发送指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

4、在一种可能的实现方式中,可以获取处理器命令历史表。然后在所述处理器命令历史表中所述待执行命令的地址对应访问随机存储器的情况下,确定所述待执行命令是目标命令;在所述处理器命令历史表中所述待执行命令的地址对应访问随机存储器的情况下,确定所述待执行命令是目标命令。其中,所述处理器命令历史表用于记录命令的地址与是否访问随机存储器之间的对应关系。

5、可以看出,本技术实施例提供的命令处理方法,可以根据处理器中待执行命令的地址查询处理器命令历史表确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,提前向随机存储器发送指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

6、在另一种可能的实现方式中,可以获取概率信息。然后在所述访问概率大于第一阈值的情况下,确定所述待执行命令是目标命令;在所述访问概率小于第二阈值的情况下,确定所述待执行命令不是目标命令。其中,所述概率信息用于指述所述待执行命令的同地址命令访问随机存储器的访问概率,所述同地址命令是地址与所述待执行命令的地址相同的命令,所述第一阈值大于或等于所述第二阈值。

7、可以看出,本技术实施例提供的命令处理方法,可以根据处理器中待执行命令的地址查询与该命令相同地址的命令访问随机存储器的访问概率,然后根据访问概率确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,提前向随机存储器发送指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

8、在又一种可能的实现方式中,可以根据所述待执行命令的命令类型确定所述待执行命令是否为目标类型命令。在所述待执行命令是目标类型命令的情况下,确定所述待执行命令是目标命令;在所述待执行命令不是目标类型命令的情况下,确定所述待执行命令不是目标命令。其中,所述目标类型命令包括预取(prefetch)三级缓存(l3)命令和/或预取prefetch末级缓存(last level cache,llc)命令。

9、可以看出,本技术实施例提供的命令处理方法,可以根据处理器中待执行命令的命令类型确定待执行命令不是目标类型命令,然后根据待执行命令是否为目标类型命令确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,提前向随机存储器发送指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

10、在一种可能的实现方式中,处理器与所述随机存储器通过总线连接。

11、在一种可能的实现方式中,可以控制所述处理器通过所述总线向所述随机存储器发送所述指示信息。

12、可以看出,本技术实施例提供命令处理方法可以根据处理器中待执行命令的地址确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,可以控制所述处理器通过所述总线向所述随机存储器发送所述指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

13、在另一种可能的实现方式中,可以控制所述处理器通过直连通道向所述随机存储器发送所述指示信息。其中,所述直连通道为所述处理器与所述随机存储器之间的直连通道。

14、可以看出,本技术实施例提供命令处理方法可以根据处理器中待执行命令的地址确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,可以控制所述处理器通过处理器与所述随机存储器之间的直连通道向所述随机存储器发送所述指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。且相较于通过总线向随机存储器发送指示信息,通过处理器与所述随机存储器之间的直连通道可以降低传输时延。

15、可选地,上述直连通道可以是连接处理器与随机存储器的高层金属线。

16、在一种可能的实现方式中,该方法还可以包括:控制所述处理器向所述随机存储器发送所述待执行命令。

17、本技术实施例提供命令处理方法可以根据处理器中待执行命令的地址确定待执行命令是否访问随机存储器,在待执行命令访问随机存储器的情况下,提前向随机存储器发送指示信息使随机存储器从低功耗状态(即第一状态)切换至正常状态(即第二状态),之后控制所述处理器向所述随机存储器发送所述待执行命令。从而能使随机存储器在后续接收到处理器下发的命令时,无需退出低功耗状态,而是直接执行处理器下发的命令,或少量等待退出低功耗状态的时间后执行处理器下发的命令,从而降低访问时延。

18、可选地,上述第一状态可以为掉电(power down)状态、自刷新(sref refresh)状态、自刷新掉电(sref refresh power down)状态、深度睡眠模式(deep sleep mode)或其他低功耗状态。

19、第二方面,本技术实施例提供了另一种命令处理方法,应用于电子设备,所述电子设备包括处理器和随机存储器,该方法包括:处理器根据待执行命令的目标信息确定待执行命令是否为目标命令。处理器在待执行命令为目标命令的情况下,向随机存储器发送指示信息。

20、在一种可能的实现方式中,处理器可以先获取处理器命令历史表。然后在上述处理器命令历史表中上述待执行命令的地址对应访问随机存储器的情况下,确定上述待执行命令是目标命令;在上述处理器命令历史表中上述待执行命令的地址对应访问随机存储器的情况下,确定上述待执行命令是目标命令。

21、在另一种可能的实现方式中,处理器可以获取概率信息。然后在上述访问概率大于第一阈值的情况下,确定上述待执行命令是目标命令;在上述访问概率小于第二阈值的情况下,确定上述待执行命令不是目标命令,上述第一阈值大于或等于上述第二阈值。

22、在一种可能的实现方式中,上述第一状态可以为掉电状态、自刷新状态、自刷新掉电状态、深度睡眠模式或其他低功耗状态。

23、在一种可能的实现方式中,上述指示信息可以包括快速唤醒信号和/或中断信号。

24、在一种可能的实现方式中,处理器可以通过上述总线向上述随机存储器发送上述指示信息。

25、在另一种可能的实现方式中,处理器可以通过直连通道向上述随机存储器发送上述指示信息。其中,所述直连通道为所述处理器与所述随机存储器之间的直连通道。

26、在又一种可能的实现方式中,处理器可以根据上述待执行命令的命令类型确定上述待执行命令是否为目标类型命令。在上述待执行命令是目标类型命令的情况下,确定上述待执行命令是目标命令;在上述待执行命令不是目标类型命令的情况下,确定上述待执行命令不是目标命令。其中,上述目标类型命令包括prefetch l3命令和/或prefetch llc命令。

27、第三方面,本技术实施例了一种命令处理装置,该命令处理装置包括:收发单元和确定单元。所述确定单元,用于根据所述处理器中待执行命令的目标信息确定所述待执行命令是否为目标命令,所述目标信息包括地址和/或命令类型,所述目标命令为访问随机存储器的命令。所述收发单元,用于在所述待执行命令为目标命令的情况下,向所述随机存储器发送指示信息,所述指示信息用于指示所述随机存储器从第一状态切换至第二状态,所述随机存储器在第一状态的功耗小于所述第二状态的功耗。

28、在一种可能的实现方式中,所述确定单元具体用于:获取处理器命令历史表,所述处理器命令历史表用于记录命令的地址与是否访问随机存储器之间的对应关系。在所述处理器命令历史表中所述待执行命令的地址对应访问随机存储器的情况下,确定所述待执行命令是目标命令。在所述处理器命令历史表中所述待执行命令的地址对应不访问随机存储器的情况下,确定所述待执行命令不是目标命令。

29、在另一种可能的实现方式中,所述确定单元具体用于:获取概率信息,所述概率信息用于指述所述待执行命令的同地址命令访问随机存储器的访问概率,所述同地址命令是地址与所述待执行命令的地址相同的命令。在所述访问概率大于第一阈值的情况下,确定所述待执行命令是目标命令。在所述访问概率小于第二阈值的情况下,确定所述待执行命令不是目标命令,上述第一阈值大于或等于上述第二阈值。

30、在又一种可能的实现方式中,所述确定单元具体用于:根据所述待执行命令的命令类型确定所述待执行命令是否为目标类型命令,所述目标类型命令包括prefetch l3命令和/或prefetch llc命令;在所述待执行命令是目标类型命令的情况下,确定所述待执行命令是目标命令;在所述待执行命令不是目标类型命令的情况下,确定所述待执行命令不是目标命令。

31、在一种可能的实现方式中,处理器与所述随机存储器通过总线连接。

32、在一种可能的实现方式中,所述收发单元具体用于:控制所述处理器通过直连通道向所述随机存储器发送所述指示信息,所述直连通道为所述处理器与所述随机存储器之间的直连通道。

33、在另一种可能的实现方式中,所述收发单元具体用于:控制所述处理器通过所述总线向所述随机存储器发送所述指示信息。

34、可选地,可选地,上述第一状态可以为掉电(power down)状态、自刷新(sref refresh)状态、自刷新掉电(sref refresh power down)状态、深度睡眠模式(deep sleep mode)或其他低功耗状态。

35、第四方面,本技术实施例还提供了一种电子设备,所述电子设备包括处理器和随机存储器。所述处理器,用于根据待执行命令的目标信息确定所述待执行命令是否为目标命令。在所述待执行命令为目标命令的情况下,向所述随机存储器发送指示信息。其中,所述目标信息包括地址和/或命令类型,所述目标命令为访问随机存储器的命令。所述指示信息用于指示所述随机存储器从第一状态切换至第二状态,所述随机存储器在第一状态的功耗小于所述第二状态的功耗。

36、在一种可能的实现方式中所述处理器具体用于:获取处理器命令历史表,所述处理器命令历史表用于记录命令的地址与是否访问随机存储器之间的对应关系。在所述处理器命令历史表中所述待执行命令的地址对应访问随机存储器的情况下,确定所述待执行命令是目标命令。在所述处理器命令历史表中所述待执行命令的地址对应不访问随机存储器的情况下,确定所述待执行命令不是目标命令。

37、在一种可能的实现方式中所述处理器具体用于:获取概率信息,所述概率信息用于指述所述待执行命令的同地址命令访问随机存储器的访问概率,所述同地址命令是地址与所述待执行命令的地址相同的命令。在所述访问概率大于第一阈值的情况下,确定所述待执行命令是目标命令。在所述访问概率小于第二阈值的情况下,确定所述待执行命令不是目标命令,所述第一阈值大于或等于所述第二阈值。

38、在一种可能的实现方式中所述处理器具体用于:根据所述待执行命令的命令类型确定所述待执行命令是否为目标类型命令,所述目标类型命令包括预取三级缓存命令和/或预取末级缓存命令;在所述待执行命令是目标类型命令的情况下,确定所述待执行命令是目标命令;在所述待执行命令不是目标类型命令的情况下,确定所述待执行命令不是目标命令。

39、第五方面,本技术实施例还提供一种命令处理装置,该命令处理装置包括:至少一个处理器,当所述至少一个处理器执行程序代码或指令时,实现上述第一方面或其任意可能的实现方式中所述的方法。

40、可选地,该命令处理装置还可以包括至少一个存储器,该至少一个存储器用于存储该程序代码或指令。

41、第六方面,本技术实施例还提供一种芯片,包括:输入接口、输出接口、至少一个处理器。可选地,该芯片还包括存储器。该至少一个处理器用于执行该存储器中的代码,当该至少一个处理器执行该代码时,该芯片实现上述第一方面或其任意可能的实现方式中所述的方法。

42、可选地,上述芯片还可以为集成电路。

43、第七方面,本技术实施例还提供一种计算机可读存储介质,用于存储计算机程序,该计算机程序包括用于实现上述第一方面或其任意可能的实现方式中所述的方法。

44、第八方面,本技术实施例还提供一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机实现上述第一方面或其任意可能的实现方式中所述的方法。

45、本实施例提供的命令处理装置、计算机存储介质、计算机程序产品和芯片均用于执行上文所提供的方法,因此,其所能达到的有益效果可参考上文所提供的方法中的有益效果,此处不再赘述。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184756.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。