具有T+FLY-BY拓扑结构的电路的制作方法

- 国知局

- 2024-07-31 20:00:07

本技术涉及存储,尤其涉及一种具有t+fly-by拓扑结构的电路。

背景技术:

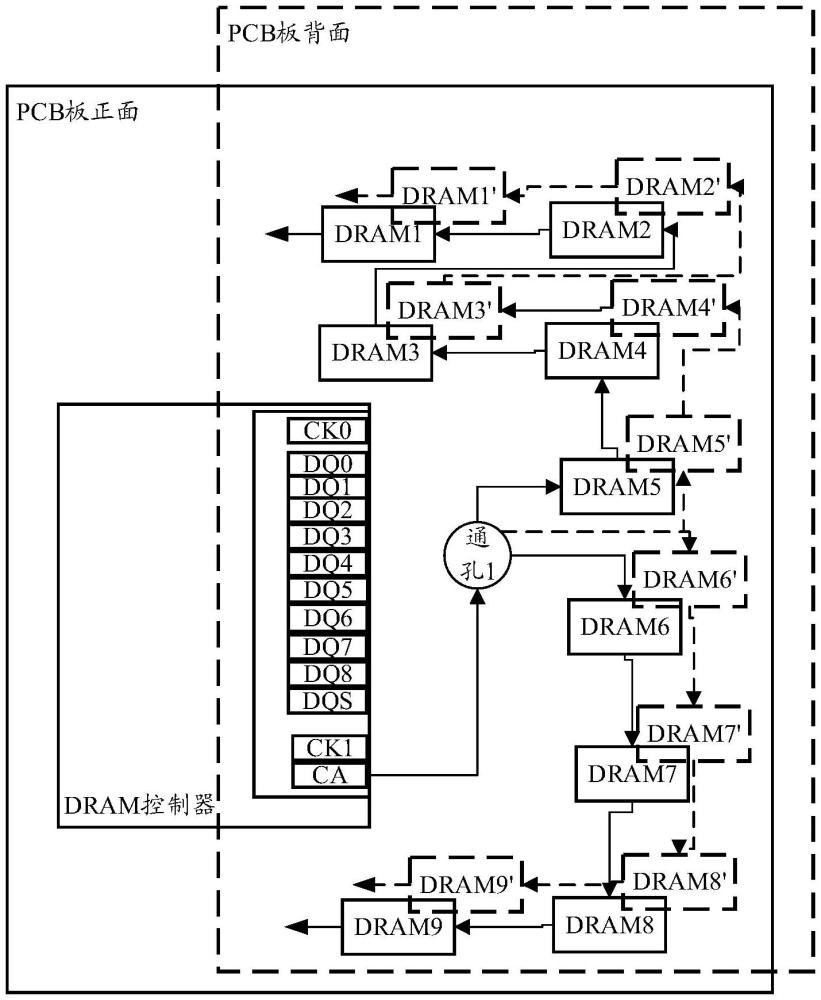

1、随着对电子设备性能要求的提升,需要dram控制器耦合更多的dram颗粒,例如,dram控制器耦合18颗dram颗粒;dram控制器与dram颗粒之间传输的信号组包括ca(command/address,命令/地址信号)、ck(时钟信号)、dq(数据信号)、dqs(数据选通信号)。18颗dram被布局到pcb(printed circuit board,印制电路板)的两个表面上(正、背两面),每一面布局9颗dram。例如,正面布局了dram1~dram9(9颗dram),背面布局了dram1'~dram9'(9颗dram)。参见图1所示,为在pcb板的两个表面布局多颗dram的示意图,虚线表示在pcb板的背面布局dram。

2、18颗dram可以分为2组,例如正面的9颗dram作为一组,将背面的9颗dram作为另一组;或者将正面5颗dram和背面4颗dram作为一组,将正面4颗dram和反面5颗dram作为另一组。每组dram对应一个ck信号,如dram控制器包括两个ck信号端口,ck0和ck1,用于分别为两组dram提供ck信号。两组dram共享dq、ca、dqs信号,例如,dram控制器包括一个ca端口和一个dqs端口,通过ca端口来为两组dram提供ca信号,通过dqs端口来为两组dram提供dqs信号;dq端口数量与每一组所支持的dram颗粒的数量相同,例如dram控制器包括dq0、dq1、dq2、dq3、dq4、dq5、dq6、dq7以及dq8这九个dq端口来分别为每组9颗dram提供dq信号。参见图2a和图2b所示,pcb板正面的9颗dram作为一组、pcb板背面的9颗dram作为另一组,dram控制器部署于pcb板的正面,正面的一组对应于ck0信号,背面的一组对应于ck1信号,两组dram共享dq、ca、dqs信号。

3、pcb板有多层,在pcb板上双面布局多颗dram,正面和背面布局的dram颗粒之间是一一对应的(一对一相对设置),正面、背面相对设置的dram颗粒之间相同的管脚之间可通过通孔来连接,通孔贯穿pcb板从正面到反面的多层,使得正面布局的dram控制器各端口的信号能通过通孔传输给正面布局的dram颗粒,也可以传输给背面布局的dram颗粒,例如,正面dram颗粒上的dq、ca或dqs信号通过通孔传输到与其对应的反面dram颗粒上。例如,dram1颗粒的dq管脚收到dq信号,通过与dram1颗粒的dq管脚耦合的通孔将dram1颗粒收到的dq信号传输给dram1'颗粒的dq管脚。

4、目前,向dram颗粒传输ca和ck信号时,走线通常采用fly-by拓扑结构或者t型结构,传输dq和dqs信号走线通常采用点对点的方式。如图3a所示,为传输ca和ck信号的信号走线采用fly-by拓扑结构、传输dq和dqs信号的信号走线采用点对点方式的一具体示意;参见图3b所示,为传输ca信号的信号走线采用fly-by拓扑结构的另一示意。

5、在fly-by拓扑结构中,例如ca信号线采用单一走线形式依次延伸到各个dram颗粒附近,通过短连接线将ca信号线与各dram颗粒的ca端口连接。为了提高信号质量,在ca信号线末端还设置端接电阻vtt,以进行容性负载补偿。

技术实现思路

1、dram控制器在向dram颗粒传输ca、ck、dq或dqs等信号时,要求ck和dqs之间的时间偏差不能超过指定阈值(例如,1个时钟周期)。当每组dram中多颗dram(如9颗)采用fly-by拓扑结构来传输ca/ck信号时,由于每组dram所包含dram颗粒数目较多,受电路板上其他部件的影响、要放置的dram颗粒数量的影响、dram控制器上访问dram颗粒的端口所处位置的影响等,ca和ck信号线采用fly-by拓扑结构,使得ca和ck信号线的形状会受到影响。为了满足fly-by拓扑结构的布线要求,可能会导致ca和ck信号线过长,由于传输ca和ck信号需要的时间与ca和ck信号线长度成正比,过长的连线会使得ck和dqs之间的时间偏差超过指定阈值,无法满足时序要求。本技术希望提供方案来解决上述技术问题。

2、本实用新型实施例提供一种具有t+fly-by拓扑结构的电路,包括:设置于pcb板上的dram控制器、第一组dram以及第一分支点;

3、所述第一组dram包括多个dram颗粒;

4、所述dram控制器的ca端口通过信号线与所述第一分支点连接,所述第一分支点通过信号线与所述第一组dram中第一dram颗粒和/或第二dram颗粒连接;

5、布设于所述第一dram颗粒以及至少一个第三dram颗粒之间的用于传递ca信号的信号线采用fly-by拓扑结构,以及布设于所述第二dram颗粒到至少一个第四dram颗粒之间的用于传递ca信号的信号线采用fly-by拓扑结构;

6、其中,所述第一dram颗粒、所述第二dram颗粒、所述至少一个第三dram颗粒以及所述至少一个第四dram颗粒为所述第一组dram中不同dram颗粒,其共同组成所述第一组dram。

7、可选地,所述具有t+fly-by拓扑结构的电路还包括:第二分支点;

8、所述dram控制器的第一ck端口通过信号线与所述第二分支点连接,所述第二分支点通过信号线与所述第一组dram中第一dram颗粒和/或第二dram颗粒连接;

9、布设于所述第一dram颗粒以及所述至少一个第三dram颗粒之间的用于传递ck信号的信号线采用fly-by拓扑结构,以及布设于所述第二dram颗粒到所述至少一个第四dram颗粒之间的用于传递ck信号的信号线采用fly-by拓扑结构。

10、可选地,所述第一dram颗粒到所述至少一个第三dram颗粒之间布设的信号线长度与所述第二dram颗粒到所述至少一个第四dram颗粒之间布设的信号线长度的差值在第一预设范围内。

11、可选地,所述第一分支点或所述第二分支点与所述第一dram颗粒和所述第二dram颗粒上对应管脚之间连接的信号线长度在第二预设范围内。

12、可选地,所述第一组dram中位置相邻的两个dram颗粒之间的信号线长度在预设第三范围内。

13、可选地,所述第一分支点和所述第二分支点为设置于所述pcb板上的通孔。

14、可选地,所述第一分支点和/或所述第二分支点均为所述pcb板上设置的用作于实现分支点功能的专用通孔;或者,所述第一分支点为所述pcb板上dram颗粒的ca管脚对应的通孔,所述第二分支点为所述第一组dram中dram颗粒的ck管脚对应的通孔。

15、可选地,所述第一分支点和/或所述第二分支点为所述专用通孔,所述第一分支点和/或所述第二分支点通过信号线与所述第一dram颗粒和所述第二dram颗粒连接。

16、可选地,所述第一dram颗粒的ca管脚对应的通孔作为所述第一分支点,所述第一分支点通过信号线与所述第二dram颗粒对应的管脚连接;或

17、所述第二dram颗粒的ca管脚对应的通孔作为所述第一分支点,所述第一分支点通过信号线与所述第一dram颗粒对应的管脚连接。

18、可选地,所述第一dram颗粒的ck管脚对应的通孔作为所述第二分支点,所述第二分支点通过信号线与所述第二dram颗粒对应的管脚连接;或

19、所述第二dram颗粒的ck管脚对应的通孔作为所述第二分支点,所述第二分支点通过信号线与所述第一dram颗粒对应的管脚连接。

20、可选地,所述dram控制器的ca端口通过信号线与所述第一dram颗粒或所述第二dram颗粒的ca端口连接;

21、所述dram控制器的第一ck端口通过信号线与所述第一dram颗粒或所述第二dram颗粒的ck端口连接。

22、可选地,所述dram控制器的ca端口与所述第一分支点通过信号线连接,所述第一分支点通过信号线与所述第一dram颗粒和/或所述第二dram颗粒的ca端口连接;

23、所述dram控制器的第一ck端口与所述第二分支点通过信号线连接,所述第二分支点通过信号线与所述第一dram颗粒和/或所述第二dram颗粒的ck端口连接。

24、可选地,所述具有t+fly-by拓扑结构的电路还包括:第二组dram;

25、所述dram控制器的ca端口通过信号线与所述第一分支点连接,所述第一分支点通过信号线与所述第二组dram中第五dram颗粒和/或第六dram颗粒连接;

26、布设于所述第五dram颗粒以及至少一个第七dram颗粒之间的用于传递ca信号的信号线采用fly-by拓扑结构,以及布设于所述第六dram颗粒到至少一个第八dram颗粒之间的用于传递ca信号的信号线采用fly-by拓扑结构;

27、其中,所述第五dram颗粒、所述第六dram颗粒、所述至少一个第七dram颗粒以及所述至少一个第八dram颗粒为所述第二组dram中不同dram颗粒,其共同组成所述第二组dram。

28、可选地,所述第一分支点为专用通孔,所述第一分支点通过信号线分别与所述第五dram颗粒和第六dram颗粒的ca管脚连接。

29、可选地,在所述第一dram颗粒的ca管脚对应的通孔作为所述第一分支点情况下,所述第五dram颗粒或所述第六dram颗粒的ca管脚与所述第一dram颗粒的ca管脚通过所述第一dram颗粒的ca管脚对应的通孔连接,ca信号通过所述第一dram颗粒的ca管脚的通孔传递到所述第五dram颗粒或所述第六dram颗粒的ca管脚。

30、可选地,所述具有t+fly-by拓扑结构的电路还包括第三分支点以及所述dram控制器还包括第二ck端口;

31、所述dram控制器的第二ck端口通过信号线与所述第三分支点连接,所述第三分支点通过信号线与所述第二组dram中第五dram颗粒和/或第六dram颗粒连接;

32、布设于所述第五dram颗粒以及至少一个第七dram颗粒之间的用于传递ck信号的信号线采用fly-by拓扑结构,以及布设于所述第六dram颗粒到至少一个第八dram颗粒之间的用于传递ck信号的信号线采用fly-by拓扑结构。

33、可选地,所述第二ck端口与所述第一ck端口为所述dram控制器上不同的ck端口;

34、所述第一分支点、所述第二分支点以及所述第三分支点为不同分支点。

35、可选地,所述第三分支点为设置于所述pcb板上与所述第一分支点以及所述第二分支点不同的专用通孔;或者,所述第三分支点为所述第二组dram中dram颗粒的ck管脚对应的通孔。

36、可选地,所述第三分支点为专用通孔,所述第三分支点通过信号线分别与所述第五dram颗粒和所述第六dram颗粒的ck管脚连接。

37、可选地,在所述第五dram颗粒的ck管脚对应的通孔作为所述第三分支点情况下,所述dram控制器的第二ck端口通过信号线与所述第五dram颗粒的ck管脚连接;

38、所述六dram颗粒的ck管脚通过信号线与所述第五dram颗粒的ck管脚对应的通孔连接,ck信号通过所述第五dram颗粒的ck管脚的通孔传递到所述第六dram颗粒的ck管脚。

39、可选地,在所述第三分支点为所述第六dram颗粒的ck管脚对应的通孔情况下,所述dram控制器的第二ck端口通过信号线与所述第六dram颗粒的ck管脚连接;

40、所述第五dram颗粒的ck管脚通过信号线与所述第六dram颗粒的ck管脚对应的通孔连接,ck信号通过所述第六dram颗粒的ck管脚的通孔传递到所述第五dram颗粒的ck管脚。

41、可选地,所述第一组dram和所述第二组dram位于所述pcb板上不同端面,或者所述第一组dram和所述第二组dram均包括来自于布设于所述pcb板上两个端面的dram颗粒。

42、可选地,在所述第一组dram和所述第二组dram均包括来自于布设于所述pcb板上两个端面的dram颗粒,且所述第一分支点为所述第一dram颗粒的ca管脚对应的通孔,所述第五dram颗粒或所述第六dram颗粒的ca管脚通过信号线与所述第一dram颗粒的ca管脚对应的通孔连接,以及所述第二dram颗粒的ca管脚通过信号线与所述第一dram颗粒的ca管脚的通孔连接;

43、ca信号通过所述第一dram颗粒的ca管脚的通孔传输给所述第二dram颗粒的ca管脚以及传输给所述第五dram颗粒的ca管脚或第六dram颗粒的ca管脚。

44、可选地,若ca信号通过所述第一dram颗粒对应的ca管脚的通孔传输给所述第五dram颗粒的ca管脚,所述第六dram颗粒的ca管脚通过信号线与所述第五dram颗粒的ca管脚的通孔连接,ca信号通过所述第五dram颗粒的ca管脚传输给所述第六dram颗粒的ca管脚。

45、可选地,若ca信号通过所述第一dram颗粒对应的ca管脚的通孔传输给所述第六dram颗粒的ca管脚,所述第五dram颗粒的ca管脚通过信号线与所述第六dram颗粒的ca管脚的通孔连接,ca信号通过所述第六dram颗粒的ca管脚传输给所述第五dram颗粒的ca管脚。

46、根据本实用新型的实施例,通过采用分支点对dram组内的dram颗粒进行划分,所划分的每部分dram对应的多颗dram采用fly-by拓扑结构传输ca或ck信号,dram组内的各部分dram之间并行的通过各自对应的fly-by拓扑结构传输ca或ck信号,实现减少组内dram颗粒之间传输ca或ck信号所需的时间,保证ca或ck信号的传输满足时序要求。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184963.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表