关于低频电子标签存储器eeprom的控制方法与流程

- 国知局

- 2024-07-31 20:00:40

本发明涉及无源低频电子标签存储,尤其是涉及关于低频电子标签存储器eeprom的控制方法。

背景技术:

1、随着微电子技术的发展与物联网技术的兴起,作为物品重要感知手段的rfid技术日益受到人们的关注。电子标签是一种非接触式的射频识别技术,通过电磁波目前,rfid电子标签正在越来越多地用在格类物品上,更广泛的应用也对标签信息的读写效率存储性能及安全稳定性提出了更高的要求。

2、现有的技术中,目前主流的总线为高级高性能总线ahb(advanced highperformance bus),主要用于高性能模块(如cpu、dma和dsp等)之间的连接。ahb系统由主模块、从模块和基础结构(infrastructure)三部分组成,整个ahb总线上的传输都由主模块发出,由从模块负责回应。

3、eeprom(electrically erasable programmable read-only memory)是一种掉电后数据不丢失的带电可擦可编程存储器,其编程操作需要高压信号;此外,根据不同的工艺参数要求,操作遵循严格的时序要求。一般soc上对于eeprom的操作采用ahb总线。

4、上述中的现有技术方案存在以下缺陷:一般的soc系统有稳定的电源,可以快速满足操作时所需的高压,对于eeprom的操作,只需要满足工艺所要求的的setup和hold时序即可。无源电子标签接收电磁信号为设备供电,当对eeprom进行操作时,需要一定的时间调整电压信号,因此操作时间较长,为满足eeprom的操作要求并符合通信格式,需对eeprom的控制进行特殊处理。

5、此外通用的ahb总线架构,对于基于iso 11784/11785标准的无源电子标签并不适用,操作效率及性能都较差。

技术实现思路

1、针对现有技术存在的不足,本发明的目的是提供关于低频电子标签存储器eeprom的控制方法,其对于基于iso 11784/11785标准的无源电子标签,显著提高了操作效率,提升了性能,且可以保证存储数据的正确性。

2、本发明的上述发明目的是通过以下技术方案得以实现的:

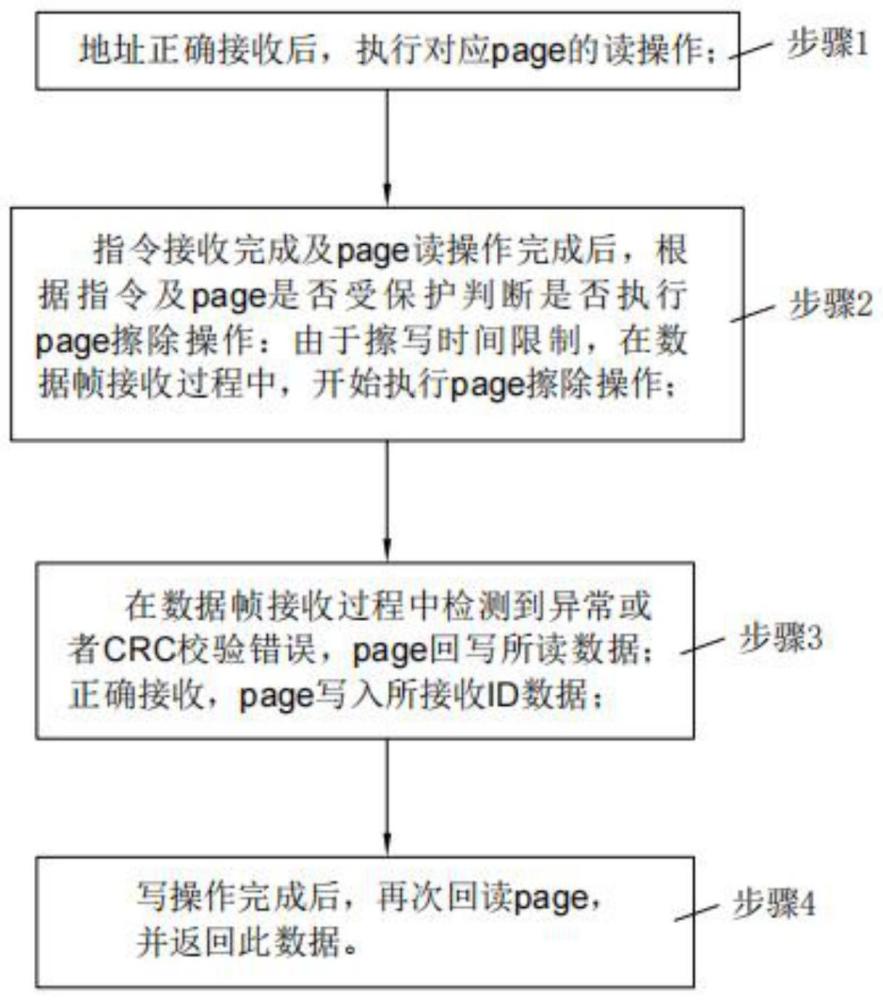

3、关于低频电子标签存储器eeprom的控制方法,包括以下步骤:

4、步骤1、地址正确接收后,执行对应page的读操作;

5、步骤2、指令接收完成及page读操作完成后,根据指令及page是否受保护判断是否执行page擦除操作:

6、由于擦写时间限制,在数据帧接收过程中,开始执行page擦除操作;

7、步骤3、在数据帧接收过程中检测到异常或者crc校验错误,page回写所读数据;

8、正确接收,page写入所接收id数据;

9、步骤4、写操作完成后,再次回读page,并返回此数据。

10、作为本发明的进一步的技术方案:为满足协议要求及eeprom控制器的工艺要求,对于eeprom的擦除操作在接收过程中执行。

11、作为本发明的进一步的技术方案:接收完成或受环境干扰中断中断时,根据记录状态,执行对应的写操作。

12、作为本发明的进一步的技术方案:基于iso 11784/11785标准的数据帧格式,数据存储结构以80bit一行进行数据存储。

13、作为本发明的进一步的技术方案:所述数据存储结构支持8bit、80bit两种数据量操作。

14、作为本发明的进一步的技术方案:在步骤1中,地址正确接收后,立马执行page读操作。

15、作为本发明的进一步的技术方案:在步骤2中,根据接收指令及page是否受保护,判断是否执行page擦写操作;

16、数据段正确接收后,在crc段接收时执行page擦除操作;

17、若在未执行擦除操作前检测到编码格式或帧格式错误,则不再对eeprom执行任何操作。

18、作为本发明的进一步的技术方案:在步骤2中,在接收阶段提前执行page擦除操作可能会导致eeprom数据的丢失,crc字段编码格式错误,帧格式错误或校验错误,都应跳转执行错误流程,回写对应page,使eeprom保持原始数据。

19、作为本发明的进一步的技术方案:eeprom执行擦除前需要先读对应地址数据,并锁存,后续接收检测出错则回写锁存数据,保证eeprom存储数据的正确性。

20、作为本发明的进一步的技术方案:若在执行eeprom擦写操作过程中,检测到读卡器信号接收异常,保证eeprom擦写操作均执行完成,再控制标签执行放电操作。

21、综上所述,本发明包括以下至少一种有益技术效果:

22、本发明公开了一种关于低频电子标签存储器eeprom的控制方法,其同时满足eeprom的工艺要求及iso 11784/11785标准,相比于通用的总线结构在读写效率性能等方面都与之不匹配的问题,本发明采用专用的总线结构,支持8bit、80bit两种数据量操作,提高操作效率,且结构简单,各方面性能更优。基于工艺特性及通信格式采用本eeprom控制方案,可以显著提高操作效率,且可以保证存储数据的正确性。

技术特征:1.关于低频电子标签存储器eeprom的控制方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,为满足协议要求及eeprom控制器的工艺要求,对于eeprom的擦除操作在接收过程中执行。

3.根据权利要求2所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,接收完成或受环境干扰中断中断时,根据记录状态,执行对应的写操作。

4.根据权利要求1所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,基于iso 11784/11785标准的数据帧格式,数据存储结构以80bit一行进行数据存储。

5.根据权利要求4所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,所述数据存储结构支持8bit、80bit两种数据量操作。

6.根据权利要求1所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,在步骤1中,地址正确接收后,立马执行page读操作。

7.根据权利要求1所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,在步骤2中,根据接收指令及page是否受保护,判断是否执行page擦写操作;

8.根据权利要求1所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,在步骤2中,在接收阶段提前执行page擦除操作可能会导致eeprom数据的丢失,crc字段编码格式错误,帧格式错误或校验错误,都应跳转执行错误流程,回写对应page,使eeprom保持原始数据。

9.根据权利要求8所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,eeprom执行擦除前需要先读对应地址数据,并锁存,后续接收检测出错则回写锁存数据,保证eeprom存储数据的正确性。

10.根据权利要求9所述的关于低频电子标签存储器eeprom的控制方法,其特征在于,若在执行eeprom擦写操作过程中,检测到读卡器信号接收异常,保证eeprom擦写操作均执行完成,再控制标签执行放电操作。

技术总结本发明涉及关于低频电子标签存储器eeprom的控制方法,包括以下步骤:步骤1、地址正确接收后,执行对应page的读操作;步骤2、指令接收完成及page读操作完成后,根据指令及page是否受保护判断是否执行page擦除操作:由于擦写时间限制,在数据帧接收过程中,开始执行page擦除操作;步骤3、在数据帧接收过程中检测到异常或者CRC校验错误,page回写所读数据;正确接收,page写入所接收I D数据;步骤4、写操作完成后,再次回读page,并返回此数据。其对于基于I SO 11784/11785标准的无源电子标签,显著提高了操作效率,提升了性能,且可以保证存储数据的正确性。技术研发人员:王雅鑫,高攀,罗洵受保护的技术使用者:深圳列拓科技有限公司技术研发日:技术公布日:2024/6/11本文地址:https://www.jishuxx.com/zhuanli/20240731/185027.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。