一种用于充电桩的掉电记忆电路及方法与流程

- 国知局

- 2024-07-31 20:00:49

本发明属于电子设备控制,具体涉及了一种用于充电桩的掉电记忆电路及方法。

背景技术:

1、充电桩是电动汽车的一种充电续航装置,该装置需要精确的记录充电过程中的电能数据。在一些特殊条件(如变压器异常、接线松动)下,正在充电中的充电桩会突然掉电,进而导致一次充电记录数据丢失。在此情况下,将会给运营商家带来经营损失。

2、专利号cn201810923985.3提出一种用于充电桩的掉电记忆方法,但是该方法需要一个专门电压采集芯片及相关电路采集系统电压值。

技术实现思路

1、为解决上述技术问题,本发明提供了一种用于充电桩的掉电记忆电路及方法,在不增加电压检测芯片的前提下,依托于国产芯片gd32f407而实现。

2、为达到上述目的,本发明采用如下技术方案:

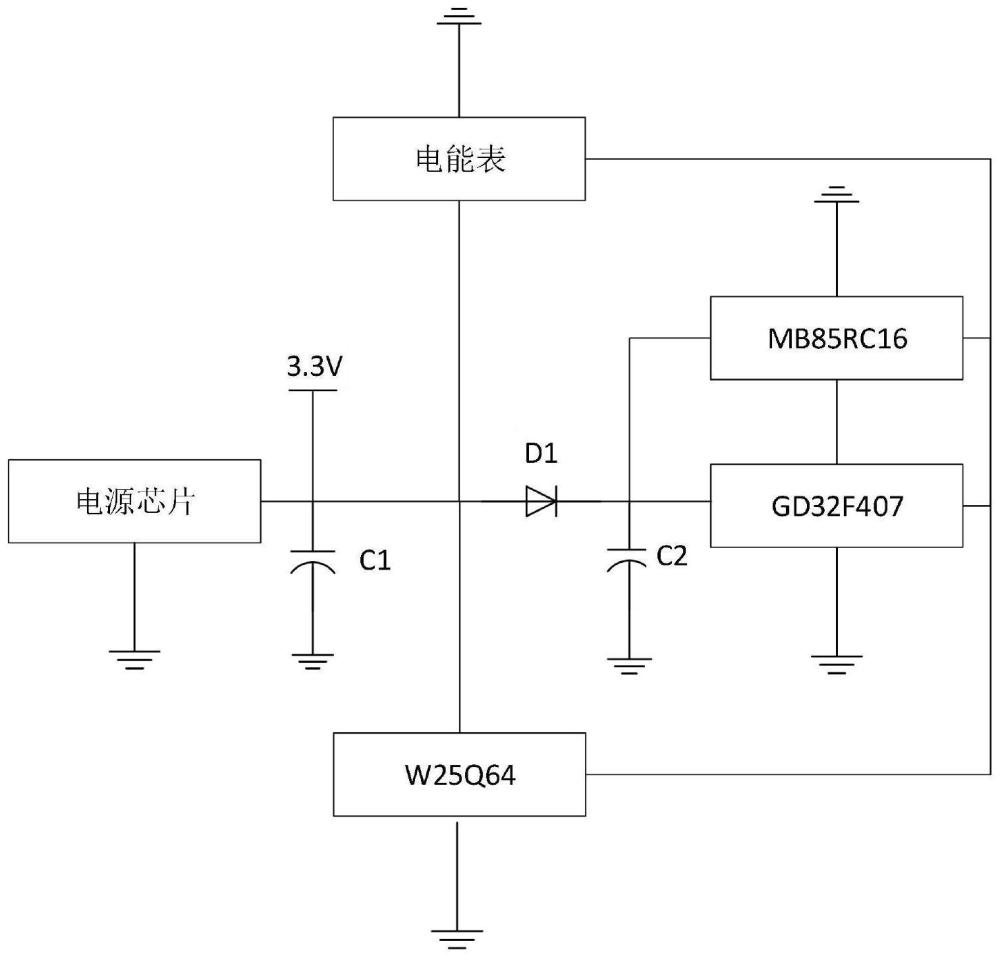

3、一种用于充电桩的掉电记忆电路,包括:电源芯片、极性电容c1、极性电容c2、二极管d1、芯片gd32f407(、串行flash w25q64、fram存储器mb85rc16、电能表;

4、其中,所述电源芯片输出正极分别连接二极管d1、极性电容c1、电能表、串行flashw25q64的正极;二极管d1正极分别连接极性电容c2、处理器芯片gd32f407、fram存储器mb85rc16的正极;电源芯片、电能表、串行flash w25q64、极性电容c1、极性电容c2、fram存储器mb85rc16、处理器芯片gd32f407的负极均接地;

5、所述处理器芯片gd32f407通过spi总线与串行flash w25q64连接;通过iic总线与fram存储器mb85rc16连接;通过ttl总线与电能表连接。

6、相应的,本发明还提供了一种用于充电桩的掉电记忆方法,所述方法包括如下步骤:

7、步骤(1)系统上电初始化,设置处理器芯片gd32f407内的掉电阈值;

8、步骤(2)检索fram存储器mb85rc16内掉电标记,若掉电标记不为0xaaaa,则正常运行系统;

9、步骤(3)若掉电标记为0xaaaa,则取出fram存储器mb85rc16内充电记录,将充电记录转存至串行flash w25q64中,同时掉电标记置为0x5555;

10、步骤(4)当系统发生掉电事件,会自动触发处理器芯片gd32f407进入掉电中断函数;

11、步骤(5)若充电桩在充电中,则将fram存储器mb85rc16内掉电标记置为0xaaaa,并将充电记录存储至fram存储器mb85rc16;若充电桩未在充电中,则不执行任何操作。

12、本发明的有益效果:

13、本发明提供了一种用于充电桩的掉电记忆电路,可保证在充电桩掉电后,会产生一个电压跌落延时50ms,保证控制芯片将充电数据记录下来。

14、本发明提供了一种用于充电桩的掉电记忆方法,可以保证将掉电前的充数据瞬间存储至fram存储器mb85rc16内,待充电桩重新上电后,将充电数据转存至串行flashw25q64,从而达到充电记录不丢失的作用。

技术特征:1.一种用于充电桩的掉电记忆电路,其特征在于,包括:电源芯片、极性电容c1、极性电容c2、二极管d1、处理器芯片gd32f407、串行flash w25q64、fram存储器mb85rc16、电能表;

2.根据权利要求1所述的一种用于充电桩的掉电记忆电路,其特征在于,当电源芯片掉电后,所述极性电容c1向电能表提供延时电压。

3.根据权利要求1所述的一种用于充电桩的掉电记忆电路,其特征在于,所述极性电容c2用于所述电源芯片掉电后,为处理器芯片gd32f407提供延时电压,使得电压由3.3v缓慢降至1.8v,延时时间为50ms。

4.根据权利要求1所述的一种用于充电桩的掉电记忆电路,其特征在于,所述二极管d1用于当电源芯片掉电后,极性电容c2只单方向向处理器芯片gd32f407提供延时电压。

5.根据权利要求1所述的一种用于充电桩的掉电记忆电路,其特征在于,所述fram存储器mb85rc16用于充电桩掉电时,存储充电记录。

6.根据权利要求1所述的一种用于充电桩的掉电记忆电路,其特征在于,所述串行flash w25q64用于充电桩正常充电时,存储充电记录。

7.一种用于充电桩的掉电记忆方法,应用于权利要求1-6任一项所述的一种用于充电桩的掉电记忆电路,其特征在于,包括如下步骤:

技术总结本发明公开了一种用于充电桩的掉电记忆电路及方法。所述电路由电源芯片、极性电容、二极管、单片机芯片、FLASH存储芯片、FRAM存储器、电能表组成。所述电源芯片输出正极分别连接二极管D1、极性电容C1、电能表、串行FLASH W25Q64的正极;二极管D1正极分别连接极性电容C2、处理器芯片GD32F407、FRAM存储器MB85RC16的正极;电源芯片、电能表、串行FLASH W25Q64、极性电容C1、极性电容C2、FRAM存储器MB85RC16、处理器芯片GD32F407的负极均接地。所述电路保证在充电桩掉电后,会产生一个电压跌落延时50ms,保证控制芯片将充电数据记录下来。技术研发人员:张法瑞,李玉泉,徐飞,史黎明,李子欣,高范强,赵聪,范满义,李步云,李耀华受保护的技术使用者:齐鲁中科电工先进电磁驱动技术研究院技术研发日:技术公布日:2024/6/13本文地址:https://www.jishuxx.com/zhuanli/20240731/185041.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表