具有施密特结构的混合型14T-SRAM单元、SRAM电路、芯片

- 国知局

- 2024-07-31 20:09:18

本发明属于静态随机存储器领域,具体涉及一种具有施密特结构的混合型14t-sram单元,采用混合型14t-sram单元作为基本单元的sram电路及其对应的存储芯片。

背景技术:

1、随着电子和互联网技术不断发展,市场对于高性能静态随机存储器的需求日益增加,高性能静态随机存储器(sram,static random-access memory)主要通过提升电路的集成度来实现,随着电路集成度的提高,芯片的功耗问题也日益严重,功耗问题目前已经成为研究人员面临的首要挑战。为保持产品的续航,市场对低工作电压的低功耗芯片的需求愈发强烈。在处理器、物联网设备和可移动设备中,sram占据了大部分的芯片面积,并产生了最高占比的运行功耗;其中,sram的静态功耗消耗了总功耗的50%以上。因此降低sram的静态功耗变得至关重要。目前关于在亚阈值电压下降低sram静态功耗的研究大多集中于优化sram外围逻辑电路或引入读写辅助电路等方式。然而受玻尔兹曼分布影响,传统mosfet器件的亚阈值摆幅在低电压应用中存在物理极限,这极大影响了mosfet器件的开关特性,并导致电路的泄漏电流随电压降低呈指数增长。总而言之,mosfet器件的上述固有缺点极大阻碍了其在超低功耗芯片中的应用。

2、而相比于mosfet器件,隧穿场效应晶体管(tfet)作为非玻尔兹曼分布器件,具有更高的开关比和更低的亚阈值摆幅,这使得tfet器件在低电压低功耗领域具有广阔的应用前景,在替代mosfet器件方面潜力巨大。但是,将tfet器件应用于sram中,仍面临以下几项挑战:一、teft器件的源极和漏极掺杂不均匀,具有单向导通性,这导致其在工作时可能出现不受栅极电压控制的正向偏置电流,这将极大增大现有tfet sram的静态功耗,并破坏存储节点的电压稳定性。二、tfet器件相对mosfet器件的导通电流更小,导致其读写能力较弱,读写噪声容限较低。三、由于tfet的延迟输出饱和特性,基于tfet的反相器的vtc曲线近似为具有平缓斜率的直线,这导致由tfet反相器对组成的存储单元比由mosfet反相器对组成的存储单元的小得多的snm(静态容限噪声,static noise margin)。

技术实现思路

1、为了解决现有tfet 型sram电路的噪声容限较低、静态功耗大、写速度较慢的问题,本发明提供一种具有施密特结构的混合型14t-sram单元,及其对应的sram电路和存储芯片。

2、本发明提供的技术方案为:

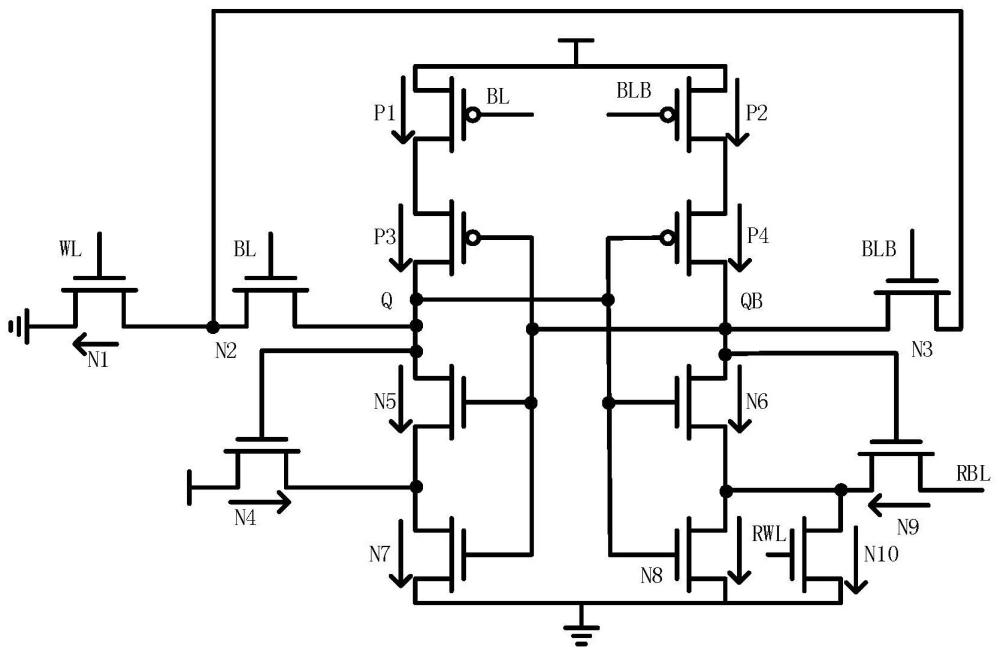

3、一种具有施密特结构的混合型14t-sram单元,其由4个ptfet晶体管p1、p2、p3、p4,8个ntfet晶体管n1、n4、n5、n6、n7、n8、n9、n10,以及两个nmos管n2、n3构成。电路连接关系如下:

4、p1、p2的源极与n4的漏极接vdd;p1的漏极和p3的源极相连;p2的漏极和p4的源极相连;p1的栅极和n2的栅极接写位线bl;p2栅极和n3的栅极接写位线blb;p3、n2、n5的漏极与p4、n4、n6、n8的栅极相连并作为存储节点q;p3、n5、n7、n9的栅极与p4、n3、n6的漏极相连并作为存储节点qb;n4、n5的源极与n7的漏极相连;n6、n9的源极与n8、n10的漏极相连;n1的漏极与n2、n3的源极相连;n1、n7、n8、n10的源极接gnd;n1的栅极接写字线wl; n10的栅极接读字线rwl;n9的漏极接读位线rbl。

5、在本发明提供的混合型14t-sram单元中,p3、n4、n5、n7构成一个施密特反相器,p4、n6、n8、n9构成另一个施密特反相器,两个反相器构成存储单元中的锁存结构。p1、p2为写辅助晶体管。p3、p4为上拉晶体管,n5、n6、n7、n8为下拉晶体管。n4、n9为反馈晶体管。n1、n2、n3构成单元传输管。

6、作为本发明进一步的改进,具有施密特结构的混合型14t-sram单元实现数据保持的操作逻辑如下:

7、将写字线wl、写位线bl、blb以及读字线rwl均置为低电平,读位线rbl置为高电平;此时,n1、n2、n3、n10关闭,p1、p2导通,锁存结构处于锁存状态,进而实现数据保持。

8、作为本发明进一步的改进,具有施密特结构的混合型14t-sram单元实现数据写入的操作逻辑如下:

9、首先,将读字线rwl置为低电平,读位线rbl置为高电平,写字线wl置为高电平。然后,根据写入的数据对写位线bl和blb的电平状态进行调整,进而通过写位线bl和blb改写存储节点q和qb的电平状态。

10、作为本发明进一步的改进,在数据写入的操作逻辑中,当需要写入数据“1”时,则将bl置为低电平,blb置为高电平。当需要写入数据“0”时,则将bl置为高电平,blb置为低电平。

11、作为本发明进一步的改进,在数据写入的操作完成后,将写字线wl置为低电平,写位线bl、blb置为低电平,p1、p2导通,锁存结构恢复锁存状态。

12、作为本发明进一步的改进,具有施密特结构的混合型14t-sram单元实现数据读取的操作逻辑如下:

13、首先,将写字线wl和写位线bl、blb均置为低电平,读位线rbl接初始电位为vdd的电容。接着,将读字线rwl置为高电平,此时,若读位线rbl的电平下降,则读取结果为数据“0”。若读位线rbl仍保持为高电平时,则读取结果为数据“1”。

14、本发明还包括一种sram电路,其包括存储阵列,以及配合存储阵列实现数据读、写、保持功能的外围电路。该存储阵列由如前述的具有施密特结构的混合型14t-sram单元按照阵列的方式排列而成。在存储阵列中,同列的所有存储单元共用写辅助晶体管p1和p2,同行的所有存储单元共用单元传输管n1。

15、作为本发明进一步的改进,在存储阵列中,每一行的各个存储单元连接在同一条写字线wl和读字线rwl上;每一列的各个存储单元连接在同一组写位线bl和blb,以及读位线rbl上。

16、本发明还包括一种存储芯片,其由如前述的sram电路封装而成。

17、本发明提供的技术方案,具有如下有益效果:

18、本发明利用12个tfet晶体管和2个cmos晶体管设计了一个14t-sram单元,该电路充分利用了低电压下tfet晶体管具有更好开关特性和更低的亚阈值摆幅的优势,采用了打断锁存结构的方式,提高了单元的写噪声容限。该方案采用施密特结构来形成sram的锁存结构,能够提高电路的噪声容限。

19、本发明设计的14t-sram方案采用漏极电压始终不低于源极电压的n型tfet晶体管作为传输控制管,可以消除tfet器件的正向偏置电流,进而降低电路的静态功耗。

20、本发明的14t-sram单元还将施密特结构中部分晶体管与读通道进行共用,并在存储阵列中对同行的单元传输管和同列中的写辅助晶体管进行复用。通过以上两种手段可以有效减少阵列中晶体管的数量,进而提高基于14t-sram单元设计的存储芯片的集成度。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185345.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。