非易失性存储器结构中的低功率多电平单元(MLC)编程的制作方法

- 国知局

- 2024-07-31 20:10:14

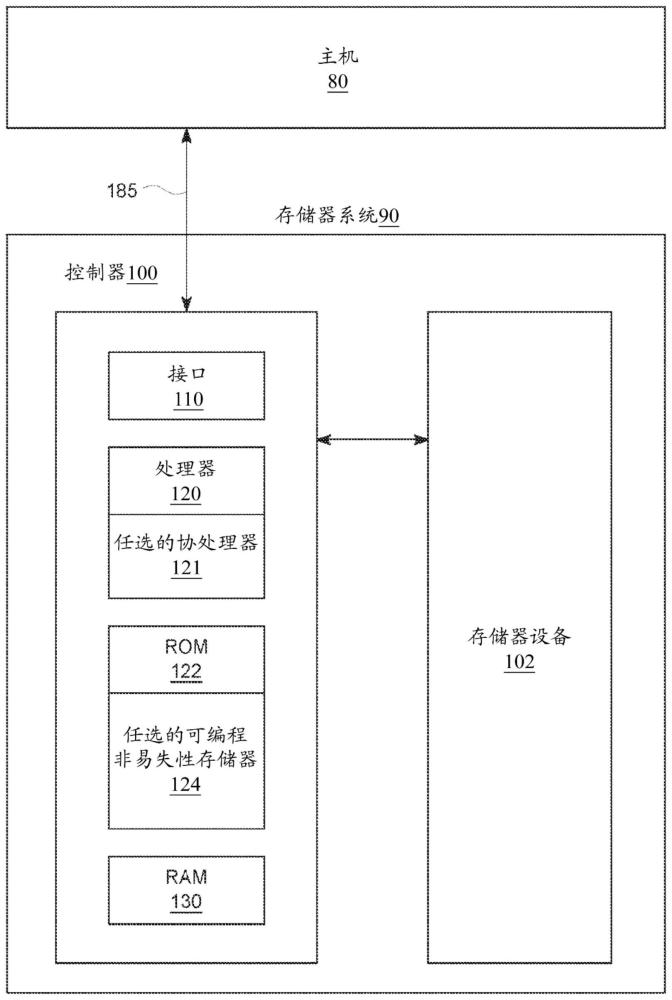

本公开涉及固态驱动器或其他设备中的非易失性存储器存储系统,包括但不限于闪存驱动器或嵌入式/可移除闪存封装件。更具体地,本公开涉及用于对非易失性存储器结构进行编程的系统和方法。

背景技术:

1、由于新兴的技术和市场力量,固态驱动器(ssd)稳定地取代依赖于磁性介质的旋转以用于读取和写入数据的先前常规数据存储系统(例如,硬盘驱动器)。固态存储器不是包括任何机械或移动部分,而是包括集成电路组件或互连的闪存部件以提供非易失性存储装置,其中即使在计划或非计划的电力中断期间也可持续保持存储的数据。因此,与基于磁盘的存储装置相比,固态驱动器固有地更快且更稳健(即,不易受到数据丢失和损坏的影响),以及消耗更少的功率并且更紧凑。因此,相对于许多类型的计算、消费电子和独立外部存储(例如,usb驱动器)设备,非易失性存储器是强大的存储解决方案。此外,非易失性存储器结构的进步已导致其存储密度能力的显著增加及功率消耗的减少,由此降低每位及每芯片位成本。

2、一般来说,非易失性存储器设备可由单独存储器单元的一个或多个阵列组成。相对于一些闪存存储器类型,每个存储器单元包括浮栅,该浮栅定位在半导体基板的沟道区上方并与之隔离,其中浮栅定位在源极区和漏极区之间。此外,控制栅极提供于浮栅上方且与浮栅隔离,其中所得晶体管的阈值电压(vth)然后由保持于浮栅上的电荷量控制且取决于保持于浮栅上的电荷量。具体地,以类似开关的方式,在激活晶体管以允许其源极区和其漏极区之间导通之前必须施加到控制栅极的最小电压量因此由浮栅上保持的电荷电平确定。因此,可通过精确地改变浮栅上的电子电荷电平将位值数据编程到存储器单元上以及从存储器单元擦除以便改变晶体管的阈值电压(vth)特性。在阵列结构中,存储器单元可由字线(行)及位线(列)寻址。

3、由该一般结构定义的一种类型的非易失性存储器由于其基于nand逻辑门的电特性而被称为nand闪存存储器。

4、如下面详细解释的,可存储在单独存储器单元中的位数取决于可在该存储器单元的阈值电压(vth)窗口内划分的不同电压范围的数量。例如,为了存储一位数据(称为二进制数据),存储器单元的可能阈值电压(vth)被分成两个范围,其中这两个范围分别被分配为逻辑数据“1”和“0”。因此,这种类型的存储密度的存储器单元可被称为“单级单元”或“slc”。

5、通过将存储器单元的阈值电压(vth)窗口进一步划分为附加的不同电压范围,可存储多级信息。因此,此类存储器单元可被称为“多态单元”。例如,为了存储两位数据,单元的阈值电压(vth)窗口可被划分为四个不同的电压范围(或状态),其中每个电压范围被分配等于例如“11”、“10”、“01”和“00”的某一位值。因此,在擦除操作之后,阈值电压(vth)为负并且因此可被定义为逻辑“11”。因此,正阈值电压可以用于“10”、“01”、“00”的状态。该存储密度的存储器单元可被称为例如“多级单元”或“mlc”。

6、在另一个示例中,为了存储三位数据,单元的电压阈值窗口可被划分为八个不同电压范围(或状态),其中每个范围被分配等于例如“111”、“110”、“100”、“010”、“011”、“000”、“001”和“101”的某一位值。因此,该存储密度的存储器单元可被称为例如“三级”或“三级单元”(“tlc”)。

7、在又一实例中,为了存储四位数据,存储器单元的阈值电压(vth)窗口可被划分为16个不同电压范围(或状态),其中每个电压范围被分配等于例如“1111”、“1110”、“1100”、“1000”、“0111”、“0011”、“0001”、“0000”、“0001”、“1001”、“1101”、“1011”、“0110”、“0100”、“0101”和“1010”的某一位值。因此,这种类型的存储密度的存储器单元可被称为例如“四级单元”或“qlc”。

8、除了关于单个存储器单元的增加的存储密度之外,非易失性存储器阵列结构的进步还导致存储器单元在关于半导体基板的竖直方向上堆叠,由此产生与平面二维阵列结构相反的三维阵列结构。

9、编程到存储器单元中的数据与存储器单元的阈值电压电平之间的具体关系取决于存储器单元采用的数据编码方案。

10、因此,包括多态数据(通过结合mlc和/或tlc型和/或qlc型单元)的存储器设备具有使用与slc型单元相同的mosfet结构和晶圆尺寸来增加的存储容量,并且因此提供有益的相当的单位节省成本。然而,由于多态存储器单元的增加的密度和划分电压范围之间的严格公差,编程操作固有地以较慢速度发生,并且相对于单态存储器单元消耗显著更多的功率,因为数据被编程到多个目标阈值电压(vth)范围,并且通过扩展,在编程期间需要较高的精度水平。因此,导出将改进多态编程操作的性能参数或特性(包括例如增加编程速度及减少功率消耗)的技术和/或方法将是有益的。

技术实现思路

1、各种实施方案包括一种用于编程非易失性存储器结构的存储器阵列的方法,该方法包括:发起关于包括存储器阵列的mlc型存储器单元的群体的编程操作,其中该编程操作包括:(i)在第一编程脉冲中,根据第一编程电压对第一可编程状态进行编程;(ii)在第二编程脉冲中,根据第二编程电压对第二可编程状态进行编程;并且(iii)在第三编程脉冲中,根据第三编程电压对第三可编程状态进行编程,其中在第一编程脉冲、第二编程脉冲和第三编程脉冲的每个期间,施加:(1)对存储器阵列的一个或多个位线的禁止条件;以及(2)对存储器阵列的一个或多个位线的零电压条件,使得存储器阵列的邻近位线的不到一半经历禁止条件与零电压条件之间的电压摆动。

2、其它实施方案包括存储器控制器,该存储器控制器包括:(1)通信通路,其被配置为耦接到非易失性存储器结构的存储器阵列;并且(2)存储器控制器被配置为:发起关于包括存储器阵列的mlc型存储器单元的群体的编程操作,其中编程操作包括:(i)在第一编程脉冲中,根据第一编程电压对第一可编程状态进行编程;

3、(ii)在第二编程脉冲中,根据第二编程电压对第二可编程状态进行编程;并且(iii)在第三编程脉冲中,根据第三编程电压对第三可编程状态进行编程,其中在第一编程脉冲、第二编程脉冲和第三编程脉冲的每个期间,施加:对存储器阵列的一个或多个位线的禁止条件;以及对存储器阵列的一个或多个位线的零电压条件,使得存储器阵列的邻近位线的不到一半经历禁止条件与零电压条件之间的电压摆动。

4、额外实施方案包括一种非易失性存储器系统,该非易失性存储器系统包括:存储器阵列,其包括mlc型存储器单元的群体;以及存储器控制器,其耦接到存储器阵列,并且:(1)发起关于存储器阵列的编程操作,其中该编程操作包括:(i)在第一编程脉冲中,根据第一编程电压对第一可编程状态进行编程;

5、(ii)在第二编程脉冲中,根据第二编程电压对第二可编程状态进行编程;并且(iii)在第三编程脉冲中,根据第三编程电压对第三可编程状态进行编程,(2)其中在第一编程脉冲、第二编程脉冲和第三编程脉冲的每个期间,施加:(i)对存储器阵列的一个或多个位线的禁止条件;以及(ii)对存储器阵列的一个或多个位线的零电压条件,使得存储器阵列的邻近位线的不到一半经历禁止条件与零电压条件之间的电压摆动。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185379.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。