一种存储芯片的故障测试设备及方法与流程

- 国知局

- 2024-07-31 20:15:04

本发明涉及芯片测试,特别是指一种存储芯片的故障测试设备及方法。

背景技术:

1、存储芯片是一种用于存储数据的电子设备,广泛应用于各种电子产品中,如计算机、手机、数码相机等。这些芯片可以是易失性的,如动态随机存取存储器(dram)和静态随机存取存储器(sram),它们在断电时会丢失存储的信息,也可以是非易失性的,如闪存,即使在断电情况下也能保持数据不丢失。

2、存储芯片的故障测试是电子设备制造过程中不可或缺的一环,它确保芯片能可靠存储和处理数据,提高产品整体质量和用户体验。这些测试帮助发现并修复潜在缺陷,降低后期维护成本,减少保修索赔,同时还能推动设计和制造过程的优化。

3、然而现有的存储芯片测试设备和测试流程在测试过程中往往不考虑测试数据的格式,仅通过大量重复数据重复注入存储芯片进行故障测试,而且在测试的过程中对所有的存储单元均无差别地多次重复注入数据,在这一重复测试过程中,正常的存储单元的擦除次数被大量消耗,不仅测试效率低,而且消耗大量的存储芯片寿命。

技术实现思路

1、为了解决现有技术存在的现有的存储芯片测试设备和测试流程在测试过程中往往不考虑测试数据的格式,仅通过大量重复数据重复注入存储芯片进行故障测试,而且在测试的过程中对所有的存储单元均无差别地多次重复注入数据,在这一重复测试过程中,正常的存储单元的擦除次数被大量消耗,不仅测试效率低,而且消耗大量的存储芯片寿命的技术问题,本发明提供了一种存储芯片的故障测试设备及方法。

2、本发明实施例提供的技术方案如下:

3、第一方面

4、本发明实施例提供的一种存储芯片的故障测试设备,包括:

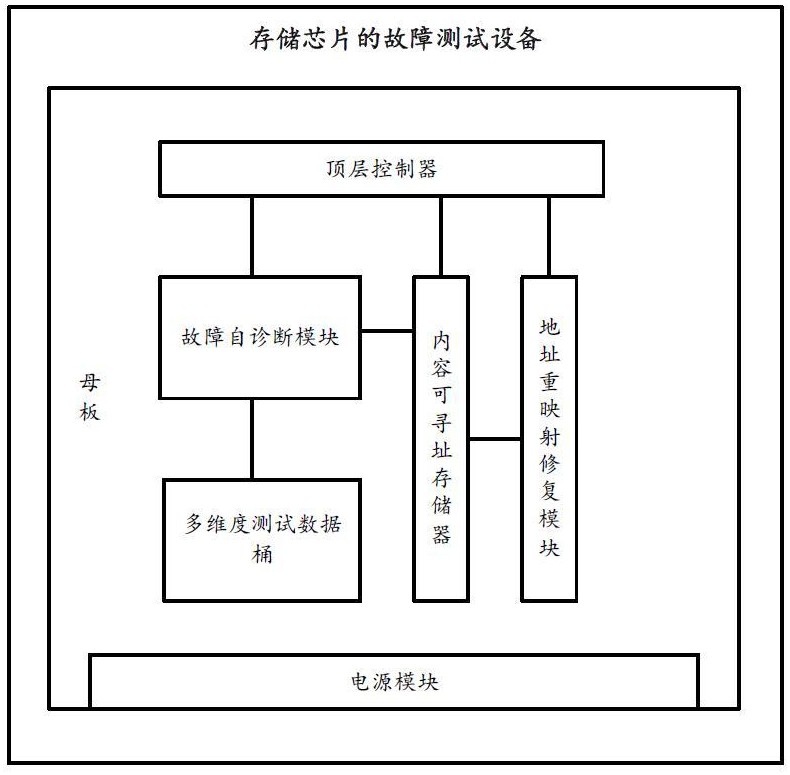

5、顶层控制器、多维度测试数据桶、故障自诊断模块、地址重映射修复模块和内容可寻址存储器;

6、所述顶层控制器分别与所述故障自诊断模块、所述地址重映射修复模块以及所述内容可寻址存储器连接;

7、所述地址重映射修复模块与所述内容可寻址存储器连接;

8、所述故障自诊断模块分别与所述多维度测试数据桶和所述内容可寻址存储器连接;

9、所述存储芯片的控制器与所述顶层控制器连接,所述顶层控制器向所述故障自诊断模块发送测试指令,所述故障自诊断模块根据所述测试指令从所述多维度测试数据桶中抽取测试数据对所述存储芯片进行测试,输出故障位置;

10、所述内容可寻址存储器用于存储所述故障位置;

11、测试结束后所述地址重映射修复模块抽取所述内容可寻址存储器中的故障位置对所述存储芯片进行故障修复。

12、在所述的存储芯片的故障测试设备中,优选地,所述故障测试设备还包括:母板和电源模块;所述顶层控制器、所述多维度测试数据桶、所述故障自诊断模块、所述地址重映射修复模块和所述内容可寻址存储器均布置于所述母板上;所述电源模块与所述母板连接,以向所述故障测试设备供电。

13、第二方面

14、本发明实施例提供的一种存储芯片的故障测试方法,应用于如第一方面所述的故障测试设备,方法包括:

15、s1:获取所述存储芯片的冗余资源,其中,所述冗余资源为所述存储芯片动态启用的非固定存储资源;

16、s2:从所述多维度测试数据桶抽取目标测试数据,其中,所述目标测试数据包括故障初筛层、干扰故障检测层和耦合故障检测层;

17、s3:利用所述目标测试数据对所述存储芯片进行循环测试,输出故障位置;

18、s4:结合所述故障位置,以所述冗余资源为约束建立故障修复线性规划模型,其中,所述故障修复线性规划模型包括故障单元修复数量;

19、s5:以故障单元修复数量最大为目标,结合贪心算法和局部搜索策略对所述故障修复线性规划模型进行寻优,输出最优修复策略;

20、s6:根据所述最优修复策略对所述存储芯片进行修复;

21、s7:输出所述最优修复策略中未修复的故障位置,完成所述存储芯片的测试。

22、在所述的存储芯片的故障测试方法中,优选地,所述故障初筛层包括数量相同的零一数据,所述干扰故障检测层包括棋盘格数据和倒棋盘格数据,所述耦合故障检测层包括行行翻转数据和伪随机数据。

23、在所述的存储芯片的故障测试方法中,优选地,所述s3具体包括:

24、s301:获取所述存储芯片的可寻址存储单元;

25、s302:以覆盖所述可寻址存储单元为目标,将所述故障初筛层中的全零数据和全一数据通过ate设备依次输入至所述存储芯片,记录一次测试结果,其中,所述一次测试结果包括读写失败的存储单元;

26、s303:对所述一次测试结果进行基于k-means聚类算的聚类分析,获取故障区域;

27、s304:将所述干扰故障检测层和所述耦合故障检测层的数据通过所述ate设备依次输入至所述故障区域进行二次筛选,记录二次测试结果,其中,所述二次测试结果包括所述故障区域内各个存储单元在相同测试数据和不同测试数据下的存在读写故障的故障位置;

28、s305:输出所述故障位置。

29、在所述的存储芯片的故障测试方法中,优选地,所述s303具体包括:

30、s303a:从所述故障区域内随机选择多个读写失败的存储单元作为初始聚类中心;

31、s303b:计算每个读写失败的存储单元到每个所述初始聚类中心的欧式距离:

32、;

33、其中, d表示欧氏距离,表示读写失败的存储单元 u的物理地址,表示第 i个初始聚类中心的坐标,, k表示所述初始聚类中心总数量;

34、s303c:将读写失败的存储单元分配至欧氏距离最小的初始聚类中心;

35、s303d:取聚类内所有坐标点的均值,将所述均值作为新的初始聚类中心;

36、s303e:迭代次数加1,返回步骤s303b,直到所述初始聚类中心不再改变或达到预设的迭代次数。

37、在所述的存储芯片的故障测试方法中,优选地,所述故障修复线性规划模型具体为:

38、;

39、其中, m表示故障单元修复数量,表示二进制指示变量,当所述存储芯片的第 i行第 j列的故障单元存在故障时=1,否则,=0,,,其中, m和 n分别表示所述存储芯片的最大行数和最大列数,表示二进制辅助变量,当第 i行第 j列的故障单元被修复时=1,否则,=0,表示是否选用所述冗余资源中第 i个备用行的二进制决策变量,表示是否选用所述冗余资源中第 j个备用列的二进制决策变量, r表示所述冗余资源的最大行数, c表示所述冗余资源的最大列数。

40、在所述的存储芯片的故障测试方法中,优选地,所述s5具体包括:

41、s501:统计所述存储芯片中每行和每列的故障总数;

42、s502:将与所述故障总数呈正比例关系的优先级分配至各个故障单元;

43、s503:将所述贪心算法的贪心选择目标设置为从最高优先级到最低优先级对所述故障单元进行逐个修复,制定初步修复策略,并获取所述初步修复策略的故障单元修复数量最大值:

44、;

45、其中,max表示取最大值;

46、s504:对所述初步修复策略执行邻域结构的局部变更操作,其中,所述变更操作包括添加操作、移出操作和替换操作;

47、s505:计算变更操作后的故障单元修复数量:

48、;

49、其中,表示变更后的故障单元修复数量,表示变更后的第 k行的故障单元数量,表示变更行集合,表示变更后的第 l列的故障单元数量,表示变更列集合, o表示重叠故障单元数量,表示第 k行第 l列的交点二进制指示变量,若交点为故障单元,则=1,否则,=0;

50、s506:重复执行s504-s505,直至所述存储芯片中的行和列均被覆盖,即所述变更行集合和所述变更列集合执行完毕;

51、s507:取变更后的故障单元修复数量的最大值,并记录此时的变更修复策略;

52、s508:取故障单元修复数量最大值对应的策略作为最优恢复策略:

53、;

54、其中,表示变更后的故障单元修复数量的最大值。

55、在所述的存储芯片的故障测试方法中,优选地,所述s6具体为:根据所述最优修复策略,通过修改所述存储芯片的地址译码逻辑将所述故障单元对应的故障位置映射至所述冗余资源的备用行或者备用列,完成所述存储芯片的修复。

56、在所述的存储芯片的故障测试方法中,优选地,在所述s7之后,还包括:

57、在未修复的故障位置对应的故障数量大于预设故障数量的情况下,发出预警。

58、本发明实施例提供的技术方案带来的有益效果至少包括:

59、在本发明中,构建了包括顶层控制器、多维度测试数据桶、故障自诊断模块、地址重映射修复模块和内容可寻址存储器的故障测试设备,利用多维度测试数据桶中存储的故障初筛层、干扰故障检测层和耦合故障检测层进行有序分层的测试。在测试过程中,充分利用存储芯片的冗余资源,利用分层的测试数据逐步缩减测试的存储芯片范围,并以故障单元修复数量最大为目标,结合贪心算法和局部搜索策略对所述故障修复线性规划模型进行寻优,标记未修复的故障位置,以评估存储芯片的可用情况,在快速完成测试的同时,能够利用内容可寻址存储器和地址重映射修复模块,在测试结束后执行最佳的故障修复,最大程度地降低测试过程中的正常存储单元擦除次数的磨损,测试效率高,且能够自动准确地定位故障位置。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185549.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表