多器件并行测试方法、系统、终端及存储介质与流程

- 国知局

- 2024-07-31 20:16:17

本技术涉及智能测试,尤其是涉及一种多器件并行测试方法、系统、终端及存储介质。

背景技术:

1、硬件测试是产品质量控制中的重要一环,也是保障用户安全和体验的关键步骤,以spi nor flash存储器为例,spi nor flash存储器在当前半导体行业中广泛应用于存储数据。作为各种类型的电子设备的核心存储器件。spi nor flash存储器的数据稳定对于航天航空,电子通信等重要行业具有重大意义。因此,spi nor flash存储器功能完整性的测试工作十分重要。

2、但存储器测试设备对测试操作人员往往具有一定的技术门槛要求,相关技术中多数测试设备只能同时测试一片spi nor flash存储器,若需要对大批量的器件进行测试,则需要面临存储器型号不相同,导致无法协同测试等问题。

技术实现思路

1、为了解决大批量的器件进行测试时需要面临型号不相同,导致无法协同测试等问题的问题,本技术提供了一种多器件并行测试方法、系统、终端及存储介质。

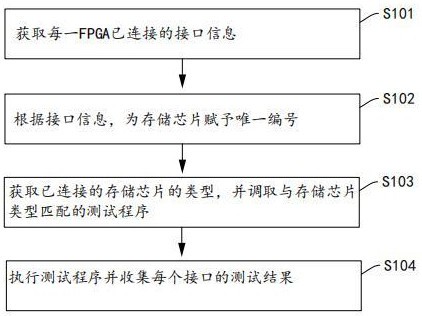

2、在本技术的第一方面,提供一种多器件并行测试方法,应用于上位机,其特征在于,包括:

3、获取每一fpga已连接的接口信息;

4、根据所述接口信息,为存储芯片赋予唯一编号,所述唯一编号与对应的fpga接口位置相关联;

5、读取每一个唯一编号对应的存储芯片的类型;

6、根据所述每一个唯一编号对应的存储芯片的类型,为每一fpga分配与存储芯片的类型匹配的测试程序,并为每一fpga生成对应测试程序的测试指令;

7、将每一个唯一编号对应的存储芯片的类型输入至预设的脚本生成模型中,得到对应每一fpga的测试脚本,所述测试脚本包括适用于对应fpga的测试程序和测试指令;

8、获取fpga返还的测试结果,筛选不合格的存储芯片标记对应的接口位置,并对不合格的存储芯片的坏点位置进行记录。

9、通过采用上述技术方案,先使用fpga对已连接的存储芯片的类型进行识别,上位机接收存储芯片的类型后,先对存储芯片进行编码,再将编码后的存储芯片的类型输入至预设的脚本生成模型中,生成适用于不同fpga的测试脚本,再依赖fpga的并行处理能力执行对应的测试脚本,实现对大量flash存储芯片并行测试,从而完成在同一个fpga上对不同类型的存储芯片的并行测试,简化了大量存储芯片的测试时分类的需求,又通过连接不同的fpga横向拓展了测试数量,提高了测试效率。

10、在一种可能的实现方式中,将每一个唯一编号对应的存储芯片的类型输入至预设的脚本生成模型中,得到对应每一fpga的测试脚本,包括:

11、根据所述每一个唯一编号对应的存储芯片的类型,确定每一fpga连接的存储芯片的类型和对应类型的存储芯片的接口位置;

12、根据每一fpga连接的存储芯片的类型,为对应的fpga分配与存储芯片的类型匹配的测试程序;

13、根据每一fpga连接的存储芯片的类型和对应类型的存储芯片的接口位置,为每一fpga生成对应测试程序的测试指令。

14、在一种可能的实现方式中,获取fpga返还的测试结果,筛选不合格的存储芯片标记对应的接口位置,并对不合格的存储芯片的坏点位置进行记录,包括:

15、根据所述测试结果,将不合格的存储芯片进行标记;

16、根据所述不合格芯片的唯一编号,调取对应的接口位置;

17、并根据测试结果中测试失败的测试项目,确定不合格存储芯片的坏点位置。

18、一种多器件并行测试方法,应用于fpga,包括:

19、获取已连接的存储芯片的类型和对应的接口信息;

20、将所述存储芯片的类型和接口信息发送至上位机,以使得上位机根据所述存储芯片的类型返还与存储芯片类型匹配的测试程序和测试指令,所述测试指令用于为每一存储芯片调取对应的测试程序;

21、根据所述测试指令,针对不同类型的存储芯片执行不同的测试程序。

22、在一种可能的实现方式中,根据所述测试指令,针对不同类型的存储芯片执行不同的测试程序,包括:

23、获取每一存储芯片测试时的写入地址;所述写入地址为测试数据写入存储芯片的地址;

24、判断所述写入地址不为最大写入地址后,向存储芯片的写入地址写入预设大小的测试数据;

25、获取写入测试数据的写入时间;

26、读取写入的测试数据,得到读取数据;

27、将读取数据与测试数据进行对比,得到读取结果;

28、当所述写入时间不超过预设时间且读取结果为一致时,将写入地址递增预设大小作为新的写入地址;所述预设大小等同于测试数据的大小;

29、依次使用预设的四组测试数据对存储芯片都进行测试后,测试结束;所述测试数据包括连续高电平、连续低电平、高低电平切换和低高电平切换的数据。

30、在一种可能的实现方式中,将读取数据与测试数据进行对比,得到读取结果后,还包括:

31、当所述写入时间超过预设时间或读取结果为不一致时,将存储芯片标记为不合格并获取对应的接口信息;

32、记录存储芯片不合格的写入地址;

33、将不合格的存储芯片的写入地址与接口信息发送至上位机。

34、在一种可能的实现方式中,执行所述测试程序,还包括:

35、整片擦除存储芯片内的数据;

36、获取每一存储芯片的擦除时间并整片读取存储芯片内数据;

37、将储存芯片内数据与默认数据进行比对,得到对比结果;

38、当所述擦除时间大于预设时间或对比结果为不一致时,标记对应存储芯片测试失败并暂存测试结果。

39、在本技术的第二方面,提供一种多器件并行测试系统,包括:

40、上位机,上位机上运行有测试软件,所述测试软件用于下发测试指令和显示测试结果。

41、flash测试板,每个flash测试板连接多个待测试的存储芯片,并连接同一个上位机。

42、flash测试板包括一片fpga、串口通信模块、电源模块,所述fpga连接有多个用以放置被测试存储芯片的夹具。

43、在本技术的第三方面,提供一种终端,具有实现多器件并行测试的特点。

44、本技术的上述申请目的三是通过以下技术方案得以实现的:

45、一种终端,包括存储器和处理器,所述存储器上存储有能够被处理器加载并执行上述多器件并行测试方法的计算机程序。

46、在本技术的第四方面,提供一种计算机存储介质,能够存储相应的程序,具有便于实现多器件并行测试的特点。

47、本技术的上述申请目的四是通过以下技术方案得以实现的:

48、一种计算机可读存储介质,存储有能够被处理器加载并执行上述任一种多器件并行测试方法的计算机程序。

49、综上所述,本技术包括以下有益技术效果:先使用fpga对已连接的存储芯片的类型进行识别,上位机接收存储芯片的类型后,先对存储芯片进行编码,再将编码后的存储芯片的类型输入至预设的脚本生成模型中,生成适用于不同fpga的测试脚本,再依赖fpga的并行处理能力执行对应的测试脚本,实现对大量flash存储芯片并行测试,从而完成在同一个fpga上对不同类型的存储芯片的并行测试,简化了大量存储芯片的测试时分类的需求,又通过连接不同的fpga横向拓展了测试数量,提高了测试效率。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185648.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。