测试装置、测试方法和测试系统与流程

- 国知局

- 2024-07-31 20:17:02

本申请涉及内存颗粒测试,尤其涉及一种测试装置、测试方法和测试系统。

背景技术:

1、为了解内存颗粒的坏块、读干扰以及擦写寿命等特性,需要对内存颗粒进行测试,目前的测试方法主要是将单个测试座将内存颗粒连接到电脑,写入测试程序,再重新上电进行测试,每项测试完成后需要读取测试数据,再写入下一个测试程序,重复这个过程直至完成全部测试并读取到全部测试数据,导致时效差,完整的测试流程需要对存储设备逐个多次写入测试程序,耗费人力且效率较低;且无法实时监测到当前测试进度和状况,只能等测试结束再读取数据后才能了解到测试异常现象。

2、受限于x86-64计算机架构,目前主流的电脑测试平台支持的内存总线位宽为64bit,而内存颗粒单颗的位宽为4bit、8bit或16bit,所以在进行内存测试时,就需要将内存颗粒进行组合,使其达到64bit的位宽,也就是说,4bit的颗粒需要16颗,8bit的颗粒需要8颗,16bit的颗粒需要4颗,组合成总线位宽为64bit的内存条,最终才能再进行测试,测试灵活度低。

技术实现思路

1、本申请的目的是提供一种测试装置、测试方法和测试系统,可以对单颗、多颗,不限于4bit、8bit、16bit的位宽的内存颗粒也能进行测试,大大提高测试灵活度。

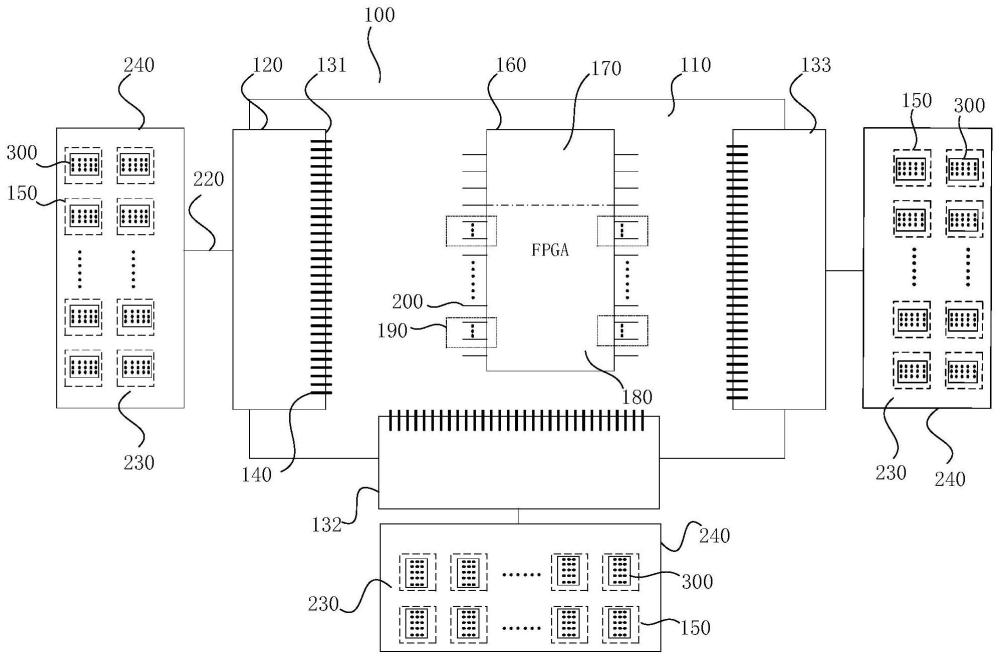

2、本申请公开一种测试装置,所述测试装置包括印刷电路板和fpga芯片,所述fpga芯片集成在所述印刷电路板上,所述印刷电路板上包括至少一个测试接口区,所述测试接口区包括测试接口,所述测试接口与n个mbit位宽的内存颗粒电连接;所述fpga芯片包括控制模块和可编程逻辑模块,所述可编程逻辑模块包括n个测试接口管脚组,每个测试管脚组通过所述测试接口与每个mbit位宽的内存颗粒一一对应连接,且定义出与每个mbit位宽的内存颗粒对应的管脚类型;其中,所述可编程逻辑模块对应不同位宽的内存颗粒时,分别将对应的测试管脚定义成对应位宽的内存颗粒的管脚类型,n≥1,m≥2n,n≥1,n,m,n为自然数。

3、可选的,所述测试接口区包括n个安装位,每个安装位安装一个mbit的内存颗粒,所述测试接口包括多个测试引脚,每个测试接口管脚组包括多个测试管脚,所述测试管脚通过所述测试引脚与所述安装位上的内存颗粒的bga焊盘连接,以将多个所述内存颗粒组合成一个位宽为n*m的内存条进行测试,或分别对每个mbit位宽的内存颗粒进行测试。

4、可选的,将n个mbit的内存颗粒,安装在一个测试治具上,所述测试治具与所述测试接口区上的测试接口电连接,所述测试接口包括多个测试引脚,每个测试接口管脚组包括多个测试管脚,所述测试管脚通过所述测试引脚与所述测试治具上的内存颗粒的bga焊盘连接,以对所述测试治具上的所述内存颗粒形成的位宽为n*m的内存条进行测试,或分别对每个mbit位宽的内存颗粒进行测试。

5、可选的,所述测试装置包括数据线缆,n个mbit位宽的内存颗粒集成在一个测试子板上,所述测试子板包括子板接口,所述数据线缆一端连接所述测试接口,一端连接所述子板接口。

6、可选的,每个所述内存颗粒包括地址bga焊盘、电源bga焊盘以及数据bga焊盘,不同内存颗粒的地址bga焊盘、电源bga焊盘连接通过测试引脚连接所述可编程逻辑模块的同一批测试管脚。

7、可选的,所述测试接口区设有三个,三个测试接口区内的测试接口类型不同,所述可编程逻辑模块的测试接口管脚组分别通过三个测试接口与每个测试接口对应的每个mbit位宽的内存颗粒一一对应连接,且定义成与每个mbit位宽的内存颗粒对应的管脚类型。

8、可选的,三个测试接口分别为第一测试接口、第二测试接口和第三测试接口,所述第一测试接口连接的内存颗粒的总位宽规格与所述第二测试接口连接的内存颗粒的总位宽规格不同,所述第一测试接口连接的内存颗粒的总位宽规格与所述第三测试接口连接的内存颗粒的总位宽规格相同,内存颗粒的数量不同。

9、本申请公开了一种内存颗粒的测试方法,用于如上任一所述的测试装置对内存颗粒进行测试,所述测试方法包括:

10、启用预设的测试接口,判断测试待测试的内存颗粒的位宽类型;

11、fpga芯片的可编程逻辑模块定义出与每个mbit位宽的内存颗粒对应的管脚类型,执行测试指令,并输出测试信号至对应的测试接口,以实现待测试的内存颗粒的性能测试;

12、其中,测试指令可以是针对所有内存颗粒组成的总位宽的测试指令,也可以是单个内存颗粒对应位宽的测试指令。

13、可选的,所述fpga芯片的可编程逻辑模块定义出与每个mbit位宽的内存颗粒对应的管脚类型,执行测试指令,并输出测试信号至对应的测试接口,以实现待测试的内存颗粒的性能测试的步骤包括:

14、选择预设的测试频率进行性能测试,并判断是否报错,若是,则自动调节测试频率,再次进行性能测试,若否,则测试完成。

15、本申请还公开了一种测试系统,所述测试系统包括如上任一所述的测试装置和测试平台,所述测试装置与所述测试平台连接,通过所述测试平台操作完成所述测试装置的测试。

16、相对于具备x86-64计算机架构,只能测试固定位宽的的测试装置来说,本申请将fpga芯片集成在印刷电路板上形成测试装置,在印刷电路板上设置至少一个测试接口区,所述测试接口区包括测试接口,所述测试接口与n个mbit位宽的内存颗粒电连接;所述fpga芯片的可编程逻辑模块包括n个测试接口管脚组,每个测试管脚组通过所述测试接口与每个mbit位宽的内存颗粒一一对应连接,且定义出与每个mbit位宽的内存颗粒对应的管脚类型;所述可编程逻辑模块对应不同位宽的内存颗粒时,分别将对应的测试管脚定义成对应位宽的内存颗粒的管脚类型;可以对多个内存颗粒组成的内存条进行测试,也可以对每个内存颗粒进行测试,提供测试的灵活度,且可以快速找出存在问题的内存颗粒,提高测试效率。

技术特征:1.一种测试装置,其特征在于,所述测试装置包括印刷电路板和fpga芯片,所述fpga芯片集成在所述印刷电路板上,所述印刷电路板上包括至少一个测试接口区,所述测试接口区包括测试接口,所述测试接口与n个mbit位宽的内存颗粒电连接;

2.如权利要求1所述的测试装置,其特征在于,所述测试接口区包括n个安装位,每个安装位安装一个mbit的内存颗粒,所述测试接口包括多个测试引脚,每个测试接口管脚组包括多个测试管脚,所述测试管脚通过所述测试引脚与所述安装位上的内存颗粒的bga焊盘连接,以将多个所述内存颗粒组合成一个位宽为n*m的内存条进行测试,或分别对每个mbit位宽的内存颗粒进行测试。

3.如权利要求1所述的测试装置,其特征在于,将n个mbit的内存颗粒,安装在一个测试治具上,所述测试治具与所述测试接口区上的测试接口电连接,所述测试接口包括多个测试引脚,每个测试接口管脚组包括多个测试管脚,所述测试管脚通过所述测试引脚与所述测试治具上的内存颗粒的bga焊盘连接,以对所述测试治具上的所述内存颗粒形成的位宽为n*m的内存条进行测试,或分别对每个mbit位宽的内存颗粒进行测试。

4.如权利要求1所述的测试装置,其特征在于,所述测试装置包括数据线缆,n个mbit位宽的内存颗粒集成在一个测试子板上,所述测试子板包括子板接口,所述数据线缆一端连接所述测试接口,一端连接所述子板接口。

5.如权利要求2所述的测试装置,其特征在于,每个所述内存颗粒包括地址bga焊盘、电源bga焊盘以及数据bga焊盘,不同内存颗粒的地址bga焊盘、电源bga焊盘连接通过测试引脚连接所述可编程逻辑模块的同一批测试管脚。

6.如权利要求1-5任意一项所述的测试装置,其特征在于,所述测试接口区设有三个,三个测试接口区内的测试接口类型不同,所述可编程逻辑模块的测试接口管脚组分别通过三个测试接口与每个测试接口对应的每个mbit位宽的内存颗粒一一对应连接,且定义成与每个mbit位宽的内存颗粒对应的管脚类型。

7.如权利要求6所述的测试装置,其特征在于,三个测试接口分别为第一测试接口、第二测试接口和第三测试接口,所述第一测试接口连接的内存颗粒的总位宽规格与所述第二测试接口连接的内存颗粒的总位宽规格不同,所述第一测试接口连接的内存颗粒的总位宽规格与所述第三测试接口连接的内存颗粒的总位宽规格相同,内存颗粒的数量不同。

8.一种内存颗粒的测试方法,用于如权利要求1-7任意一项所述的测试装置对内存颗粒进行测试,其特征在于,所述测试方法包括:

9.如权利要求8所述的测试方法,其特征在于,所述fpga芯片的可编程逻辑模块定义出与每个mbit位宽的内存颗粒对应的管脚类型,执行测试指令,并输出测试信号至对应的测试接口,以实现待测试的内存颗粒的性能测试的步骤包括:

10.一种测试系统,其特征在于,包括如权利要求1-7任意一项所述的测试装置和测试平台,所述测试装置与所述测试平台连接,通过所述测试平台操作完成所述测试装置的测试。

技术总结本申请公开了一种测试装置,测试方法和测试系统,所述测试装置包括印刷电路板和集成在印刷电路板上的FPGA芯片,印刷电路板上包括至少一个测试接口,测试接口与n个mbit位宽的内存颗粒电连接;FPGA芯片包括控制模块和可编程逻辑模块,可编程逻辑模块包括n个测试接口管脚组,每个测试管脚组通过所述测试接口与每个mbit位宽的内存颗粒一一对应连接,且定义出与每个mbit位宽的内存颗粒对应的管脚类型。本申请将FPGA芯片集成在印刷电路板上,即通过FPGA芯片替代原来的测试架构,不受限于64Bit的带宽,数据位宽都是可配的,可以随心所欲的对内存颗粒进行性能测试,即可以对单个颗粒实现单独测试,也可以对多个颗粒组成的内存条进行整体测试。技术研发人员:徐张坤,韩统亮受保护的技术使用者:深圳市时创意电子股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/185685.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表