用于高速时域交织ADC的神经网络校准方法及装置

- 国知局

- 2024-08-02 15:08:00

本发明属于电子工程和机器学习交叉,具体涉及一种用于高速时域交织adc的神经网络校准方法及装置。

背景技术:

1、时域交织模数转换器(time-interleaved adc,简称tiadc)在使用时经常遇到不同通道间失配和非线性等问题,存在这些问题的tiadc的转换结果在频域范围内会表现为存在杂散与谐波,在时域表现为结果偏离理论值,上述问题,可能会导致tiadc处理性能降低。因此对tiadc进行误差校准十分重要。

2、现有技术中,一般采用在采样保持电路中使用可编程电容阵列(pca)的方法来进行失配校准,该技术的原理是通过多路复用器来选择性地将电容器的底板连接到地或输入节点来调整采样电容的量。这一方法避免了传统采样保持电路在关态下采样电容会存在悬空节点的问题,进而避免了片上信号通过悬空节点产生耦合进而产生失配的问题。

3、但由于现有的tiadc失配校准技术,需要引入新的电路元件,这在一定程度上增加了电路复杂度与电路规模,进而增加了使用成本。此外,额外硬件部分的添加,将改变原本电路的带宽,可能会导致原本电路的带宽降低。

技术实现思路

1、为了解决现有技术中所存在的上述问题,本发明提供了一种用于高速时域交织adc的神经网络校准方法及装置。

2、本发明要解决的技术问题通过以下技术方案实现:

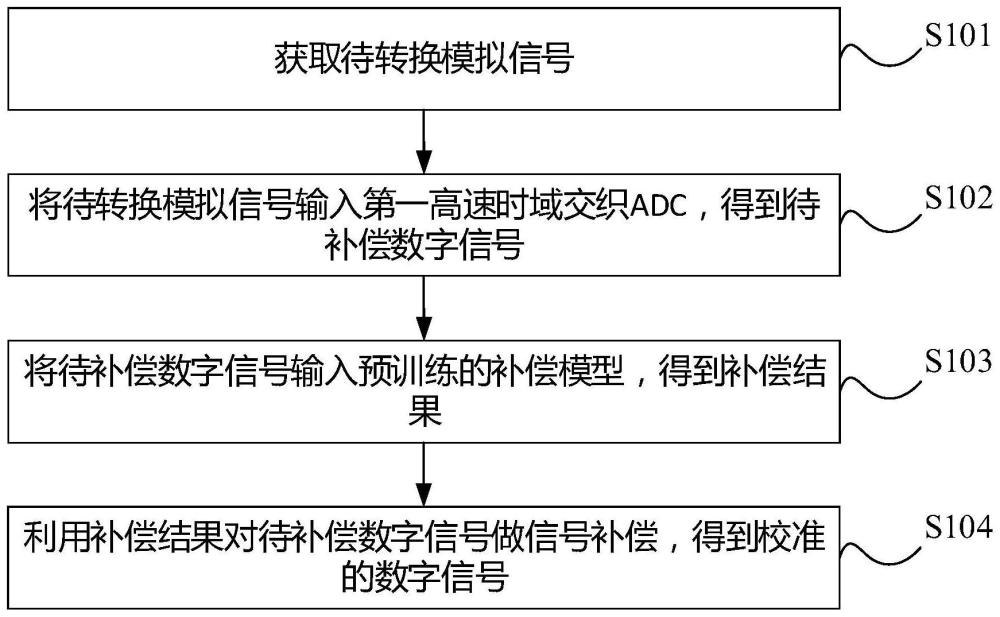

3、第一方面,本发明提供了一种用于高速时域交织adc的神经网络校准方法,包括:

4、获取待转换模拟信号;

5、将待转换模拟信号输入第一高速时域交织adc,得到待补偿数字信号;

6、将待补偿数字信号输入预训练的补偿模型,得到补偿结果;

7、利用补偿结果对待补偿数字信号做信号补偿,得到校准的数字信号;预训练的补偿模型通过多个理想数字信号以及与理想数字信号对应的实际数字信号联合训练得到。

8、可选地,实际数字信号样本通过第一高速时域交织adc获取得到;

9、理想数字信号样本通过第二高速时域交织adc获取得到;

10、第一高速时域交织adc中包括多个第一子adc;第二高速时域交织adc中包括多个第二子adc;

11、多个第一子adc的参数存在不同;多个第二子adc的参数均相同。

12、可选地,利用补偿结果对待补偿数字信号做信号补偿,得到校准的数字信号,包括:

13、将补偿结果与待补偿数字信号进行求和处理,得到校准的数字信号。

14、可选地,预训练的补偿模型的训练过程包括:

15、获取多个理想数字信号样本以及与理想数字信号样本对应的多个实际数字信号样本;

16、计算理想数字信号样本与对应的实际数字信号样本之间的差值,得到多个失配样本数据;

17、对多个失配样本数据进行离散信号处理,得到多个离散数据;

18、利用多个离散数据、实际数字信号样本以及预设损失函数对初始补偿模型进行训练;

19、将达到收敛条件的初始补偿模型作为预训练的补偿模型。

20、可选地,将达到收敛条件的初始补偿模型作为预训练的补偿模型,包括:

21、将达到预设迭代次数的初始补偿模型作为预训练的补偿模型;或,

22、将预设损失函数的输出值,小于预设阈值时对应的初始补偿模型作为预训练的补偿模型。

23、可选地,预设损失函数为均方误差损失函数。

24、可选地,预训练的补偿模型,包括:

25、输入层、单层隐藏层以及输出层;

26、单层隐藏层中设置有relu函数。

27、第二方面,本发明提供一种用于高速时域交织adc的神经网络校准装置,包括:获取模块、转换模块、计算模块以及补偿模块;

28、获取模块,用于获取待转换模拟信号;

29、转换模块,用于将待转换模拟信号输入第一高速时域交织adc,得到待补偿数字信号;

30、计算模块,用于将待补偿数字信号输入预训练的补偿模型,得到补偿结果;

31、补偿模块,用于利用补偿结果对待补偿数字信号做信号补偿,得到校准的数字信号;预训练的补偿模型通过多个理想数字信号以及与理想数字信号对应的实际数字信号联合训练得到。

32、第三方面,本发明提供了一种用于高速时域交织adc的神经网络校准系统,包括:处理器、存储介质和总线,存储介质存储有处理器可执行的机器可读指令,当用于高速时域交织adc的神经网络校准系统运行时,处理器与存储介质之间通过总线通信,处理器执行机器可读指令,以执行如上述第一方面方法的步骤。

33、第四方面,本发明提供了一种存储介质,存储介质上存储有计算机程序,计算机程序被处理器运行时执行如上述第一方面方法的步骤。

34、本发明提供了一种用于高速时域交织adc的神经网络校准方法及装置。其中,一种用于高速时域交织adc的神经网络校准方法,包括:获取待转换模拟信号;将待转换模拟信号输入第一高速时域交织adc,得到待补偿数字信号;将待补偿数字信号输入预训练的补偿模型,得到补偿结果;利用补偿结果对待补偿数字信号做信号补偿,得到校准的数字信号;预训练的补偿模型通过多个理想数字信号以及与理想数字信号对应的实际数字信号联合训练得到。在本发明中,通过预训练的补偿模型进行待补偿数字信号的校准。由于,整个过程不涉及硬件以及电路结构的改变,因此,在不改变电路的原有带宽性能的前提下实现了使用成本的降低;此外,本发明是基于软件进行的校准,无需对硬件校准部分进行繁琐的调试便可直接应用于目标电路,简单易行,降低了使用门槛。

35、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:1.一种用于高速时域交织adc的神经网络校准方法,其特征在于,包括:

2.根据权利要求1所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,

3.根据权利要求1所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,所述利用所述补偿结果对所述待补偿数字信号做信号补偿,得到校准的数字信号,包括:

4.根据权利要求1所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,所述预训练的补偿模型的训练过程包括:

5.根据权利要求4所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,所述将达到收敛条件的所述初始补偿模型作为所述预训练的补偿模型,包括:

6.根据权利要求4所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,所述预设损失函数为均方误差损失函数。

7.根据权利要求1所述的一种用于高速时域交织adc的神经网络校准方法,其特征在于,所述预训练的补偿模型,包括:

8.一种用于高速时域交织adc的神经网络校准装置,其特征在于,包括:获取模块、转换模块、计算模块以及补偿模块;

9.一种用于高速时域交织adc的神经网络校准系统,其特征在于,包括:处理器、存储介质和总线,所述存储介质存储有所述处理器可执行的机器可读指令,当所述用于高速时域交织adc的神经网络校准系统运行时,所述处理器与所述存储介质之间通过总线通信,所述处理器执行所述机器可读指令,以执行如权利要求1-7任一项所述方法的步骤。

10.一种存储介质,其特征在于,所述存储介质上存储有计算机程序,所述计算机程序被处理器运行时执行如权利要求1-7任一项所述方法的步骤。

技术总结本发明提供了一种用于高速时域交织ADC的神经网络校准方法及装置。其中,方法包括:获取待转换模拟信号;将待转换模拟信号输入第一高速时域交织ADC,得到待补偿数字信号;将待补偿数字信号输入预训练的补偿模型,得到补偿结果;利用补偿结果对待补偿数字信号做信号补偿,得到校准的数字信号;预训练的补偿模型通过多个理想数字信号以及与理想数字信号对应的实际数字信号联合训练得到。在本发明中,通过预训练的补偿模型进行信号的校准。由于,不涉及硬件以及电路结构的改变,因此,在不改变电路的原有带宽性能的同时实现了使用成本的降低;此外,本发明是基于软件进行的校准,无需进行调试便可应用于目标电路,简单易行,降低了使用门槛。技术研发人员:李登全,杨天齐,王隆盛,朱樟明,丁瑞雪受保护的技术使用者:西安电子科技大学技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/245051.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表