一种低行走误差的高速过零比较器及其控制方法

- 国知局

- 2024-08-02 15:19:57

本技术涉及集成电路,尤其涉及一种低行走误差的高速过零比较器及其控制方法。

背景技术:

1、目前基于激光雷达时刻鉴别方法中的比较器,现有方法仅仅是考虑了比较器的输入信号过驱动电压对传播延时散布的影响,忽略了输入信号摆率对传播延时散布的影响,然而在时刻鉴别中,输入信号摆率造成的影响比过驱动电压更明显。而有些方法虽然也同时考虑到摆率和过驱动电压的影响,但是当输入信号的摆率在很大范围内变化时,延时散布仍有几百ps。也存在采用的是把输入信号进行多级放大,直至饱和,以此来把摆率和过驱动电压均不同的信号的速度加快到一样,从而减小行走误差,但是其静态功耗较高。

2、综上,相关技术中存在的技术问题有待得到改善。

技术实现思路

1、本技术实施例的主要目的在于提出一种低行走误差的高速过零比较器及其控制方法,能够在消耗较小的静态功耗条件下,增强比较器对不同摆率和过驱动的输入信号的处理能力,降低在宽输入摆率和过驱动下的传播延时散布,从而降低高速过零比较器的过零点的漂移误差与回踢噪声。

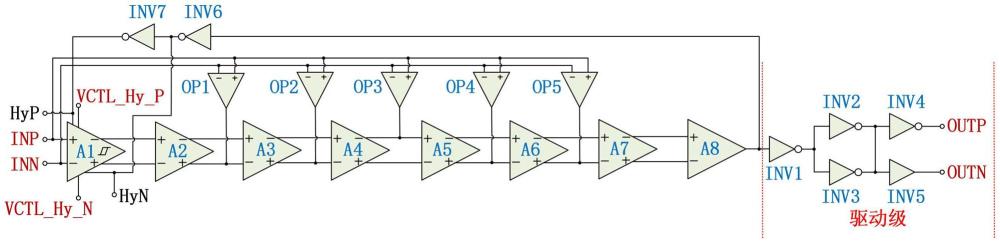

2、为实现上述目的,本技术实施例的一方面提出了一种低行走误差的高速过零比较器,所述高速过零比较器包括差分放大器模块、五管运算放大器模块、迟滞控制模块和驱动级电路,所述差分放大器模块的输出端与所述五管运算放大器模块的输出端连接于第一连接点,所述第一连接点分别与所述驱动级电路的输入端和所述迟滞控制模块的输入端连接,所述迟滞控制模块的输出端与所述差分放大器模块的输入端连接,其中:

3、所述差分放大器模块用于获取差分输入信号并进行放大与转换处理,输出单端信号;

4、所述五管运算放大器模块用于获取所述差分输入信号并进行放大处理,生成与所述差分输入信号的摆率相关的电流信号;

5、所述迟滞控制模块用于控制所述差分放大器模块的正反迟滞阈值;

6、所述驱动级电路用于根据所述单端信号与所述电流信号,进行输出驱动处理,输出含有相位信息的数字信号。

7、在一些实施例中,所述差分放大器模块包括迟滞控制全差分放大器、小增益高带宽全差分放大器模块、判决电路和差分输入单端输出放大器,所述迟滞控制全差分放大器的输出端与所述小增益高带宽全差分放大器模块的输入端连接,所述小增益高带宽全差分放大器模块的输出端与所述判决电路的输入端连接,所述判决电路的输出端与所述差分输入单端输出放大器的输入端连接,其中:

8、所述迟滞控制全差分放大器用于获取所述差分输入信号并进行放大处理,输出一级放大后的差分信号;

9、所述小增益高带宽全差分放大器模块包括第一小增益高带宽全差分放大器、第二小增益高带宽全差分放大器、第三小增益高带宽全差分放大器、第四小增益高带宽全差分放大器和第五小增益高带宽全差分放大器,所述小增益高带宽全差分放大器模块用于对所述一级放大后的差分信号进行逐级放大处理,输出六级放大后的差分信号;

10、所述判决电路用于对所述六级放大后的差分信号进行比较锁存处理,输出比较后的差分信号;

11、所述差分输入单端输出放大器用于对所述比较后的差分信号进行转换处理,输出所述单端信号。

12、在一些实施例中,所述迟滞控制全差分放大器包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第一电阻和第二电阻,其中,所述第一晶体管的栅极与所述迟滞控制模块连接,所述第一晶体管的源极、所述第二晶体管的源极、所述第七晶体管的源极、所述第八晶体管的源极与所述第一小增益高带宽全差分放大器连接并接高电平,所述第一晶体管的漏极、所述第二晶体管的漏极与所述第三晶体管的源极连接,所述第三晶体管的漏极、所述第三晶体管的栅极、所述第四晶体管的漏极与所述第一小增益高带宽全差分放大器连接,所述第七晶体管的漏极、所述第八晶体管的漏极与所述第六晶体管的源极连接,所述第六晶体管的栅极、所述第六晶体管的漏极、所述第五晶体管的漏极与所述第一小增益高带宽全差分放大器连接,所述第四晶体管的源极与所述第五晶体管的源极连接并接地,所述第四晶体管的栅极连接第一差分输入信号,所述第五晶体管的栅极连接第二差分输入信号,所述第二晶体管的栅极与所述第一电阻的第一端连接,所述第一电阻的第二端接地,所述第七晶体管的栅极与所述第二电阻的第一端连接,所述第二电阻的第二端接地。

13、在一些实施例中,所述第一小增益高带宽全差分放大器、第二小增益高带宽全差分放大器、第三小增益高带宽全差分放大器、第四小增益高带宽全差分放大器和第五小增益高带宽全差分放大器均具有相同的结构,所述第一小增益高带宽全差分放大器包括第九晶体管、第十晶体管、第十一晶体管和第十二晶体管,其中,所述第九晶体管的源极与所述第十二晶体管的源极连接,所述第九晶体管的栅极、所述第九晶体管的漏极与所述第十晶体管的漏极连接,所述第十二晶体管的栅极、所述第十二晶体管的漏极与所述第十一晶体管的漏极连接,所述第十晶体管的源极与所述第十一晶体管的源极连接。

14、在一些实施例中,所述判决电路包括第二十九晶体管、第三十晶体管、第三十一晶体管、第三十二晶体管、第三十三晶体管和第三十四晶体管,其中,所述第二十九晶体管的源极与所述第三十四晶体管的源极连接,所述第二十九晶体管的栅极与所述第五小增益高带宽全差分放大器连接,所述第三十四晶体管的栅极与所述第五小增益高带宽全差分放大器连接,所述第二十九晶体管的漏极、所述第三十二晶体管的栅极、所述第三十一晶体管的漏极、所述第三十晶体管的栅极、所述第三十晶体管的漏极与所述差分输入单端输出放大器连接,所述第三十四晶体管的漏极、所述第三十一晶体管的栅极、所述第三十二晶体管的漏极、所述第三十三晶体管的栅极、所述第三十三晶体管的漏极与所述差分输入单端输出放大器连接,所述第三十晶体管的源极、所述第三十一晶体管的源极、所述第三十二晶体管的源极和所述第三十三晶体管的源极连接。

15、在一些实施例中,所述差分输入单端输出放大器包括第三十五晶体管、第三十六晶体管、第三十七晶体管、第三十八晶体管、第三十九晶体管和第四十晶体管,其中,所述第三十七晶体管的源极分别与所述判决电路和所述驱动级电路连接,所述第三十七晶体管的栅极、所述第三十五晶体管的漏极、所述第三十六晶体管的漏极和所述第三十八晶体管的栅极连接,所述第三十七晶体管的漏极、所述第三十五晶体管的源极和所述第三十九晶体管的源极连接,所述第三十五晶体管的栅极、所述第三十六晶体管的栅极与所述判决电路连接,所述第三十九晶体管的栅极、所述第四十晶体管的栅极与所述判决电路连接,所述第三十九晶体管的漏极、所述第四十晶体管的漏极和所述驱动级电路连接,所述第三十六晶体管的源极、所述第四十晶体管的源极和所述第三十八晶体管的漏极连接,所述第三十八晶体管的源极接地。

16、在一些实施例中,所述五管运算放大器模块包括第一五管运算放大器、第二五管运算放大器、第三五管运算放大器、第四五管运算放大器和第五五管运算放大器,所述第一五管运算放大器、所述第二五管运算放大器、所述第三五管运算放大器、所述第四五管运算放大器和所述第五五管运算放大器依次连接,所述第一五管运算放大器、所述第二五管运算放大器、所述第三五管运算放大器、所述第四五管运算放大器和所述第五五管运算放大器具有相同的结构,所述第一五管运算放大器包括第五十五晶体管、第五十六晶体管、第五十七晶体管和第五十八晶体管,其中,所述第五十五晶体管的源极与所述第五十八晶体管的源极连接并接高电平,所述第五十五晶体管的栅极、所述第五十五晶体管的漏极和所述第五十六晶体管的漏极连接,所述第五十八晶体管的漏极、所述第五十七晶体管的漏极和所述第二五管运算放大器连接,所述第五十六晶体管的栅极连接所述第一差分输入信号,所述第五十七晶体管的栅极连接所述第二差分输入信号,所述第五十六晶体管的源极和所述第五十七晶体管的源极连接并接地。

17、在一些实施例中,所述迟滞控制模块包括第五十一晶体管、第五十二晶体管、第五十三晶体管和第五十四晶体管,所述第五十一晶体管的源极与所述第五十三晶体管的源极连接并接高电平,所述第五十一晶体管的漏极、所述第五十二晶体管的漏极与所述迟滞控制全差分放大器连接,所述第五十一晶体管的栅极、所述第五十二晶体管的栅极、所述第五十三晶体管的漏极、所述第五十四晶体管的漏极和所述迟滞控制全差分放大器连接,所述第五十二晶体管的源极与所述第五十四晶体管的源极连接并接地,所述第五十三晶体管的栅极、所述第五十四晶体管的栅极与所述差分输入单端输出放大器连接。

18、在一些实施例中,所述驱动级电路包括第一级驱动单元、第二级驱动单元、第三级驱动单元、第四级驱动单元和第五级驱动单元,所述第一级驱动单元分别与所述第二级驱动单元和所述第三级驱动单元连接,所述第二级驱动单元与所述第四级驱动单元连接,所述第三级驱动单元与所述第五级驱动单元连接,所述第一级驱动单元、所述第二级驱动单元、所述第三级驱动单元、所述第四级驱动单元和所述第五级驱动单元具有相同的结构,所述第一级驱动单元包括第四十一晶体管和第四十二晶体管,所述第四十一晶体管的栅极、所述第四十二晶体管的栅极与所述差分输入单端输出放大器连接,所述第四十一晶体管的源极分别与所述差分放大器模块和所述第二级驱动单元连接,所述第四十二晶体管的源极分别与所述差分放大器模块和所述第三级驱动单元连接,所述第四十一晶体管的漏极、所述第四十二晶体管的漏极、所述第二级驱动单元和所述第三级驱动单元连接。

19、为实现上述目的,本技术实施例的另一方面提出了一种低行走误差的高速过零比较器的控制方法,所述方法包括:

20、确定正反迟滞阈值;

21、基于所述正反迟滞阈值,获取差分输入信号并进行放大处理,生成电流信号;

22、对所述差分输入信号进行转换处理,输出单端信号;

23、根据所述单端信号与所述电流信号,进行输出驱动处理,输出含有相位信息的数字信号。

24、本技术实施例至少包括以下有益效果:本技术提供一种低行走误差的高速过零比较器及其控制方法,该方案包括差分放大器模块、五管运算放大器模块、迟滞控制模块和驱动级电路,差分放大器模块能够获得很高的开环增益带宽积,这样对于摆率和过驱动电压均不同的输入信号,比较器的响应速度基本上一样,从而减小了在轨到轨输入摆幅下的传播延时散布,进一步通过五管运算放大器模块,在当输入信号的斜率和过驱动都很大时,五管运算放大器的输出端会有很强的上拉能力,从而减慢了全差分放大器各个关键输出节点的放电速度,也就是将大摆率大过驱动的输入信号的传播延时略微增大了,而对于小摆率小过驱动的输入信号,将传播延时散布从300ps以上显著降低到100ps以内,最后基于驱动级电路用于提高比较器的输出端驱动能力以及迟滞控制模块分别控制比较器的正反迟滞阈值,能够在消耗较小的静态功耗条件下,增强比较器对不同摆率和过驱动的输入信号的处理能力,降低在宽输入摆率和过驱动下的传播延时散布,从而降低高速过零比较器的过零点的漂移误差与回踢噪声。

本文地址:https://www.jishuxx.com/zhuanli/20240801/245660.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表