一种低抖动占空比稳定时钟电路的制作方法

- 国知局

- 2024-08-02 15:25:38

本发明涉及集成电路,具体涉及一种低抖动占空比稳定时钟电路。

背景技术:

1、采样过程是所有模数转换器(analog-to-digital converter)的核心,采样过程本质上由一个采样开关和采样电容组成,如图1所示,采样开关在时钟控制作用下对信号进行采样和保持,采样过程类似采样时钟与模拟输入信号的调制,采样开关时钟抖动将会调制到采样信号中。采样抖动δtj将转化为采样误差2πfin×a×δtj,占空比误差δt也将转化为2πfin×a×δt,其中a为模拟输入信号的幅度。采样抖动δtj和占空比误差δt越大,引起的采样误差越大。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明提供一种低抖动占空比稳定时钟电路,以解决上述技术问题。

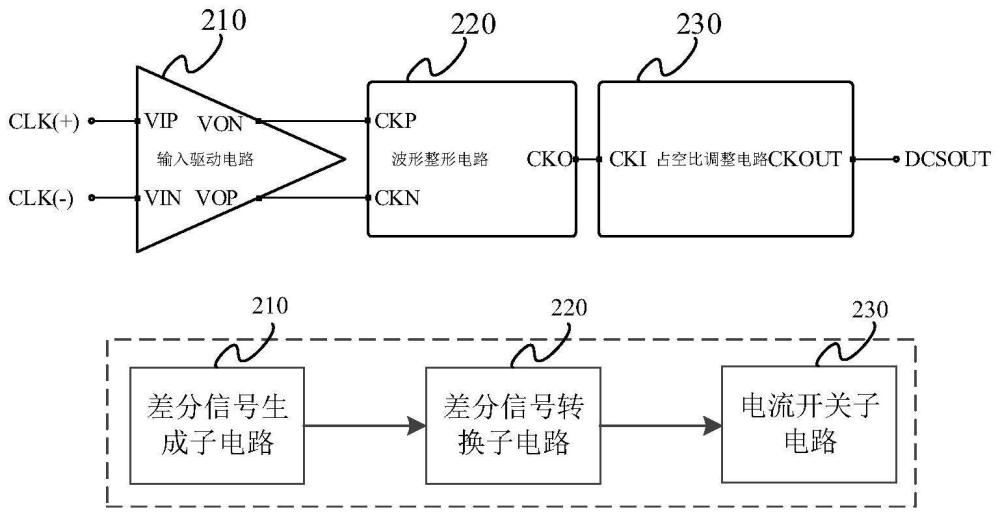

2、本发明提供的一种低抖动占空比稳定时钟电路,包括:

3、输入驱动电路,用于对输入的周期性的模拟电压信号进行放大,输出周期性的放大信号;

4、波形整形电路,用于将所述周期性放大信号转换成方波信号;

5、占空比调整电路,用于调整所述方波信号的占空比,以使所述方波信号的占空比为目标占空比。

6、于本发明一实施例中,所述输入驱动电路包括:

7、放大模块,用于对所述模拟电压信号进行逐级放大,输出周期性的放大信号;

8、反馈模块,用于对所述放大信号进行单极反馈。

9、于本发明一实施例中,所述放大模块包括多个串联设置的放大单元,所述放大单元均包括第一同相输入端、第一同相输出端、第一反相输入端和第一反相输出端;所述反馈模块包括第二同相输入端、第二反相输入端和第一输出端;

10、第一个放大单元的第一同相输入端接模拟电压信号的同相输入信号,第一反相输入端接模拟电压信号的反相输入信号;

11、第一个放大单元的第一同相输出端与第二个放大单元的第一反相输入端连接,第二个放大单元的第一同相输出端与第三个放大单元的第一反相输入端连接;

12、第二个放大单元的第一反相输出端与第二个放大单元的第一同相输入端连接,第二个放大单元的第一反相输出端与第三个放大单元的第一同相输入端连接;

13、第三个放大单元的第一同相输出端与反馈模块的第二反相输入端连接,第三个放大单元的第一反相输出端与反馈模块的第二同相输入端连接,反馈模块的输出端与第一个放大单元的第一同相输出端连接;所述第三个放大单元的第一同相输出端作为输入驱动电路的其中一个输出端,所述第三个放大单元的第一反相输出端作为输入驱动电路的另一个输出端。

14、于本发明一实施例中,所述放大单元包括:第一同相输入端、第一反相输入端、第一同相输出端、第一反相输出端、第一nmos管、第二nmos管、第一电阻和第二电阻;

15、所述第一nmos管的栅极与所述第一同相输入端连接,所述第一nmos管的源极接第一电流源的正极,所述第一nmos管的漏极与所述第一电阻的一端连接后与所述第一同相输出端连接,所述第一电阻的另一端接电源电压;所述第二nmos管的栅极与所述第一反相输入端连接,所述第二nmos管的源极接第一电流源的正极,第一电流源的负极接地,所述第二nmos管的漏极与所述第二电阻的一端连接后与所述第一反相输出端连接,所述第二电阻的另一端接电源电压。

16、于本发明一实施例中,所述反馈模块包括:第二同相输入端、第二反相输入端、第一输出端、第三nmos管和第四nmos管;

17、所述第三nmos管的栅极与所述第二同相输入端连接,与第三个放大单元的第一同相输出端连接,所述第三nmos管的源极接第二电流源的正极,所述第三nmos管的漏极与第一输出端连接;

18、所述第四nmos管的栅极与第二反相输入端连接,与第三个放大单元的第一反相输出端连接,所述第四nmos管的源极接第二电流源的正极,第二电流源的负极接地,所述第四nmos管的漏极接电源电压。

19、于本发明一实施例中,所述波形整形电路包括:第一电压输入端、第二电压输入端、第一时钟信号输出端、第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第五nmos管、第六nmos管、第七nmos管;

20、第五nmos管的栅极与第一电压输入端连接,与所述第三个放大单元的第一同相输出端连接,第五nmos管的源极接第三电流源的正极,第三电流源的负极接地;第六nmos管的栅极与第二电压输入端连接,与所述第三个放大单元的第一反相输出端连接,第六nmos管的源极接第三电流源的正极;第五nmos管的漏极分别与所述第一pmos管的漏极、第二pmos管的漏极连接,第六nmos管的漏极分别与第三pmos管的漏极、第四pmos管的漏极连接,第一pmos管的漏极与栅极连接,第二pmos管的栅极与第三pmos管的漏极连接,第三pmos管的栅极与第二pmos管的漏极连接,第四pmos管的漏极与栅极连接,第一pmos管的源极、第二pmos管的源极、第三pmos管的源极、第四pmos管的源极分别接电源电压;第六nmos管的栅极分别与第五pmos管的栅极、第七nmos管的栅极连接,第五nmos管的源极接电源电压,第七nmos管的源极接地,第五pmos管的漏极与第七nmos管的漏极连接后与第一时钟信号输出端连接。

21、于本发明一实施例中,所述占空比调节电路包括:时钟信号输入端、第二时钟信号输出端、第一非门g1、第一与非门、第二与非门、第二非门、第三非门、施密特触发门、第四非门、第三与非门、下降沿调整电路;

22、第一非门g1的输入端和第一与非门的第一输入端分别与时钟信号输入端连接,时钟信号输入端与所述时钟信号输出端连接;第一非门g1的输出端与第一与非门的第二输入端连接;第一与非门的输出端与第二与非门的第一输入端连接;第二与非门的第二输入端与第三与非门的输出端连接;第二与非门的输出端与第二时钟输出端连接,输出时钟信号;第二与非门的输出端分别与第三与非门的第一输入端、第二非门的输入端连接;第二非门的输出端与第三非门的输入端连接;第三非门的输出端与下降沿调整电路的输入端连接;下降沿调整电路的输出端与施密特触发门的输入端连接;施密特触发门的输出端与第四非门的输入端连接;第四非门的输出端与第三与非门的第二输入端连接。

23、于本发明一实施例中,所述施密特触发门包括第六pmos管、第七pmos管、第八pmos管、第八nmos管、第九nmos管、第十nmos管;

24、第六pmos管的源极接电源电压,第六pmos管的漏极与第七pmos管的源极连接,第七pmos管的漏极与第八nmos管的漏极连接,第八nmos管的源极与第九nmos管的漏极连接,第九nmos管的源极接地;第六pmos管的栅极、第七pmos管的栅极、第八nmos管的栅极、第九nmos管的栅极连接并作为施密特触发门的输入端;第六pmos管的漏极与第七pmos管的源极连接后与第八pmos管的源极连接,第八pmos管的漏极接地;第八nmos管的源极与第九nmos管的漏极连接后与第十nmos管的源极连接,第十nmos管的漏极接电源电压;第七pmos管的漏极与第八nmos管的漏极连接后分别与第八pmos管的栅极、第十mnos管的栅极连接作为成施密特触发门的输出端。

25、于本发明一实施例中,所述下降沿调整电路包括:

26、运放单元、第九pmos管、第十pmos管、第十一nmos管、第十二nmos管、第十三nmos管、第三电阻、第四电阻、第五电阻、第一电容、第二电容;

27、第三电阻的一端作为下降沿调整电路的输入端,另一端与运放单元的同相输入端连接,第一电容并联于运放单元的同相输入端与输出端之间;第四电阻的一端接电源电压,另一端与第五电阻的一端连接,第五电阻的另一端接地;第四电阻与第五电阻的公共端与运放单元的反相输入端连接,运放单元的输出端与第九pmos管的栅极连接,第九pmos管的源极与第十pmos管的源极接电源电压,第九pmos管的漏极与第十一nmos管的漏极连接,第十一nmos管的源极接地,第十一nmos管的漏极与栅极连接,第十pmos管的漏极与第十三nmos管的漏极连接,第十三nmos管的源极与第十二nmos管的漏极连接,第十二nmos管的源极接地,第十pmos管的栅极与第十三nmos管的栅极连接后与下降沿调整电路的输入端连接,第十pmos管的漏极与第十三nmos管的漏极连接后作为下降沿调整电路的输出端;第二电容的一端与输出端连接,另一端接地。

28、于本发明一实施例中,所述运放单元包括:第三同相输入端、第三反相输入端、第二输出端、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第十四nmos管、第十五nmos管、第十六nmos管、第十七nmos管、第十八nmos管、第十九nmos管;

29、第十四nmos管的栅极与第三同相输入端连接,接第三电阻的另一端,第十四nmos管的源极接第四电流源的正极,第四电流源的负极接地,第十四nmos管的漏极分别与第十一pmos管的漏极、第十三pmos管的源极连接,第十五nmos管的源极接第四电流源的正极,第十五nmos管的栅极与第三反相输入端连接,第十五nmos管的漏极分别与第十二pmos管的漏极、第十四pmos管的源极连接,第十一pmos管的源极、第十二pmos管的源极分别接电源电压,第十一pmos管的栅极与第十二pmos管的栅极连接并接第一偏置电压,第十三pmos管的栅极与第十四pmos管的栅极连接并接第二偏置电压,第十三pmmos管的漏极分别与第十七nmos管的漏极、第十六nmos管的栅极、第十八nmos管的栅极连接,第十七nmos管的源极与第十六nmos管的漏极连接;第十四pmos管的漏极与第十九nmos管的漏极连接后与第二输出端连接;第十九nmos管的源极与第十八nmos管的漏极连接,第十八nmos管的源极接地,第十七nmos管的栅极与第十九nmos管的栅极连接并接第三偏置电压,第十六nmos管的源极接地。

30、本发明的有益效果:本发明的一种低抖动占空比稳定时钟电路,包括:输入驱动电路,用于对输入的周期性的模拟电压信号进行放大,输出周期性的放大信号;波形整形电路,用于将所述周期性放大信号转换成方波信号;占空比调整电路,用于调整所述方波信号的占空比,以使所述方波信号的占空比为目标占空比,经通上述发明输出的时钟信号具有低低斗抖动和占空比稳定特点。

31、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

本文地址:https://www.jishuxx.com/zhuanli/20240801/246035.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表