一种多路电源上电掉电时序控制电路

- 国知局

- 2024-08-02 15:26:25

本发明涉及电路设计领域,具体涉及一种多路电源上电掉电时序控制电路。

背景技术:

1、在板级电路设计领域,诸如处理器、fpga、存储器等芯片,大多是多电源供电,往往含核心电压、io电压等,一般对上电和掉电时序有一定要求,控制上电时序一般通过专用芯片或通用电路设计实现。本设计发明主要是利用复位芯片和cpld和逻辑芯片配合,实现电源任意上电和掉电时序稳定控制。

2、现代电子系统越来越复杂,电源轨道也越来越多,为此,复杂系统一般通过专用单片机及其外围电路或通过比较器等模拟电路设计电路来实现上电或掉电时序的控制。但由于单片机等上电加载代码需要一定时间,其上电过程到代码稳定跑起来需要一定时间,这段时间往往为不稳定状态时间,给电源控制造成上电紊乱,其初始io状态取决于单片机上电默认状态,但电源模块使能电平为高或低取决于电源模块设计,因此这个设计带来一定麻烦,且单片机方案上电时间控制不够精确,模拟电路不适合于电源比较多的控制情况。

3、有鉴于此,本发明提供一种多路电源上电掉电时序控制电路。

技术实现思路

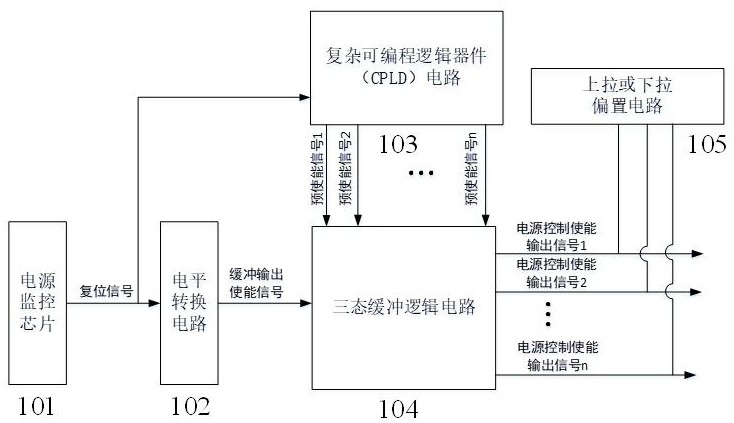

1、本发明的目的在于针对现有技术的不足,提供一种多路电源上电掉电时序控制电路,利用复位用的电源监控芯片、复杂可编程逻辑器件电路芯片和具有三态总线缓冲输出功能的三态缓冲逻辑电路配合使用,精确控制外部电源模块的上电及掉电,有效解决板级电路上电及掉电控制。

2、为了解决上述技术问题,采用如下技术方案:

3、一种多路电源上电掉电时序控制电路,包括:

4、电源监控芯片:用于产生上电或者掉电的复位信号。

5、电平转换电路:用于将所述电源监控芯片的复位信号逻辑反向,控制三态缓冲逻辑电路是否输出,以保障复位有效期间所述三态缓冲逻辑电路输出为高阻。

6、复杂可编程逻辑器件电路:用于编程精确控制各个预使能信号的时间顺序,所述预使能信号的时间顺序包括上电过程时序控制和掉电过程时序控制。

7、三态缓冲逻辑电路:用于将复杂可编程逻辑器件电路输出的预使能信号经过逻辑处理得到最终的电源控制使能输出信号,同时具备三态总线输出控制功能。

8、上拉或下拉偏置电路:用于保障在复位期间,所述电源控制使能输出信号处于高阻态,且确保正常运行情况下各电源控制信号都处于设定的固定状态。

9、在所述的技术方案基础之上再做进一步的改进的是,在上电或者掉电的复位信号有效期间内,

10、s1.通过所述电平转换电路的电平变换,关闭缓冲输出使能信号。

11、s2.然后所述三态缓冲逻辑电路处于高阻状态。

12、s3.接着所述电源控制使能输出信号由默认的上拉或下拉偏置电路决定。

13、s4.最后初次上电,所述复杂可编程逻辑器件电路进入程序加载,加载完成后,所述复杂可编程逻辑器件电路的程序检测到复位信号有效后,所述复杂可编程逻辑器件电路进入等待程序,并关闭所述预使能信号。

14、在所述的技术方案基础之上再做进一步的改进的是,检测到在上电或者掉电的复位信号无效期间:

15、s1.通过所述电平转换电路的电平变换,使能缓冲输出使能信号。

16、s2.所述三态缓冲逻辑电路处于缓冲输出状态。

17、s3.所述电源控制使能输出信号为由所述复杂可编程逻辑器件电路输出的预使能信号电平决定。

18、s4.所述复杂可编程逻辑器件电路的程序检测到复位信号无效后,所述复杂可编程逻辑器件电路进入延时计数程序,每路输出所述复杂可编程逻辑器件电路均有单独的延时程序,待设定的计数周期到达后,改变所述三态缓冲逻辑电路输出的预使能信号电平为使能电平。

19、在所述的技术方案基础之上再做进一步的改进的是,所述电源监控芯片为电源监控复位芯片或看门狗复位芯片,所述电源监控芯片包括复位芯片u3,所述复位芯片u3的管脚1连接所述电平转换电路和复杂可编程逻辑器件电路,所述复位芯片u3的管脚1通过电阻r3连接电压3.3v,所述复位芯片u3的管脚2连接接地,所述复位芯片u3的管脚5连接电压3.3v。

20、在所述的技术方案基础之上再做进一步的改进的是,所述电平转换电路包括三极管q1、电容c2、电阻r8和电阻r9,所述三极管q1的管脚1分别并联连接有电容c2、电阻r8和电阻r9,所述电容c2的另一端接地,所述电阻r8的另一端分别并联连接所述复位芯片u3的管脚1和复杂可编程逻辑器件电路,所述三极管q1的管脚2接地,所述三极管q1的管脚3分别并联连接有电阻r6和三态缓冲逻辑电路,所述电阻r6的另一端连接电压3.3v。

21、在所述的技术方案基础之上再做进一步的改进的是,所述电平转换电路可用专用反相器逻辑芯片替代。

22、在所述的技术方案基础之上再做进一步的改进的是,所述复杂可编程逻辑器件电路包括cpld芯片u1、晶振y1和电阻r1,所述cpld芯片u1的管脚43连接有电阻r1,所述电阻r1的另一端连接于所述晶振y1的管脚3,所述晶振y1的管脚2接地,所述晶振y1的管脚4连接电压3.3v,所述cpld芯片u1的管脚33分别连接所述复位芯片u3的管脚2和所述三极管q1的管脚1,所述cpld芯片u1的管脚4、管脚17和管脚25接地,所述cpld芯片u1的管脚29、管脚30、管脚31、管脚32、管脚37、管脚38、管脚39和管脚40连接所述三态缓冲逻辑电路。

23、在所述的技术方案基础之上再做进一步的改进的是,所述复杂可编程逻辑器件电路可由fpga芯片替代。

24、在所述的技术方案基础之上再做进一步的改进的是,所述三态缓冲逻辑电路包括缓冲逻辑芯片u2、缓冲逻辑芯片u4、电容c1和电容c3。

25、所述缓冲逻辑芯片u2的管脚2连接所述cpld芯片u1的管脚29,所述缓冲逻辑芯片u2的管脚5连接所述cpld芯片u1的管脚30,所述缓冲逻辑芯片u2的管脚9连接所述cpld芯片u1的管脚31,所述缓冲逻辑芯片u2的管脚12连接所述cpld芯片u1的管脚32。

26、所述缓冲逻辑芯片u2的管脚1、管脚4、管脚10、管脚13连接所述三极管q1的管脚3。

27、所述缓冲逻辑芯片u2的管脚14分别连接电压3.3v和电容c1,所述电容c1的另一端接地。

28、所述缓冲逻辑芯片u2的管脚7接地。

29、所述缓冲逻辑芯片u2的管脚3、管脚6、管脚8、管脚11连接所述上拉或下拉偏置电路。

30、所述缓冲逻辑芯片u4的管脚2连接所述cpld芯片u1的管脚37,所述缓冲逻辑芯片u4的管脚5连接所述cpld芯片u1的管脚38,所述缓冲逻辑芯片u4的管脚9连接所述cpld芯片u1的管脚39,所述缓冲逻辑芯片u4的管脚12连接所述cpld芯片u1的管脚49。

31、所述缓冲逻辑芯片u4的管脚1、管脚4、管脚10、管脚13连接所述三极管q1的管脚3,

32、所述缓冲逻辑芯片u4的管脚14分别连接电压3.3v和电容c3,所述电容c3的另一端接地;

33、所述缓冲逻辑芯片u4的管脚7接地。

34、所述缓冲逻辑芯片u4的管脚3、管脚6、管脚8、管脚11连接所述上拉或下拉偏置电路。

35、在所述的技术方案基础之上再做进一步的改进的是,所述上拉或下拉偏置电路包括电阻r2、r3、r4、r5、r10、r11、r12和r13。

36、所述电阻r2的一端连接所述缓冲逻辑芯片u2的管脚3,所述电阻r2的另一端接地。

37、所述电阻r3的一端连接所述缓冲逻辑芯片u2的管脚6,所述电阻r3的另一端接地。

38、所述电阻r4的一端连接所述缓冲逻辑芯片u2的管脚8,所述电阻r4的另一端接地。

39、所述电阻r5的一端连接所述缓冲逻辑芯片u2的管脚11,所述电阻r5的另一端接地。

40、所述电阻r10的一端连接所述缓冲逻辑芯片u4的管脚3,所述电阻r10的另一端接地。

41、所述电阻r11的一端连接所述缓冲逻辑芯片u4的管脚6,所述电阻r11的另一端接地。

42、所述电阻r12的一端连接所述缓冲逻辑芯片u4的管脚8,所述电阻r12的另一端接地。

43、所述电阻r13的一端连接所述缓冲逻辑芯片u4的管脚11,所述电阻r13的另一端接地。

44、由于采用上述技术方案,具有以下有益效果:

45、本发明通过提供一种多路电源上电掉电时序控制电路,本发明结构精简,原理简单清晰,成本较低,便于大规模生产应用,易于普及推广。在上电期间通过逻辑控制使得旁路复杂可编程逻辑器件电路(cpld)的输出控制,在复位后(一般复位时间可保障可编程逻辑器件电路(cpld)加载初始化完成),按照可编程逻辑器件电路(cpld)时序控制进行板级电源模块的上电时序控制。由于具有通道可扩展性及时序时间通过编程调节,可方便实现板级电路的多电源轨道上电及掉电的时序控制,保障电路安全。

46、本发明利用复杂可编程逻辑器件电路(cpld)、复位的电源监控芯片、三态的三态缓冲逻辑电路和上拉/下拉偏置电路配合,保障复杂可编程逻辑器件电路(cpld)加载期间输出的电源使能信号为确定的电平状态。

47、本发明利用三态使能避开可编程逻辑器件电路(cpld)或fpga直接输出信号在加载期间的电平不可控。

本文地址:https://www.jishuxx.com/zhuanli/20240801/246108.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种自校准系统的制作方法

下一篇

返回列表