一种高速动态比较器

- 国知局

- 2024-08-02 15:31:24

本技术涉及模拟电路信号处理,特别涉及一种高速动态比较器。

背景技术:

1、动态比较器是用于通信应用的高速、高分辨率模数转换器(adc)的核心。adc的速度和精度取决于比较器模块的鲁棒性。动态比较器由于没有静态功耗、输入参考偏置小、比较时间短等特点而被广泛运用。

2、常用的动态比较器包括单尾(st)动态比较器和双尾(dt)动态比较器。大多数动态比较器使用一对交叉耦合逆变器作为锁存级,提供强正反馈以加速比较。传统的dt动态比较器由具有独立的尾晶体管的输入级和锁存级组成。两个独立的尾电流使设计者能够在速度、失调和功耗之间权衡。这种拓扑结构具有较少的晶体管堆叠,适合低压应用。由于输入晶体管和输出节点之间的隔离,它还降低了回踢噪声。

3、由于晶体管的堆叠,st动态比较器需要足够的电压余量。这使得在低压深亚微米下设计它们具有挑战性。此外,由于再生锁存器和差分输入级之间的隔离性较差,st动态比较器在输入端会承受较大的回踢噪声。传统dt比较器缓解了st比较器的不足。然而,目前大多数动态比较器只能在一个狭窄的输入共模电压范围内实现高速,其性能在共模电压的极值处会下降。

技术实现思路

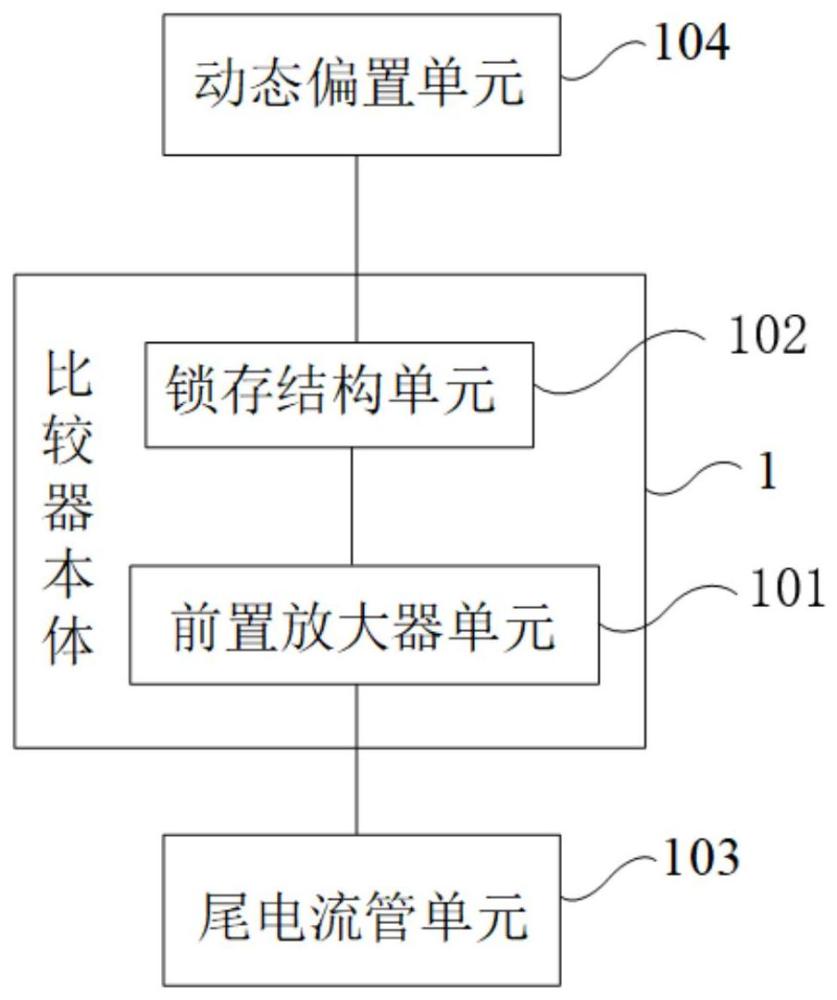

1、本技术提供一种高速动态比较器,在锁存结构单元尾端动态偏置单元,能够暂时提高电路的有效电源电压,加快了比较速度;并在前置放大器单元尾端增加电流管单元,降低比较器的功耗。

2、为解决上述技术问题,本技术实施例提供一种高速动态比较器,包括:比较器本体,比较器本体包括前置放大器单元和锁存结构单元;比较器本体还包括尾电流管单元和动态偏置单元;尾电流管单元设置在前置放大器单元的尾端,动态偏置单元设置在锁存结构单元的尾端;动态偏置单元包括第一mos管、第二mos管和第一电容;第一mos管的漏极与锁存结构单元连接,第一mos管的栅极与时钟信号clkb连接,第一mos管的源极分别与第二mos管的漏极、时钟信号clk连接;第一电容设置在第一mos管的源极和时钟信号clk之间;第二mos管的源极与电源电压vdd连接,第二mos管的栅极与时钟信号clk连接;尾电流管单元包括第三mos管、第四mos管和第二电容;第三mos管的漏极与前置放大器单元连接,第三mos管的栅极与时钟信号clk连接,第三mos管的源极分别与第四mos管的漏极、时钟信号clkb连接;第二电容设置在第三mos管的源极和时钟信号clkb之间;第四mos管的栅极与时钟信号clkb连接,第四mos管的源极接地。

3、在一些示例性实施例中,第一mos管和第二mos管均为pmos管。

4、在一些示例性实施例中,第三mos管和第四mos管均为nmos管。

5、在一些示例性实施例中,前置放大器单元包括尾开关单元、预放大输入单元、预放大复位单元、通断单元、输出节点fn和输出节点fp;尾开关单元包括偏置管,偏置管为nmos管,偏置管的栅极与时钟信号clk连接,偏置管的漏极与预放大复位单元连接,偏置管的源极接地。

6、在一些示例性实施例中,预放大输入单元包括第一输入晶体管和第二输入晶体管,第一输入晶体管和第二输入晶体管均为nmos管,第一输入晶体管的栅极与通断单元连接,第一输入晶体管的漏极与输出节点fp连接,第一输入晶体管的源极与第一输入信号vin连接;第二输入晶体管的栅极与通断单元连接,第二输入晶体管的漏极与输出节点fn连接,第二输入晶体管的源极与第二输入信号vip连接。

7、在一些示例性实施例中,通断单元包括第一通断元件和第二通断元件,第一通断元件和第二通断元件均为nmos管;第一通断元件的栅极与输出节点fn连接,第一通断元件的源极与第三mos管的漏极连接,第一通断元件的漏极与第一输入晶体管的源极连接;第二通断元件的栅极与输出节点fp连接,第二通断元件的源极与第三mos管的漏极连接,第二通断元件的漏极与第二输入晶体管的源极连接。

8、在一些示例性实施例中,预放大复位单元包括第三通断元件和第四通断元件,第三通断元件和第四通断元件均为pmos管;第三通断元件的栅极与时钟信号clk连接,第三通断元件的源极与电源电压vdd连接,第三通断元件的漏极与输出节点fp连接;第四通断元件的栅极与时钟信号clk连接,第四通断元件的源极与电源电压vdd连接,第四通断元件的漏极与输出节点fn连接。

9、在一些示例性实施例中,锁存结构单元与前置放大器单元的输出节点fn和输出节点fp连接,用于锁存数据,并输出第一输出信号voutn和第二输出信号voutp。

10、在一些示例性实施例中,锁存结构单元包括锁存输入单元、交叉耦合锁存单元、锁存复位单元和正反馈单元;锁存输入单元输入端连接预放大输入单元的输出端,并连接交叉耦合锁存单元和正反馈单元;预放大输入单元用于在复位阶段使预放大复位单元的输出节点fn拉高至电源电压vdd,或将输出节点fp拉高到电源电压vdd;交叉耦合锁存单元连接锁存输入单元和锁存复位单元,并形成比较器本体的输出端,输出第一输出信号voutn和第二输出信号voutp;所述交叉耦合锁存单元用于在比较阶段加快放电速度,而在锁存阶段锁存数据。

11、在一些示例性实施例中,锁存复位单元输入时钟信号clk,并连接交叉耦合锁存单元;锁存复位单元用于在复位阶段将比较器本体的输出拉到电源电压vdd;正反馈单元连接锁存输入单元和交叉耦合锁存单元;正反馈单元用于在比较阶段导通,并使得交叉耦合锁存单元在比较阶段增加一条放电支路。

12、本技术提供的技术方案至少具有以下优点:

13、为解决上述技术问题,本技术实施例提供一种高速动态比较器,包括:比较器本体,比较器本体包括前置放大器单元和锁存结构单元;比较器本体还包括尾电流管单元和动态偏置单元;尾电流管单元设置在前置放大器单元的尾端,动态偏置单元设置在锁存结构单元的尾端;动态偏置单元包括第一mos管、第二mos管和第一电容;第一mos管的漏极与锁存结构单元连接,第一mos管的栅极与时钟信号clkb连接,第一mos管的源极分别与第二mos管的漏极、时钟信号clk连接;第一电容设置在第一mos管的源极和时钟信号clk之间;第二mos管的源极与电源电压vdd连接,第二mos管的栅极与时钟信号clk连接;尾电流管单元包括第三mos管、第四mos管和第二电容;第三mos管的漏极与前置放大器单元连接,第三mos管的栅极与时钟信号clk连接,第三mos管的源极分别与第四mos管的漏极、时钟信号clkb连接;第二电容设置在第三mos管的源极和时钟信号clkb之间;第四mos管的栅极与时钟信号clkb连接,第四mos管的源极接地。

14、本技术提供的高速动态比较器,在锁存级增加了一种基于电荷泵的动态偏置单元,可以暂时提高电路的有效电源电压,加快了比较速度。并在前置放大器单元尾端增加电流管单元,即在前置放大器的尾部电荷泵增加了尾电流管的过驱动电压,导致前置放大器的共模漏极电流增加,从而增加了输出节点寄生电容的放电速率,提高了比较速度。通过前置放大器的尾电容和输入管下方增加的一对开关管可以使输出节点的寄生电容放电不完全,降低了功耗。

本文地址:https://www.jishuxx.com/zhuanli/20240801/246562.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表